AFYON KOCATEPE ÜNĠVERSĠTESĠ

MÜHENDĠSLĠK FAKÜLTESĠ

ELEKTRĠK MÜHENDĠSLĠĞĠ BÖLÜMÜ

2017-2018 Eğitim Öğretim Yılı Güz Dönemi

Sayısal Elektronik Laboratuvarı Dersi

Tüm Deneyler Kitapçığı

LABORATUVARDA UYULACAK KURALLAR

Deneye gelmeden önce, deneyle ilgili teorik bilgi araĢtırılacak ve laboratuvara gerekli

bilgiler öğrenilerek gelinecektir.

Deneyler saatinde baĢlayacak, geç kalan öğrenciler deneye alınmayacaktır.

Laboratuvardaki görevlilerin tüm uyarılarına ve temel iĢ sağlığı ve güvenliği kurallarına

harfiyen uyulacaktır.

Deney için izin verilen cihazlar haricinde laboratuvarda hiçbir cihaz kullanılmayacaktır.

Deneylerin belirlenen süre içerisinde tamamlanması gerekmektedir. Verilen süre içerisinde

tamamlanamayan deney geçersiz sayılacaktır.

Deney bittikten sonra deney masa ve sandalyeleri düzenli olarak bırakılacaktır.

Laboratuvara ait malzeme ve donanım laboratuvar dıĢına çıkarılmayacaktır.

Deneylerle ilgili soru ve sorunlar görevli Öğretim Elemanı’ na aktarılacaktır.

Kural dıĢı davranıĢlardan doğacak maddi/manevi tüm zararlardan öğrenci sorumlu olacaktır.

Kurallara uymayan öğrencinin deneyine son verilecek, laboratuvardan çıkarılacak ve

öğrenci hakkında disiplin yönetmeliği uygulanacaktır.

Bir dönem içinde toplam üç deneye girmeyen öğrenci final sınavına giremeyecektir.

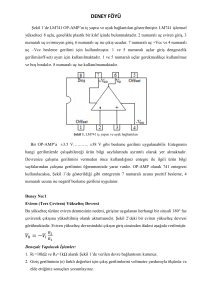

DENEY NO :1.1.

DENEYĠN ADI: Op-Amp Deneyleri 1 (Eviren Tip Yükselteç Devresi)

DENEYĠN AMACI: Eviren tip yükselteç devresi çalıĢmasının incelenmesi ve Op-Amplı

yükselteç tasarımda gerekli bilgilerin öğrenilmesi.

TEORĠK BĠLGĠ

Bilindiği gibi opampların açık çevrim kazancı çok yüksektir. Bu durum kullanıcıya her

zaman avantaj sağlamaz. Çünkü opamp’ın kazanç kontrol altında değildir. Yükselteç

tasarımında elemanın kazancı kullanıcı tarafından kontrol edilmelidir. Opamp kazancının

kontrol edilebileceği iki temel tip yükselteç devresi vardır. Bunlar; eviren (inverting) ve

evirmeyen (noninverting) yükselteçlerdir. Op-amp’lar yüksek kazançlı yükselteçlerdir.

GiriĢlerine uygulanan sinyali çıkıĢlarında yükselterek verirler. Eğer giriĢ sinyali op-amp’ın

eksi ucuna verilirse giriĢ ile çıkıĢ arasında 180 derece faz farkı oluĢur. Bu devreye eviren

yükselteç devresi denir.

Op-amp'ların özelliklerinden biri de (+) ve (-) giriĢ uçlarında potansiyel fark 0 volttur.Çünkü

op-amp'ların giriĢ empedansları çok yüksek olduğundan (+) ve (-) giriĢ uçlarından akan akım

pratikte nano amper seviyesindedir.Ġdeal bir oğ-amp'ta (+)ve (-) giriĢ uçlarından akım

akmadığı akmadığı kabul edilirse (+) ve (-) giriĢ uçlarındaki voltaj farkı 0 olur.

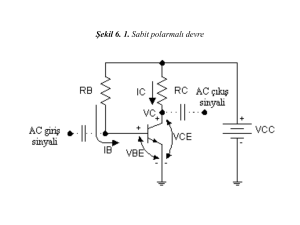

DENEYĠN BAĞLANTI ġEMASI

ġekil 1. Eviren tip yükselteç devresi (DC çalıĢma durumu).

ġekil 2. Eviren tip yükselteç devresi (AC çalıĢma durumu)

DENEYĠN YAPILIġI

1.ġekil 1’de verilen bağlantı Ģemasındaki devreyi kurunuz. ÇıkıĢ gerilimini ölçmek için deney

seti üzerindeki analog voltmetreyi ve giriĢ gerilimi için dijital avometreyi kullanınız.

2. Devredeki potansiyometrenin üç farklı konumu için giriĢ ve çıkıĢ gerilimlerinin değerlerini

ölçünüz.

3. Deney sonuçlarınızı öğretim elemanına onaylatın ve deneyi sonlandırın.

4. ġekil 2’de verilen bağlantı Ģemasındaki devreyi kurunuz. Devrede gösterilen noktalara

Osiloskop kanallarını uygun biçimde bağlayınız.

5. Sinyal jeneratörünü istenilen frekansa ayarlayın ve devreye uygulayın.

6. GiriĢ sinyalinin genliğini değiĢtirerek çıkıĢ sinyalini gözlemleyin dalga Ģeklini grafik

alanına çiziniz.

DENEYDE ALINAN SONUÇLARI

Potansiyometre Pozisyonu

1.Pozisyon

2.Pozisyon

3.Pozisyon

VgiriĢ

VçıkıĢ

Volt/Div=........V

CH1

Volt/Div=...........V

CH2

Prob X=..........

Time/Div=............ms

Prob X=.............

SORULAR

1. Eviren tip Op-Amp deney Ģemasında verilen devrede çıkıĢ gerilimi Vout = K x Vin Ģeklinde

ifade edilir. Burada K kazanç değerini belirleyen nedir araĢtırınız. Bulduğunuz kazanca göre

çıkıĢ geriliminin değerini hesaplayınız ve yaptığınız ölçümlerle karĢılaĢtırınız.

2. 741 Op-Amp devesine ait bir veri sayfası elde edin ve inceleyip gerekli parametreleri

raporunuza ekleyin.

DENEY NO

:1.2.

DENEYĠN ADI

: Op-Amp Deneyleri 2 (Evirmeyen Tip Yükselteç Devresi)

DENEYĠN AMACI :. Evirmeyen tip yükselteç devresi çalıĢmasının incelenmesi ve OpAmplı yükselteç tasarımda gerekli bilgilerin öğrenilmesi.

TEORĠK BĠLGĠ :

Opampların temel uygulamalarından bir diğeri ise evirmeyen yükselteç devresidir. Bu

devrede yükseltilecek iĢaret opamp’ın evirmeyen giriĢine uygulanmaktadır. Evirmeyen

yükselteç devresinde giriĢ iĢareti ile çıkıĢ iĢareti aynı fazdadır. Yani giriĢ ile çıkıĢ iĢareti

arasında faz farkı yoktur.

Evirmeyen yükselteç devresinin en önemli özelliklerinden birisi çok yüksek bir giriĢ direncine

sahip olmasıdır. Eviren bir yükselteç devresinde giriĢ direnci, devrede kullanılan R1 direncine

bağlıdır ve değeri birkaç KΩ civarındadır. Evirmeyen yükselteç devresinde ise giriĢ direnci

opamp’ın giriĢ direncine eĢittir. Bu değer ise yüzlerce mega ohm civarındadır.

DENEY BAĞLANTI ġEMASI

ġekil 1. Evirmeyen tip yükselteç devresi (DC çalıĢma durumu )

ġekil 2. Evirmeyen tip yükselteç devresi (AC çalıĢma durumu )

DENEYĠN YAPILIġI

1. ġekil 1’de verilen bağlantı Ģemasındaki devreyi kurunuz. ÇıkıĢ gerilimini ölçmek için

deney seti üzerindeki analog voltmetreyi ve giriĢ gerilimi için dijital avometreyi kullanınız.

2. Devredeki potansiyometrenin üç farklı konumu için giriĢ ve çıkıĢ gerilimlerinin değerlerini

ölçünüz.

3. Deney sonuçlarınızı öğretim elemanına onaylatın ve deneyi sonlandırın.

4. ġekil 2’de verilen bağlantı Ģemasındaki devreyi kurunuz. Devrede gösterilen noktalara

Osiloskop kanallarını uygun biçimde bağlayınız.

5. Sinyal jeneratörünü istenilen frekansa ayarlayın ve devreye uygulayın.

6. GiriĢ sinyalinin genliğini değiĢtirerek çıkıĢ sinyalini gözlemleyin dalga Ģeklini grafik

alanına çiziniz.

DENEYDE ALINAN SONUÇLAR

Potansiyometre Pozisyonu

1.Pozisyon

2.Pozisyon

3.Pozisyon

Vin

Volt/Div=........V

CH1

Volt/Div=...........V

CH2

Prob X=..........

Vout

Time/Div=............ms

Prob X=.............

SORULAR

V K Vin

1. Uyguladığınız devre için out

Ģeklinde verildiğine göre K kazanç değerini

belirleyip çıkıĢ geriliminin değerini hesaplayınız ve yaptığınız ölçümlerle karĢılaĢtırınız.

DENEY NO

: 2.1.

DENEYĠN ADI: Op-Amp Deneyleri 3 (Ġntegral Alıcı Devre)

DENEYĠN AMACI: Ġntegral fonksiyonunu gerçekleĢtiren yükselteç devresinin çalıĢmasını

incelemek.

TEORĠK BĠLGĠ

Integratör devre, giriĢi uygulanan sinyalin integral alarak çıkıĢa aktarır. Matematiksel

anlamda integral, bir eğrinin altında kalan alana karĢı gelir. Integratör devrenin giriĢine kare

dalga uygulandığını devrenin çıkıĢından üçgen dalga elde edilir. Çünkü, kare dalganın

integrali üçgen dalgadır. GiriĢ palorma akımlarının eĢit olmayıĢından dolayı meydana

gelebilecek ofset gerilimini ve bu gerilimin etkilerini gidermek amacıyla op-amp 'ın faz

çevirmeyen (+) giriĢiyle Ģase arasına R gibi bir direnç bağlanır.

DENEYĠN ġEKLĠ

ġekil 1. Ġntegral alıcı devre bağlantı Ģeması.

DENEYĠN YAPILIġI

1.ġekil 1’de verilen bağlantı Ģemasındaki devreyi kurunuz.

2. GiriĢe sırası ile kare, üçgen ve sinüs biçimli sinyal uygulayın.

3. Uyguladığınız her bir sinyal için giriĢ ve çıkıĢ sinyallerinin dalga Ģekillerini çiziniz.

4. Deney sonuçlarınızı öğretim elemanına onaylatın ve deneyi sonlandırın.

DENEYDE ALINAN SONUÇLAR

Kare Dalga GiriĢ için ;

Volt/Div=........V

CH1

Volt/Div=...........V

CH2

Prob X=..........

Time/Div=............ms

Prob X=.............

Üçgen Dalga GiriĢ için ;

Volt/Div=........V

CH1

Volt/Div=...........V

CH2

Prob X=..........

Sinüs Dalga GiriĢ için ;

Time/Div=............ms

Prob X=.............

Volt/Div=........V

CH1

Volt/Div=...........V

CH2

Prob X=..........

Time/Div=............ms

Prob X=.............

SORULAR

1. Ġntegral alıcı devre kullanım alanlarını araĢtırıp bilgi verin.

2. Devrenin giriĢ çıkıĢ fonksiyonunu devre analizi bilgilerinizden yararlanarak bulunuz

DENEY NO

:2.2.

DENEYĠN ADI

: Op-Amp Deneyleri 4 (Türev Alıcı Devre)

DENEYĠN AMACI :. Ġntegral fonksiyonunu gerçekleĢtiren yükselteç devresinin çalıĢmasını

incelemek.

TEORĠK BĠLGĠ :

Türev alıcı devresi, genel olarak bir eviren yükselteç özelliğindedir. Fark olarak giriĢte R1

direnci yerine C kondansatörü bulunmaktadır. Genel bir türev alıcı devresi Ģekil-2.16’da

verilmiĢtir. Türev alıcı, giriĢinden uygulanan iĢaretin türevini alarak çıkıĢa aktaran bir

devredir. GiriĢte kullanılan kondansatör, AC iĢaretleri geçiren fakat DC iĢaretleri geçirmeden

üzerinde bloke eden bir devre elemanıdır. Dolayısı ile dc iĢaretler için türev alma söz konusu

değildir. Gerçekte dc iĢaretler için türev alıcı çıkıĢı Vo=0’dır. Türev alıcı giriĢine mutlaka

sinüzoidal iĢaret uygulanması söz konusu değildir. Frekans barındıran veya genliği zamana

bağlı olarak değiĢen bir iĢaretin uygulanması yeterlidir.

DENEY BAĞLANTI ġEMASI

ġekil . Türev alıcı devre bağlantı Ģeması

DENEYĠN YAPILIġI

1. ġekil 1’de verilen bağlantı Ģemasındaki devreyi kurunuz.

2. GiriĢe sırası ile kare üçgen ve sinüs biçimli sinyal uygulayın.

3. Uyguladığınız her bir sinyal için giriĢ ve çıkıĢ sinyallerinin dalga Ģekillerini çiziniz.

4. Deney sonuçlarınızı öğretim elemanına onaylatın ve deneyi sonlandırın.

DENEYDE ALINAN SONUÇLAR

Kare Dalga GiriĢ için ;

Volt/Div=........V

CH1

Volt/Div=...........V

CH2

Prob X=..........

Time/Div=............ms

Prob X=.............

Üçgen Dalga GiriĢ için ;

Volt/Div=........V

CH1

Volt/Div=...........V

CH2

Prob X=..........

Time/Div=............ms

Prob X=.............

Sinüs Dalga GiriĢ için ;

Volt/Div=........V

CH1

Volt/Div=...........V

CH2

Prob X=..........

Time/Div=............ms

Prob X=.............

SORULAR

1. Türev alıcı devrenin kullanım alanlarını araĢtırıp bilgi verin.

2. Devrenin giriĢ çıkıĢ fonksiyonunu devre analizi bilgilerinizden yararlanarak bulunuz.

DENEY 3- Temel Lojik Fonksiyonlar

Amaç: Temel lojik fonksiyonları öğrenmek(VE-AND, VEYA-OR, DEĞĠL-NOT, VEDEĞĠLNAND, VEYADEĞĠL-NOR). Bu fonksiyonların doğruluk tabloları, lojik diyagramlar ve

Boolean kuralları ile gösterimini öğrenmek.

Deneyin YapılıĢı:

- Deney bağlantı Ģemasında verilen devreleri uygun elemanlarla kurunuz. (Entegre

devrelerinin besleme ayakları şemaların yanındaki entegre bilgileri kısmında verilmiştir.)

- Doğruluk tablosunda verilen giriĢ lojik seviyelerini verilen anahtarları kullanarak devreye

uygulayın ve devrenin çıkıĢ lojik seviyelerini tabloya aktarınız.

Deney Bağlantı ġeması:

Bacak 1

0

0

+5

+5

Bacak 2

0

+5

0

+5

ġekil 1. VEYA (OR) kapısı deney bağlantı Ģeması ve doğruluk tablosu.

Bacak 1

0

+5

Bacak 2

ġekil 2. DEĞĠL (NOT) kapısı deney bağlantı Ģeması ve doğruluk tablosu.

Bacak 3

7432

Bacak 1 Bacak 2

0

0

0

+5

+5

0

+5

+5

7404

Bacak 2

ġekil 3. VEYA+DEĞĠL (OR+NOT) kapısı deney bağlantı Ģeması ve doğruluk tablosu.

Bacak 3

0

0

+5

+5

Bacak 2

0

+5

0

+5

Bacak 1

ġekil 4. VEYADEĞĠL (NOR) kapısı deney bağlantı Ģeması ve doğruluk tablosu.

Bacak 1

0

0

+5

+5

Bacak 2

0

+5

0

+5

ġekil 5. 2 GiriĢli VEDEĞĠL (NAND) kapısı deney bağlantı Ģeması ve doğruluk tablosu.

Bacak 3

Bacak 1

0

+5

+5

+5

+5

Bacak 2

0

0

+5

+5

+5

Bacak 3

0

0

0

+5

+5

Bacak 4

0

0

0

0

+5

Bacak 6

ġekil 6. 4 GiriĢli VEDEĞĠL (NAND) kapısı deney bağlantı Ģeması ve doğruluk tablosu.

ġekil 7. 7451entegre devresi deney bağlantı Ģeması ve doğruluk tablosu.

2A

0

+5

+5

+5

+5

2B

0

0

+5

+5

+5

2C

0

0

0

+5

+5

2D

0

0

0

0

+5

2Y

Raporda Ġstenenler:

- Deney bağlantı Ģemalarını rapor defterinize çiziniz.

- Doğruluk tablolarını oluĢturunuz. (Tablolarda 0 ve 1 kullanınız.)

- Ölçüm sonuçlarını kaydediniz.

- AĢağıdaki soruları rapor defterinize cevaplayınız.

Sorular:

1. Yukarıdaki devrelerde kullanılan entegre devreler için veri sayfalarından yararlanarak

bacak bağlantılarını çıkarınız.

2. Yine veri sayfalarından faydalanarak entegrelere ait akım gerilim sınırlarını yazınız (ÇıkıĢ

akım sınırı, giriĢ gerilimi değerleri, besleme gerilimi vb…).

3. AĢağıdaki devre için verilen doğruluk tablosunu doldurunuz.

A

0

0

1

1

B

0

1

0

1

A’

B’

K

L

Y

DENEY 3- Temel Lojik Fonksiyonlar

Öğrencinin Adı Soyadı:

Deney Uygulama Tarihi:

Öğretim Elemanı:

Numarası:

Rapor Teslim Tarihi:

Onay:

DENEY 4- Boolean Kuralları ve Lojik Denklemlerin SadeleĢtirilmesi

Amaç: Boolean kuralları ile lojik denklemlerin gösterimi ve sadeleĢtirilme yöntemlerini

öğrenmek.

Deneyin YapılıĢı:

- Deney bağlantı Ģemasında verilen devreleri uygun elemanlarla kurunuz. (Entegre

devrelerinin besleme ayakları şemaların yanındaki entegre bilgileri kısmında verilmiştir.)

- Doğruluk tablosunda verilen giriĢ lojik seviyelerini verilen anahtarları kullanarak devreye

uygulayın ve devrenin çıkıĢ lojik seviyelerini tabloya aktarınız.

- Devrede Osiloskop kullanılması gerekiyorsa uygun Ģekilde Osiloskop bağlantılarını yapıp

elde ettiğiniz sinyal Ģekillerini grafik alanına aktarınız.

Deney Bağlantı ġeması:

Bacak 1

0

5V

ġekil 1. Çift evirici devresi ( A

Bacak 3

A ).

ġekil 2. Enable-Disable devreleri (Veya kapılı).

Bacak 1ve 2

Out

Bacak 4

0

5V

ġekil 3. A A A kuralı.

Bacak 1

0

5V

Out

Bacak 1 ve 2

0

5V

Out

Bacak 1

Out

ġekil 4. A A A kuralı.

ġekil 5. Enable-Disable devreleri (Ve kapılı).

ġekil 6. A A A kuralı.

0

5V

ġekil 7. A A A kuralı.

Bacak 1

0

0

1

1

Bacak 3

0

1

0

1

Out 1

Out 2

ġekil 7. 7405 entegre devresi uygulaması.

Raporda Ġstenenler:

- Deney bağlantı Ģemalarını rapor defterinize çiziniz.

- Doğruluk tablolarını oluĢturunuz. (Tablolarda 0 ve 1 kullanınız.)

- Gerekli ise sinyal çizimlerini yapınız.

- AĢağıdaki soruları rapor defterinize cevaplayınız.

Sorular:

1. 7404 entegre devresi ile 7405 entegre devresi aynı kapı devreleridir. Bu iki entegre

devresi arasındaki farklılıkları iç bağlantı Ģemalarından yararlanarak belirtiniz.

DENEY 4- Boolean Kuralları Ve Lojik Denklemlerin SadeleĢtirilmesi

Öğrencinin Adı Soyadı:

Deney Uygulama Tarihi:

Öğretim Elemanı:

Numarası:

Rapor Teslim Tarihi:

Onay:

DENEY 5- Demorgan Teoremi

Amaç: DeMorgan Teoremini kullanarak Boolean

düzenleyerek değiĢtirmek.

denklemlerini

sadeleĢtirmek ve

Deneyin YapılıĢı:

- Deney bağlantı Ģemasında verilen devreleri uygun elemanlarla kurunuz. (Entegre

devrelerinin besleme ayakları şemaların yanındaki entegre bilgileri kısmında verilmiştir.)

- Doğruluk tablosunda verilen giriĢ lojik seviyelerini verilen anahtarları kullanarak devreye

uygulayın ve devrenin çıkıĢ lojik seviyelerini tabloya aktarınız.

- Devrede Osiloskop kullanılması gerekiyorsa uygun Ģekilde Osiloskop bağlantılarını yapıp

elde ettiğiniz sinyal Ģekillerini grafik alanına aktarınız.

Deney Bağlantı ġeması:

A B

0

0

0 +5

+5 0

+5 +5

U

V

W

X

Y

ġekil 1. DeMorgan teoremi devresi.

A A’ B W

0

0

0

+5

+5

0

+5

+5

ġekil 2. DeMorgan teoremi devresi

X

Y

A B

0

0

0 +5

+5 0

+5 +5

Şekil 3. DeMorgan teoremi devresi.

U

V

W

X

Y

ġekil 4. DeMorgan teoremi devresi.

A

0

0

0

0

+5

+5

+5

+5

B

0

0

+5

+5

0

0

+5

+5

C A’ B’ C’ Z X Y

0

+5

0

+5

0

+5

0

+5

A

0

0

0

0

+5

+5

+5

+5

B

0

0

+5

+5

0

0

+5

+5

C

0

+5

0

+5

0

+5

0

+5

U

V

W X Y

ġekil 4. DeMorgan teoremi devresi.

Raporda Ġstenenler:

- Deney bağlantı Ģemalarını rapor defterinize çiziniz.

- Doğruluk tablolarını oluĢturunuz. (Tablolarda 0 ve 1 kullanınız.)

- Gerekli ise sinyal çizimlerini yapınız.

- AĢağıdaki soruları rapor defterinize cevaplayınız.

Sorular:

2. Verilen Ģemaların Boolean eĢitliklerini yazınız.

3. Devrelerde verilen X ve Y çıkıĢları birbirlerine eĢdeğerdir. Bu durumu matematiksel

olarak gösteriniz.

DENEY 5- Demorgan Teoremi

Öğrencinin Adı Soyadı:

Deney Uygulama Tarihi:

Öğretim Elemanı:

Numarası:

Rapor Teslim Tarihi:

Onay:

DENEY 6- Ayrıcalıklı Veya (EXOR) Uygulamaları

Amaç:

- Temel lojik kapı devrelerini kullanarak EXOR fonksiyonunu üreteme yollarını öğrenmek.

- Yarı toplayıcı ve yarı çıkarıcı devrelerin çalıĢmasını incelemek.

Deneyin YapılıĢı:

- Deney bağlantı Ģemasında verilen devreleri uygun elemanlarla kurunuz.

- Doğruluk tablosunda verilen giriĢ lojik seviyelerini devreye uygulayın ve devrenin çıkıĢ

lojik seviyelerini tabloya aktarınız.

Deney Bağlantı ġeması:

A

B

0

0

0

1

1

0

1

1

X’

X

ġekil 1. EXOR devresi üretme yöntemi 1.

ġekil 2. . EXOR devresi üretme yöntemi 2.

A

B

0

0

0

1

1

0

1

1

X

A

B

0

0

0

1

1

0

1

1

X

ġekil 3. EXOR devresi.

A

B

0

0

0

1

1

0

1

1

ġekil 4. Yarı toplayıcı devresi.

A

B

0

0

0

1

1

0

1

1

D

Ba

ġekil 5. Yarı çıkarıcı devresi.

Raporda Ġstenenler:

- Deney bağlantı Ģemalarını rapor defterinize çiziniz.

- Doğruluk tablolarını oluĢturunuz. (Tablolarda 0 ve 1 kullanınız.)

- Gerekli ise sinyal çizimlerini yapınız.

- AĢağıdaki soruları rapor defterinize cevaplayınız.

S

C

Sorular:

4. Verilen devrelerin çıkıĢlarına ait lojik ifadeleri yazın ve gerekiyorsa sadeleĢtiriniz.

5. EXOR kapı devresi ile gerçekleĢtirilebilecek iki örnek uygulama devresi çiziniz. ÇıkıĢ

lojik ifadesini ve doğruluk tablosunu oluĢturunuz.

DENEY 6 Ayrıcalıklı Veya (EXOR) Uygulamaları

Öğrencinin Adı Soyadı:

Deney Uygulama Tarihi:

Öğretim Elemanı:

Numarası:

Rapor Teslim Tarihi:

Onay:

DENEY 7- Tam Toplayıcı ve Tam Çıkarıcı Devreleri

Amaç:

- Tam toplayıcı ve tam çıkarıcı devrelerini üretme yollarlını öğrenmek ve özelliklerini

incelemek.

Deneyin YapılıĢı:

- Deney bağlantı Ģemasında verilen devreleri uygun elemanlarla kurunuz.

- Doğruluk tablosunda verilen giriĢ lojik seviyelerini devreye uygulayın ve devrenin çıkıĢ

lojik seviyelerini tabloya aktarınız.

Deney Bağlantı ġeması:

A0

0

0

0

0

1

1

1

1

B0

0

0

1

1

0

0

1

1

C-1

0

1

0

1

0

1

0

1

S0

C0

ġekil 1. Yarı toplayıcılarla oluĢturulmuĢ tam toplayıcı devresi.

A1

A0

B1

B0

0

0

0

0

1

1

1

1

1

0

1

0

0

1

0

1

C1

ġekil 2. Ġki bitlik tam toplama devresi.

C1

S0

A

+

B

+

C0

A3A2A1A0

B3B2B1B0

C0

1010

0101

0

1010

0011

0

1111

0110

0

1111

1111

0

A

+

B

A3A2A1A0

B3B2B1B0

1010

0101

1010

0011

1111

0110

1111

1111

= Toplam

C3

=

S3S2S1S0

A+B=S

Onluk karĢılığı

D3D2D1D0

A+B=D

Onluk karĢılığı

Fark

Ba3

ġekil 3. 7483 entegresi ile tam toplayıcı ve tam çıkarıcı devre tasarımı.

Raporda Ġstenenler:

- Deney bağlantı Ģemalarını rapor defterinize çiziniz.

- Doğruluk tablolarını oluĢturunuz. (Tablolarda 0 ve 1 kullanınız.)

- Gerekli ise sinyal çizimlerini yapınız.

- AĢağıdaki soruları rapor defterinize cevaplayınız.

Sorular:

6. Verilen devrelerin çıkıĢlarına ait lojik ifadeleri yazın ve gerekiyorsa sadeleĢtiriniz.

7. 7483 entegresi hakkında bilgi veriniz.

DENEY 7- Tam Toplayıcı ve Tam Çıkarıcı Devreleri

Öğrencinin Adı Soyadı:

Deney Uygulama Tarihi:

Öğretim Elemanı:

Numarası:

Rapor Teslim Tarihi:

Onay: