BÜLENT ECEVĠT ÜNĠVERSĠTESĠ

MÜHENDĠSLĠK FAKÜLTESĠ

ELEKTRĠK-ELEKTRONĠK MÜHENDĠSLĠĞĠ BÖLÜMÜ

2012-2013 Öğretim Yılı- Bahar Dönemi

LOJĠK DEVRELER LABORATUVARI

DENEY FÖYÜ

Hazırlayanlar: ArĢ. Gör. Gülhan USTABAġ KAYA

ArĢ. Gör. UFUK ġAN

1

LOJĠK DEVRELER LABORATUARI GENEL BĠLGĠLER

Öğretim Üyesi:

Doç.Dr. Zehra SARAÇ

Laboratuar Sorumluları:

ArĢ. Gör. Gülhan USTABAġ KAYA

ArĢ.Gör. Ufuk ġAN

Laboratuar ÇalıĢmalarının Amacı:

a. Lojik Tasarım dersinde elde edilen teorik bilgilerin laboratuar ortamında geliĢtirilmesi,

b. Kombinezonsal ve ardıĢıl sayısal sistemlerin, tasarlanması, kurulması, yorumlanması ve

oluĢan hataların ayıklanması konusunda pratik bilgilerin elde edilmesidir.

Deneyler:

Toplam 10 deney yapılacaktır ( Deney1 – Deney10 ). Üçüncü haftadan itibaren deneyler

yapılmaya baĢlanacaktır. Öğrenciler katılmadıkları sadece ( 1 ) deneyi yılsonunda, telafi

deneyi ( Deney11 ) olarak yapabilirler. Telafi deneyinde not yükseltmek için daha önce

yapılan bir deney yapılamaz.

Devam Zorunluluğu:

Her öğrenci Laboratuar Notu alabilmek için en az 8 deneye ( telafi deneyi dâhil ) katılmak

zorundadırlar. Yılsonunda en fazla 3 deneye katılmamıĢ veya rapor vermemiĢ öğrenciler

devamsızlıktan kalırlar.

Laboratuar Notu:

Her deneyden önce ön çalıĢmalar kontrol edilecektir. Ayrıca her deneyden sonra rapor

hazırlama kılavuzunda belirtildiği Ģekilde bir grup raporu hazırlanacaktır. Öğrencilerin o

deneyden alacağı notu, laboratuar çalıĢması ve rapor notu belirleyecektir. Öğrencilerin

katılmadıkları veya rapor vermedikleri deneylerin notu sıfır olarak belirlenecektir. Yılsonunda

Laboratuar Notu Ortalaması, tüm deney notlarının toplanıp 10’a bölünmesiyle elde edilen

notun %60’ı ve laboratuardan final sınavında alınan notun %40’ı alınarak belirlenecektir.

2

LOJĠK DEVRELER LABORATUARI RAPOR YAZIM KILAVUZU

Laboratuar raporları, bilimsel bir çalıĢmada elde edilen sonuçları sunmak üzere aĢağıdaki

kurallara uygun olarak hazırlanacaktır.

Grup elemanları her deneyden sonra ortak bir grup raporu hazırlayacaklardır. Raporlar

beyaz A4 kâğıtlarının tek yüzüne, mümkünse bilgisayar ile ya da okunaklı bir el yazısı

ile yazılarak hazırlanacaktır. Çizimler bilgisayar ortamında ya da cetvel kullanarak

özenle yapılacaktır.

Raporlar bilimsel ve teknik bir anlatım tarzı kullanılarak Türkçe olarak yazılacaktır.

Raporlar, deneyi yapan tüm öğrencilerin isimlerinin ve imzalarının yer aldığı tek tip

kapak sayfası ile baĢlayacaktır. Kapak sayfasını, dersin web sayfasında ve

fotokopicide

bulabilirsiniz.

Bunların

dıĢında

farklı

yapılarda

kapaklar

kullanılmayacaktır.

Raporlar deneyin yapıldığı tarihten en geç bir hafta sonraki deneye kadar laboratuar

sorumlusu öğrenciye teslim edilmiĢ olacaktır. Teslim zamanından daha geç getirilen

raporlar kabul edilmeyecektir. Teslim edilmeyen raporların notu sıfır olarak

belirlenecektir.

Raporlar aĢağıdaki bölümlerden oluĢacaktır:

Amaç: Deneyde hangi konuların incelenmesi ve öğrenilmesi amaçlanmaktadır?

Devre Çizimleri: Deneylerde kurduğunuz devrelerin lojik çizimi raporda yer

alacaktır. Çizimler bilgisayar programında yapılacaktır. Bu diyagram üstünde

elemanların kullanılan uçları katalogdaki isimleri ile belirtilecektir.

Sonuçlar: Deneyin her bölümü için elde edilen sonuçlar (tablo, çizim, gözlem)

düzgün ve okunaklı bir Ģekilde yazılacak ve yorumlanacaktır. Eğer deneyde istenmiĢse

teorik olarak beklenen değerler ile deneyde elde edilen sonuçlar karĢılaĢtırılacaktır.

Sorular: “Ön Hazırlık” bölümünde sorulan soruların cevapları rapora yazılacaktır.

Yorum ve GörüĢler: Öğrenciler isterlerse deneyle ilgili yorum ve görüĢlerini bu

bölüme yazabilirler.

Rapor Kapağı: Raporlar sonraki sayfada verilen rapor kapağıyla birlikte verilecektir.

Kapakta deney no, grup no ve tarih yazılması unutulmayacaktır.

3

LOJĠK DEVRELER LABORATUARI RAPOR KAPAK FORMATI

BÜLENT ECEVĠT ÜNĠVERSĠTESĠ

MÜHENDĠSLĠK FAKÜLTESĠ

ELEKTRĠK-ELEKTRONĠK MÜHENDĠSLĠĞĠ BÖLÜMÜ

LOJĠK DEVRELER LABORATUVARI

DENEY RAPORU

Deney No:

Deneyin Adı:

Raporu Hazırlayan:

Deneyi Yapanlar-Grup Numarası:

Deney Tarihi- Deney Saati:

Raporun Teslim Edildiği Tarih:

Gecikme:

Rapor Notu:

4

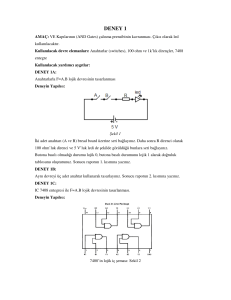

DENEY 1

DENEYĠN ADI

AND,OR,NOT KAPILARININ ENTEGRELERLE GERÇEKLENMESĠ

DENEYĠN AMACI

AND,OR,NOT kapılarını entegre yardımıyla gerçekleyerek doğruluk tablolarının çıkarılması,

Entegre kullanımın öğrenilmesi.

GEREKLĠ ELEMANLAR

1X7404(NOT kapısı)

1X7408(AND kapısı)

1X7432(OR kapısı)

1X330 ohm

1x LED

TEORĠ

AND KAPISI:

7408 TTL veya 4081 CMOS entegreleridir. Her iki entegrenin içerisinde 4 adet AND kapısı

mevcuttur. Bir AND kapısının çıkıĢı giriĢlerin çarpımına eĢittir. Çarpma iĢlemi Binary yapılır.

Bir AND kapısının giriĢlerinin tümü mantıksal 1 olduğunda çıkıĢ mantıksal 1'dir. Eğer

herhangi bir giriĢ mantıksal 0 ise çıkıĢ mantıksal 0'dır.

IC 7408 QUADRATURE 2 GĠRĠġLĠ AND KAPISI

5

OR KAPISI:

7432 TTL veya 4071 CMOS entegreleridir. GiriĢlerinden herhangi birisi mantıksal 1 ise çıkıĢ

mantıksal 1’dir.

IC 7432 QUADRATURE 2 GĠRĠġLĠ OR KAPISI

NOT KAPISI:

7404 TTL veya 4009 CMOS entegreleridir. ÇıkıĢı giriĢ voltajının mantıksal tersidir.

IC 7404 HEX NOT KAPISI

ÖN HAZIRLIK

TTL ve CMOS devrelerinin farklılıklarını, avantajlarını ve dezavantajlarını araĢtırınız.

AND, OR, NOT kapılarını kullanarak bir devre tasarlayınız.

PSPICE veya Proteus programlarından herhangi biriyle tasarladığınız devreyi

gerçekleyiniz.

DENEYSEL ÇALIġMA

Teori kısmında anlatılan kapıların doğruluk tablosunu sırasıyla çıkartınız.

6

SONUÇLAR

7

DENEY 2

DENEYĠN ADI

NAND,NOR,EXOR KAPILARININ ENTEGRELERLE GERÇEKLENMESĠ

DENEYĠN AMACI

NAND, NOR, EXOR kapılarını entegre yardımıyla gerçekleyerek doğruluk tablolarının

çıkarılması, Entegre kullanımın öğrenilmesi.

GEREKLĠ ELEMANLAR

1X7400(NAND kapısı)

1X7402(NOR kapısı)

1X7486(EXOR kapısı)

1X330 ohm

1x LED

TEORĠ

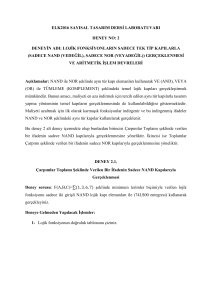

NAND KAPISI:

7400 TTL veya 4011 CMOS entegreleridir. AND kapısının çıkıĢına bir NOT kapısı

bağlanmasıyla elde edilir.

IC 7400 QUADRATURE NAND KAPISI

8

NOR KAPISI:

7402 TTL veya 4001 CMOS entegreleridir. OR kapısının çıkıĢına bir NOT kapısının

bağlanmasıyla elde edilir.

IC 7402 QUADRATURE NOR KAPISI

EXOR KAPISI:

7486 TTL veya 4030 CMOS entegreleridir. Ġki giriĢ aynı ise çıkıĢ mantıksal 0, Ġki giriĢ farklı

ise çıkıĢ mantıksal 1’dir. IC 7486 EXOR kapısı aĢağıda gösterilmiĢtir.

ÖN HAZIRLIK

NAND, NOR, EXOR kapılarını kullanarak bir devre tasarlayınız.

Sadece NAND kapılarını kullanarak EXOR kapısını tasarlayınız.

PSPICE veya Proteus programlarından herhangi biriyle tasarladığınız devreyi

gerçekleyiniz.

DENEYSEL ÇALIġMA

Teori kısmında anlatılan kapıların doğruluk tablosunu sırasıyla çıkartınız.

Ön hazırlık çalıĢmasında tasarladığınız EXOR kapısının doğruluk tablosunu çıkartınız.

9

SONUÇLAR

10

DENEY 3

DENEYĠN ADI

Sayısal sistemlerde toplama ve çıkarma iĢlemleri ile yapılan sadeleĢtirme teknikleri, Boole

Cebri

DENEYĠN AMACI

Lojik tasarımı için gerekli yöntemleri öğrenmek, mantık kapılarını kullanarak istenilen bir

lojik fonksiyonunu Boole Cebri Yöntemi ile en sade hale getirebilmek ve sadeleĢtirme

tekniklerini kavramak.

GEREKLĠ ELEMANLAR

Devre tasarımı öğrenciler tarafından yapılacaktır. Verilen tasarıma göre malzemeyi her grup

kendi belirleyecektir.

TEORĠ

Lojik devre tasarımında amaç, problemin analizi, en verimli metodu kullanarak problemin

çözümü ve en ucuz metodu kullanmaktır. Problemin çözümünde ilk safha doğruluk

tablosunun çizilmesidir. n sayıdaki giriĢ değiĢkeni için 2n olasılığı mümkün olan tüm

durumları ve yapılması istenilen sistemin giriĢ değerlerine karĢılık gelen her ihtimal için çıkıĢ

çalıĢma durumları yazılır. Problemin çözümünde ikinci safha, doğruluk tablosundaki giriĢler

yardımıyla Boole eĢitliğinin yazılmasıdır. ÇıkıĢ eĢitliğinin her bir ifadesi, "1" çalıĢma

durumunda olan giriĢ değiĢkenlerinin çalıĢma durumunu gösterir. Problemin çözümünün

üçüncü safhasında bulunan Boole eĢitliği sadeleĢtirilir. Lojik problemin son safhasında ise

sadeleĢtirilen devrenin eĢitliği çizilir.

ÖN HAZIRLIK

Bir fabrikadaki dört motordan en az üçünün çalıĢtığı anda çıkıĢı "1" olan devreyi

tasarlayınız.

ÇıkıĢ kapasitesi (Fan-Out) ve yayılım gecikmesi(propagation delay) terimlerini

araĢtırınız.

Herhangi bir lojik kapının çıkıĢ kapasitesinin nasıl arttırılacağını araĢtırınız.

PSPICE veya Proteus programlarından herhangi biriyle tasarladığınız devreyi

gerçekleyiniz.

11

DENEYSEL ÇALIġMA

Ön hazırlık çalıĢmasında tasarladığınız devreyi entegreleri kullanarak kurunuz. GiriĢ

değerlerine bütün ihtimalleri uygulayarak çıkıĢ değerini not ediniz.

SONUÇLAR

12

DENEY 4

DENEYĠN ADI

LOJĠK ĠFADELER, LOJĠK FONKSĠYONLARIN GÖSTERĠLMESĠ

DENEYĠN AMACI

Mantık kapılarını kullanarak istenilen bir lojik fonksiyonunun gerçeklenmesini öğrenmek ve

fonksiyonları birer deneyle gözlemlemek.

GEREKLĠ ELEMANLAR

Verilen tasarıma göre malzemeyi her grup kendi belirleyecektir.

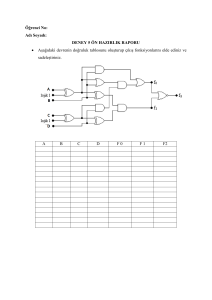

ÖN HAZIRLIK

Lojik Ġfadeler ve Lojik Fonksiyonlar hakkında kısa bir bilgi veriniz.

F=X ' YZ +XY ' Z + X ' Y ' Z ' fonksiyon ifadesini en sade biçimde gösterilecek Ģekilde

çözünüz. EXOR kapılarını kullanarak sadeleĢtirdiğiniz fonksiyonun devresini

tasarlayınız.

PSPICE veya Proteus programlarından herhangi biriyle tasarladığınız devreyi

gerçekleyiniz.

DENEYSEL ÇALIġMA

Ön hazırlık çalıĢmasında tasarladığınız devreyi entegreleri kullanarak kurunuz. GiriĢ

değerlerine bütün ihtimalleri uygulayarak çıkıĢ değerini not ediniz.

X

Y

Z

13

F

DENEY 5

DENEYĠN ADI

De’ Morgan Teoremi ile devre tasarımı

DENEYĠN AMACI

De’ Morgan Teoremini kullanarak VE iĢlemi ile VEYA iĢlemi arasında dönüĢüm yapmak.

GEREKLĠ ELEMANLAR

1X 7408 (AND kapısı)

1X 7432 (OR kapısı)

2X 330 Ω

2X LED

TEORĠ

DE MORGAN TEOREMĠ

DeMorgan teoremleri Boolean matematiğinin en önemli teoremleridir.

De Morgan teoremi kullanılarak VEYA iĢlemi ile VE iĢlemi arasında dönüĢüm yapılabilir. De

Morgan teoremi ile iĢlemler sadeleĢtirilerek daha basit hâle getirilebilir.

Bu teoremi açıklamadan önce Boolean çarpma ve Boolean toplama iĢlemi arasındaki

iliĢkiyi açıklayalım."Boolean matematiğinde çarpma iĢleminin komplementeri toplama

iĢlemine eĢittir." A,B gibi iki değiĢkenin VEDEĞĠL kapısına uygulanması ile elde edilen ifade

bu iki değiĢkenindeğilinin alınmasından sonra VEYA'lanması ile elde edilen ifadeye eĢittir.

14

Teorem1:

Teorem-1'e ait kapı eĢitliği ve doğruluk tablosu

"Boolean matematiğinde toplama iĢleminin komplementeri çarpma iĢlemine eĢittir."

A, B gibi iki değiĢkenin VEYA DEĞĠL kapısına uygulanması ile elde edilen ifade bu iki

değiĢkenin değilinin alınmasından sonra; giriĢler VE lojik iĢlemi ile elde edilen ifadeye eĢittir.

Teorem2:

Teorem-2'ye Ait Kapı EĢitliği ve Doğruluk Tablosu

ÖN HAZIRLIK

F 1 = a ' b c ' + a ' b ' c ve F 2 = a (b ' c+ bc) fonksiyonlarının De Morgan Teoremini

kullanarak tümleyen ifadelerini yazınız.

Bulduğunuz ifadeleri AND ve OR kapılarını kullanarak tasarlayınız.

PSPICE veya Proteus programlarından herhangi biriyle tasarladığınız devreyi

gerçekleyiniz.

15

DENEYSEL ÇALIġMA

Ön Hazırlık kısmında tasarladığınız devreyi kurunuz ve çıkıĢları gözlemleyiniz. GiriĢ

değerlerine bütün ihtimalleri uygulayarak çıkıĢ değerini not ediniz.

A

B

C

16

F

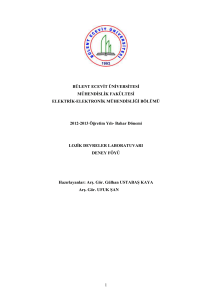

DENEY 6

DENEYĠN ADI

Lojik Fonksiyonlarının Kapılarla Gösterilmesi ve SadeleĢtirme

DENEYĠN AMACI

Tümlesik devre olarak üretilmiĢ kapı devreleri kullanarak: indirgenmiĢ fonksiyonların

gerçeklestirilmesi.

GEREKLĠ ELEMANLAR

Verilen tasarıma göre malzemeyi her grup kendi belirleyecektir.

TEORĠ

Lojik ifadelerin, lojik kapı entegre devreleri kullanılarak gerçekleĢtirilmesi için öncelikle

verilen ifadelerin sadeleĢtirilmesi gerekmektedir. Daha sonra giriĢleri lojik 0 ve lojik 1

uygulanarak gerçekleĢtirilen devrenin lojik fonksiyonu sağlayıp sağlamadığı test edilecektir.

ÖN HAZIRLIK

%45

A

%30

B

%15

C

%10

D

X

17

A,B,C,D sinyallerinin orantısal olarak dağılımı yüzde olarak tabloda verilmiĢtir. Bu

sinyaller aktif kabul edildiğinde “lojik 1”, pasif kabul edildiğinde “lojik 0 “değerini

almaktadır.

Aktif sinyallerin orantısal toplamı %50’nin üzerinde olduğu durumda çıkıĢı “lojik1” ,

%50’nin altında olduğu durumda “lojik 0” kabul ettiğimizde tablodaki çıkıĢ

değerlerini bulunuz.

Bulduğunuz lojik değerlerine göre bir X fonksiyonu oluĢturunuz.

OluĢturulan X fonksiyonunu en sade haline getiriniz.

SadeleĢtirilmiĢ fonksiyonu NAND ve NOR kapıları ile tasarlayınız.

PSPICE veya Proteus programlarından herhangi biriyle tasarladığınız devreyi

gerçekleyiniz.

DENEYSEL ÇALIġMA

Ön Hazırlık kısmında NAND ve NOR kapıları ile tasarladığınız devreleri kurunuz ve

çıkıĢları gözlemleyiniz. GiriĢ değerlerine bütün ihtimalleri uygulayarak çıkıĢ

değerlerini tablo çizerek gösteriniz.

18

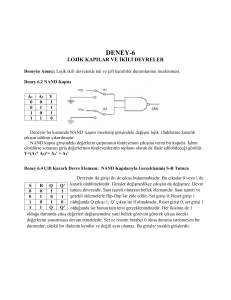

DENEY 7

DENEYĠN ADI

KARNOUGH HARĠTALARI YARDIMI ĠLE LOJĠK ĠFADELERĠN SADELEġTĠRĠLMESĠ.

DENEYĠN AMACI

Lojik ifadeleri Karnough haritaları yardımı ile çarpımların toplamı formunu kullanarak

yapılan sadeleĢtirme tekniğini kavramak.

GEREKLĠ ELEMANLAR

1X7400(NAND kapısı)

1X330 ohm

1x LED

TEORĠ

Karnough haritaları yardımı ile yapılan sadeleĢtirme iĢlemi indirgenmiĢ ifadenin formuna

göre çarpımların toplamı veya toplamların çarpımı olmak üzere iki ayrı Ģekilde olabilir. Lojik

ifadeleri Karnough haritaları yardımı ile çarpımların toplamı formunda indirgerken;

I.Doğruluk tablosundan alınan değerler Karnough haritasına aktarılır.

II. Karnough haritasında “1” olan kareler uygun bileĢkelere alınır.

a) BileĢke oluĢtururken içinde “1” olan karelerin sayısı 2n kadar olmalıdır.

Bir kare birden fazla bileĢke içinde bulunabilir.

Karelerin

bileĢke

oluĢturabilmeleri

için

birbirlerine

komĢu

olmaları

gerekmektedir.

KarĢılıklı köĢe ve kenarlardaki kareler birbirlerine komĢu kare sayılırlar.

III. BileĢke sonuçları VEYA’lanır ve indirgenmiĢ eĢitlik elde edilir.

BileĢke içinde durum değiĢtiren degiĢtiren değiĢkenler varsa ( 1’den 0’a veya 0’dan

1’e) bu değiĢkenler dikkate alınmaz.

BileĢke içindeki karelerinde durum değiĢtirmeyen değiĢkenler varsa indirgemede bu

değiĢkenler dikkate alınır. Eğer durum değiĢtirmeye değiĢkenler Lojik-0 ise

değiĢkenlerin değili, Lojik-1 ise değiĢkenlerin kendisi yazılır.

19

ÖN HAZIRLIK

Karnough haritaları yöntemini kullanarak F= AB ' (CD) ' + AB ' C D ' + (ABCD) ' lojik

ifadesinin Karnough Haritaları yardımı ile en sade halini elde ediniz.Elde edilen

fonksiyonu NAND kapıları ile gerçekleyiniz.

PSPICE veya Proteus programlarından herhangi biriyle elde ettiğiniz fonksiyonu

gerçekleyiniz.

DENEYSEL ÇALIġMA

Ön Hazırlık kısmında NAND kapıları ile tasarladığınız devreleri kurunuz ve çıkıĢları

gözlemleyiniz. GiriĢ değerlerine bütün ihtimalleri uygulayarak çıkıĢ değerlerini tablo

çizerek gösteriniz.

A

B

C

D

X

20

DENEY 8

DENEYĠN ADI

KODLAYICI (ENCODER), KOD ÇÖZÜCÜ (DECODER)

DENEYĠN AMACI

Kombinasyonel Devre Elemanları Yardımı ile Kodlayıcı (Encoder) ve Kod Çözücü (Decoder)

devrelerinin gerçekleĢtirilerek çalıĢmalarının incelenmesi

GEREKLĠ ELEMANLAR

1X 74138

1X 74148

2X 330 Ω

2X LED

TEORĠ

KOD ÇÖZÜCÜ (DECODER)

Decoder, N giriĢ hattından oluĢan binary giriĢ bilgisini 2 N çıkıĢ hattına çevirebilen

kombinasyonel devredir. Decoderler Ģekilde görüldüğü gibi yapı olarak N binary giriĢ hattını

M çıkıĢ hattına çevirdiklerinden dolayı NxM ya da N-M decoder olarak adlandırılır. Burada

M=2 N iliĢkisi söz konusudur.

NxM DECODER GENEL GÖRÜNÜġÜ

Genel olarak decoderlar IC paketler içerisinde 2x4,3x8,4x10,4x16 Ģeklinde düzenlenmiĢ

olarak bulunurlar. AĢağıdaki Ģekillderde decoder devresi ve doğruluk tablosu

görülmektedir.Decoder devresi görüldüğü gibi A ve B giriĢlerine ve bu giriĢlerin

kombinasyonuna bağlı olarak dört çıkıĢa sahiptir.

21

2x4 DECODER DEVRESĠ

2X4 DECODER DOĞRULUK TABLOSU

KODLAYICI (ENCODER)

Encoder bir decoderin tersi iĢlem yapan kombinasyonel bir lojik devredir. Bir encoder devre

2 N giriĢ hattına ve N çıkıĢ hattına sahiptir. ÇıkıĢ hatlarından 2 N değiĢken giriĢ için binary

kodlar üretir. GiriĢler M ve çıkıĢlar N olarak adlandırıldığında MxN ya da M-N encoder

olarak tanımlanabilir.

MxN ENCODER’ĠN GENEL GÖRÜNÜġÜ

22

ÖN HAZIRLIK

74138 entegresi ile 3x8 decoder devresi tasarlayınız.

74148 entegresi ile 8x3 encoder devresi tasarlayınız.

PSPICE veya Proteus programlarından herhangi biriyle tasarladığınız devreyi

gerçekleyiniz.

DENEYSEL ÇALIġMA

Ön hazırlık çalıĢmasında tasarladığınız decoder ve encoder devrelerini kurarak çıkıĢlarını

gözlemleyiniz.

23

DENEY 9

DENEYĠN ADI

R-S, J-K,D,T FLĠP-FLOPLARI

DENEYĠN AMACI

R-S, J-K,D,T flip-floplarının doğruluk tablolarının çıkarılması.

GEREKLĠ ELEMANLAR

1X 7400

1X 7476

1X 7474

1X7404

2X330 ohm

2XLED

TEORĠ

Sayısal “0” ve “1” bilgilerinin depolanması iĢlemi amasıyla kullanılan en temel hafıza

elemanları flip-floplardır.

R-S FLĠP-FLOP:

24

J-K FLĠP-FLOP:

J-K Flip-Flop çalıĢma yapısı olarak tetiklemeli R-S Flip-Flopa benzer. Ancak R-S Flip-Flop

için yasaklanan 1-1 giriĢi J-K Flip-Flopu iğle kullanılır hale getirilmiĢtir.

D FLĠP-FLOP:

D tipi Flip-Flop Ģekil ve yapı olarak R-S Flip-Flopa çok benzemektedir. Tek farkı S ve R

giriĢleri arasına bir adet değil kapısı bağlanarak S giriĢini D giriĢi olarak kabul eder. D FlipFlop giriĢine uygulanan lojik seviyeyi her tetikleme anında örnekleyerek çıkıĢına aktarır.

25

T(TOGGLE) FLĠP-FLOP:

T tipi Flip-Flop J-K tipi Flip-Flop’un aynısı olup, J ve K giriĢleri birleĢtirilip T tipi Flip-Flop

oluĢturulmuĢtur. Her iki giriĢ birleĢtirildiğine göre, T giriĢine 0 uygulamak J=0,K=0

yapmaktır ki, bu durumda çıkıĢ bir önceki halini korur. T=1 uygulayarak J=1,K=1 yapmıĢ

oluruz ki bu durumda, çıkıĢ bir önceki halinin tersini alır.

ÖN HAZIRLIK

J-K, D Flip-Floplarıyla ilgili katalog bilgilerini edinin, bağlantı bacaklarının

fonksiyonun araĢtırın.

PSPICE veya Proteus programlarından herhangi biriyle tasarladığınız devreyi

gerçekleyiniz.

DENEYSEL ÇALIġMA

R-S Flip-Flop devresini NAND kapılarıyla gerçekleĢtirin, doğruluk tablosunu

oluĢturun.

J-K Flip-Flop devresini önce NAND kapılarıyla, daha sonra 7476 yardımıyla

gerçekleyiniz. Doğruluk tablolarını çıkarınız.

D Flip-Flop deversini 7474 yardımıyla gerçekleyiniz. Doğruluk tablolarını çıkarınız.

T Flip-Flop devresini 7476 yardımıyla gerçekleyiniz. Doğruluk tablolarını çıkarınız.

26

SONUÇLAR

27

DENEY 10

DENEYĠN ADI

SHĠFT REGĠSTERS (KAYMALI KAYDEDĠCĠLER)

DENEYĠN AMACI

Shift Register temel mantığını ve yapısını anlamak.

GEREKLĠ ELEMANLAR

2X 7474

4X 330 Ω

4X LED

TEORĠ

Flip-Flopların temel özelliklerinden birisi de bilgi depolama kabiliyetleridir. Flip-Floplarla

gerçekleĢtirilen ve bilgi saklama veya kaydırma amacına yönelik devreler kaydedici devreler

olarak adlandırılır. Yapı itibariyle en çok D Flip-Flopların kullanıldığı register devrelerinde

ilave herhangi bir kapıya ihtiyaç duyulmazken, RS ve JK Flip-Floplarla gerçekleĢtirilen

register devrelerinde NOT kapısına ihtiyaç vardır. AĢağıdaki Ģekilde D Flip-Floplarla

gerçekleĢtirilmiĢ bir kaydırıcı kaydedici devre bulunmaktadır.

28

Seri giriĢ ilk Flip-Flop data giriĢine uygulanmaktadır. Ġlk tetikleme ile birlikte D giriĢindeki

data Q çıkıĢına aktarılır. Bir Flip-Flop'un Q çıkıĢının diğer Flip-Flop'un D giriĢine

bağlanmasıyla ikinci CP tetikleme ile birlikte birinci Flip-Flop yeni datayı örneklerken ikinci

Flip-Flop Q değerini örnekleyerek çıkıĢına aktarır. Böylelikle her tetiklemede seri giriĢten

uygulanan data kaydırılmıĢ olur.

Yukarıdaki tabloda da görüldüğü gibi seri data gririĢine sırasıyla 1 0 1 1 1 1 datası

uygulanmakta, her bir CP shift pulse'inde FFQ çıkıĢları biri basamak sağa kaydırılmaktadır.

FF4Q paralel çıkıĢların dördüncüsüdür. Aynı zamanda registerin seri çıkıĢını da

oluĢturmaktadır.

29

ÖN HAZIRLIK

Shift reister devrelerinde sağa kaymalı olarak kurulan devreleri sola kaymalı hale

getirmek için ne gibi değiĢiklikler yapılmalıdır.

Shift register devreleri nerelerde kullanılır.

PSPICE veya Proteus programlarından herhangi biriyle tasarladığınız devreyi

gerçekleyiniz.

DENEYSEL ÇALIġMA

ġekilde gösterilen Shift Register devresini kurun. Paralel çıkıĢlara akım sınırlayıcı bir

direnç ve LED bağlayın. GiriĢe kare dalga uygulayın. ÇıkıĢ sinyalini giriĢ sinyali ile

birlikte gözleyin.

30