Ondokuz Mayıs Üniversitesi - Gebze Teknik Üniversitesi

advertisement

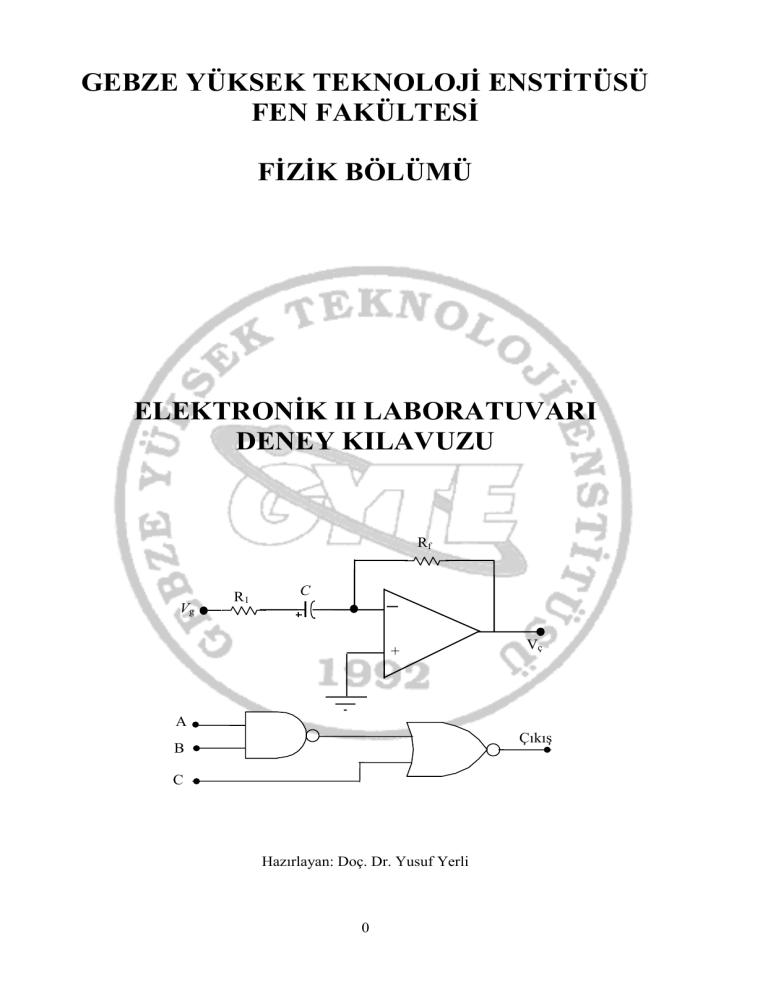

GEBZE YÜKSEK TEKNOLOJĠ ENSTĠTÜSÜ

FEN FAKÜLTESĠ

FĠZĠK BÖLÜMÜ

ELEKTRONĠK II LABORATUVARI

DENEY KILAVUZU

Rf

Vg

R1

C

─

+

Vç

A

ÇıkıĢ

B

C

Hazırlayan: Doç. Dr. Yusuf Yerli

0

ĠÇĠNDEKĠLER

SAYFA NO

NOTLARIN BELĠRLENMESĠ

2

ELEKTRONĠK LABORATUVARI KURALLARI

3

DENEYLER YAPILIRKEN DĠKKAT EDĠLMESĠ GEREKEN NOKTALAR

3

ELEKTRONĠK LABORATUVARI RAPOR YAZIM KILAVUZU

4

ÖRNEK RAPOR KAPAĞI

5

1.

OSĠLATÖRLER

6

2.

FARK YÜKSELTEÇLERĠ

16

3.

DOĞRUSAL TÜMDEVRELER

24

4.

TOPLAMA, ÇIKARMA, TÜREV, ĠNTEGRAL VE KIYASLAYICI

DEVRELER

5.

31

ĠġLEM YÜKSELTEÇLERĠNĠN FREAKANS-KAZANÇ

KAREKTERĠSTĠĞĠ VE KARE DALGA ÜRETECĠ

39

6.

MANTIK DEVRELERĠ

43

7.

ĠKĠLĠ TOPLAMA VE TAM TOPLAYICILAR

57

8.

FLOP-FLOP VEYA TETĠKLEME DEVRELERĠ

61

9.

SAYICILAR

63

10. ĠKĠLĠ-ONDALIK KODLAYICILAR VE LED GÖSTERGELER

1

69

ELEKTRONĠK II LABORATUVARI

Öğretim Üyesi: Doç. Dr. Yusuf YERLİ

Deneyler: Toplam 10 deney yapılacaktır (Deney1-Deney10).

Öğrenciler katılmadıkları sadece bir deneyi yılsonunda, telafi deneyi olarak yapabilirler. Tüm

deneylere katılmıĢ olan öğrencilerden isteyenler, 50’nin altında not aldıkları sadece bir deneyi

notlarını yükseltmek için telafi döneminde tekrar edebilirler.

Notların Belirlenmesi:

1. Devam Zorunluluğu: Her öğrenci vize alabilmek için en az 8 deneye (telafi deneyi

dahil) katılmak zorundadır.

2. Deney Notu: Her deneyden önce ön çalıĢmalarla ilgili sorular sorulacaktır. Ayrıca her

deneyden sonra rapor hazırlama kılavuzunda belirtildiği Ģekilde bir grup raporu

hazırlanacaktır. Öğrencilerin o deneyden alacağı notu, laboratuvar çalıĢması ve rapor

notu

belirleyecektir.

Öğrencilerin

katılmadıkları

deneylerin

notu

sıfır

olarak

belirlenecektir. Yılsonunda deney notu ortalaması, tüm deney notlarının toplanıp 10’a

bölünmesiyle elde edilecektir. Birbirinin kopyası olduğu belirlenen raporlar –10 puan ile

cezalandırılacaktır.

3. Dönemiçi Sınavları: Dönem içinde, deneyler arasındaki bir hafta yazılı bir sınav

yapılacaktır. Dönemiçi sınavının yapıldığı günlerde deney yapılmayacaktır.

4. Dönemsonu Sınavı: Tüm deneyler tamamlandıktan sonra deneylerde elde edilen bilgileri

sınamaya yönelik dönemsonu sınavı uygulamalı olarak yapılacaktır. Bir öğrencinin

dönemsonu sınavına girebilmesi için telafi deneyleri bittikten sonra en az 8 deneye

katılmıĢ olması zorunludur.

5. BaĢarı Notu: Dönemsonu baĢarı notu aĢağıdaki ağırlıklara göre hesaplanacaktır:

Deney notu ortalaması

:%25

Dönemiçi Sınavı

:%25

Dönemsonu Sınavı

:%50 Uygulama

2

ELEKTRONĠK LABORATUVARI KURALLARI

Elektronik Laboratuvarı, öğrencilerin Elektronik bilgilerini pratik yönden geliĢtirmeyi

ve bu konuda yeni bilgiler edinmelerini sağlamak amacıyla hazırlanmıĢtır. Laboratuvar

çalıĢmalarının verimli olabilmesi için deneylerin aĢağıdaki kurallara uygun olarak yapılması

gerekmektedir:

1. Öğrenciler, laboratuvar çalıĢmalarından bir yarar elde edebilmek için yapacakları deneye

iliĢkin kılavuzu önceden mutlaka okumalı ve her deneye hazırlıklı gelmelidir.

Deneylerden önce öğrencilere ön çalıĢmalarla ilgili sözlü sorular sorulacaktır.

2. Deneye ilk 15 dakikada geç gelen öğrenciler uyarılırlar. Ġkinci defa bir deneye geç gelen

öğrenci o deneye alınmaz. Deneye 15 dakikadan daha geç gelen öğrenciler deneye

alınmazlar.

3. Deneylerin süresi 1.5 saat olarak öngörülmüĢtür. Deney süresince laboratuvardan çıkmak

yasaktır. Deneylerini erken bitiren gruplar laboratuvar dersi sona ermeden önce

çıkabilirler.

4. Her deneyin raporu ertesi haftaki laboratuar saatinde mutlaka getirilmelidir. Raporu

getirmeyenler o deneyden sıfır puan almıĢ olurlar.

5. Yönetmelik gereğince öğrenci deneylere %80 oranında devam etmek mecburiyetindedir.

Devam, her deneyde yoklama yapılarak tespit edilecektir.

6. Öğrencinin gelmediği deneyden alacağı not sıfırdır.

7. Öğrencinin yalnızca bir deneyi telafi etme hakkı vardır.

8. Deneyde kullanılacak olan malzeme (elektronik elemanlar, el aletleri, kablolar) deneyi

yaptıracak olan öğretim elemanından sayılarak teslim alınacaktır. Deney sonunda aynı

malzeme eksiksiz olarak geri verilecektir. Gruplar, kaybettikleri veya zarar verdikleri

malzemenin yerine yenisini koymak zorundadır. Bu nedenle deney süresince baĢka

grupların malzemelerini almayınız ve kendi malzemelerinizi baĢka gruplara vermeyiniz.

9. Diğer grupları rahatsız etmemek ve daha olumlu bir çalıĢma ortamı sağlamak için

laboratuvarda mümkün olduğu kadar sessiz çalıĢınız.

DENEYLER YAPILIRKEN DĠKKAT EDĠLMESĠ GEREKEN NOKTALAR:

1. Devreleri kurarken gerilim kaynağı mutlaka kapalı olmalıdır.

2. Devreye gerilim verilmeden önce yapılan bağlantıların doğruluğu kontrol edilmeli.

a. Devrelerin besleme ve toprak hatları doğru olarak bağlandı mı?

b. Besleme gerilimi ve toprak hattı arasında kısa devre oluĢabilir mi?

c. ÇıkıĢ olan bir hatta yanlıĢlıkla giriĢ iĢareti uygulanmıĢ olabilir mi?

d. ÇıkıĢlar yanlıĢlıkla kısa devre edilmiĢ olabilir mi?

e. Bağlantılar, deneyde istenen iĢlemi gerçekleĢtirmek üzere doğru olarak yapıldı mı?

3. Tüm bağlantıların doğruluğundan emin olduktan sonra devreye besleme gerilimi

verilmeli. Eğer devre beklendiği gibi çalıĢmıyorsa hemen besleme gerilimi kapatılarak

devre kontrol edilmeli. Kontrol iĢleminde 2. maddede belirtilen noktalara dikkat edilmeli.

4. Doğru çalıĢtığından Ģüphe edilen elemanların devre ile bağlantıları kesilmeli ve bu

elemanlar ayrı olarak test edilmelidir.

5. Devre üzerinde değiĢiklik yaparken (eleman ekleme/çıkarma, bağlantı değiĢtirme) gerilim

kaynağı mutlaka kapalı olmalıdır.

6. Tüm uğraĢılara rağmen hata bulunamıyorsa laboratuvarda görevli öğretim elemanından

yardım istenmelidir.

3

Elektronik Laboratuvarı Rapor Yazım Kılavuzu

Laboratuvar raporları, bilimsel bir çalıĢmada elde edilen sonuçları sunmak üzere

aĢağıdaki kurallara uygun olarak hazırlanacaktır.

1. Grup elemanları her deneyden sonra ortak bir grup raporu hazırlayacaklardır. Raporlar

beyaz A4 kâğıtlarının tek yüzüne, mümkünse bilgisayar ile ya da okunaklı bir el yazısı ile

yazılarak hazırlanacaktır. Çizimler bilgisayar ya da cetvel kullanarak bir mühendis

özeniyle yapılacaktır.

2. Raporlar bilimsel ve teknik bir anlatım tarzı kullanılarak Türkçe olarak yazılacaktır.

3. Raporlar, deneyi yapan tüm öğrencilerin isimlerinin ve imzalarının yer aldığı tek tip

kapak sayfası ile baĢlayacaktır.

4. Raporlar bir sonraki deneyde mutlaka getirilmelidir. Raporlarınızı deneyi yaptıran

öğretim üyelerine doğrudan vermeyiniz. Teslim zamanından daha geç getirilen raporlar

kabul edilmeyecektir. Eğer teslim tarihi tatil gününe denk geliyorsa tatilden sonraki ilk iĢ

günü rapor teslim edilecektir. Teslim edilmeyen raporların notu sıfır olarak

belirlenecektir.

5. Raporlar aĢağıdaki bölümlerden oluĢacaktır:

Deney No ve Adı:

Amaç: Deneyde hangi konuların incelenmesi ve öğrenilmesi amaçlanmaktadır?

Verilerin değerlendirilmesi: Bu bölümde deneyde kullanılan devre Ģemaları çizilecek ve

veriler tablolar halinde verilecektir. Grafikler çizilecek, hesaplamalar yapılacaktır. Daha sonra

veriler deney kılavuzunda tarif edildiği gibi değerlendirilecektir.

Sonuçlar: Deneyin her bölümü için elde edilen sonuçlar (tablo, çizim, gözlem) düzgün ve

okunaklı bir Ģekilde yazılacak ve yorumlanacaktır. Eğer deneyde istenmiĢse teorik olarak

beklenen değerler ile deneyde elde edilen sonuçlar karĢılaĢtırılacaktır. Tamamlayamadığınız

bölümler için de beklenen sonuçları yazınız.

Sorular: Deney kılavuzunda sorulan sorularının cevapları rapora yazılacaktır.

Yorum ve GörüĢler: Öğrenciler isterlerse deneyle ilgili yorum ve görüĢlerini bu bölüme

yazabilirler.

4

GEBZE YÜKSEK TEKNOLOJĠ ENSTĠTÜSÜ

FĠZĠK BÖLÜMÜ

ELEKTRONİK II LABORATUVARI

DENEY RAPORU

DENEY NO

:

DENEYİN ADI

:

DENEY TARİHİ

:

RAPOR TESLİM TARİHİ :

GRUP NO

:

DENEYİ YAPANLAR

:

Numara

Adı

Soyadı

DENEYİ YAPTIRAN

ÖĞRETİM ELEMANI:

5

İmza

DENEY NO

DENEYĠN ADI

DENEYĠN AMACI

1234-

:EII-1-A

: OSĠLATÖRLER

:

Osilatör prensiplerinin öğrenilmesi.

TitreĢim frekansını kontrol etme metotlarını öğrenme.

Osilatörlerin çıkıĢ sinyalinin geribesleme, faz iliĢkisi ve yükseltme yönünden incelenmesi

RC Faz kaymalı osilatör kullanılarak frekans, faz farkı ve yükseltme iliĢkisinin pratik

olarak anlaĢılmasının sağlanması.

ÖN BĠLGĠ

Osilatörler, belirli frekanslarda alternatif sinyal elde etmeye yarayan elektronik

aygıtlardır. Sinyalin frekansı devrede kullanılan R, L, C gibi elemanların değerlerine bağlıdır.

Osilatörler radyo, TV alıcı ve vericilerinde, radarlarda, bilimsel araĢtırmalarda, endüstride ve

daha pek çok alanlarda kullanılmaktadır.

Bir osilatör, devre içinde elektronların ileri geri hareketleriyle yapılır. Bu olay,

mekanikte kütle-yay veya sarkaç hareketiyle aynıdır. Bir sarkaç, önce dengesi bozularak

harekete baĢlatılır. Eğer sistemde herhangi bir sürtünme yoksa salınım sürekli devam eder.

Ancak, gerçek bir sarkaçta sürtünme yok edilemez ve salınım sönümlü olur. Neticede, genliği

zamanla azalan ve sonunda duran bir salınım elde edilir. Salınımın sürekli olabilmesi için,

sarkaca salınım periyoduyla aynı periyotta bir alternatif kuvvet uygulanmalıdır. Bu kuvvet

gerçekte çok küçüktür ve sürtünmeden doğan kaybın yok edilmesi içindir.

Elektrik salınımlar ki biz buna osilatör diyoruz, benzer Ģekilde meydana gelirler.

Örnek olarak bir paralel LC devresini ele alalım (ġekil 1.1.).

S1

S2

+

C

V

L

ġekil 1.1. LC Tank devresi

Önce anahtarı S1 konumuna alarak C kondansatörünü dolduralım ve anahtarı S2

konumuna alalım. ġimdi V kaynağı devre dıĢı kalmıĢ, sadece L ve C paralel bağlı hale

gelmiĢtir. Kondansatörde biriken yük L bobini üzerinden boĢalacak ve boĢalırken de bobin

etrafında büyüyen bir manyetik alan meydana getirecektir. Kondansatör tamamen boĢaldığı

zaman bobin etrafındaki manyetik alan azalacak ve azalırken de bobin üzerinde ters yönde bir

akım indükleyecektir. Bu akım geri dönerek kondansatör tekrar dolacaktır. Kondansatör tam

dolduğu zaman tekrar bobin üzerinden boĢalacak ve bu hareket sürekli devam edecektir. Tabii

ki bu süreklilik Ģartı, devrede herhangi bir söndürücü eleman olmadığı zaman olabilir ve

böyle bir durum ancak süper-iletken bağlantılarla olabilir. Gerçekte, devredeki bağlantılar,

bobin ve kondansatör üzerindeki ohmik dirençten dolayı güç harcanır ve salınım kısa sürede

söner. Bu devrenin ifadesi,

d 2i

di 1

L 2 R i 0 Ģeklindedir.

dt C

dt

Birinci ve üçüncü terimler bobin ve kondansatörle ilgilidir. Ġkinci terim, yani direnç terimi

sönüm terimidir. Böyle bir diferansiyel denklemin çözümü bize ġekil1.2 deki grafiği verir.

Görüldüğü gibi salınım zamanla küçülerek yok olmaktadır (Sönüm teriminden dolayı). Bu

grafik akım, gerilim (voltaj) ve yük değiĢimleri için birbirinin benzeridir.

6

V,i,q

t

ġekil 1.2.

Sönüm terimini yok etmek için ya süper iletken bağlantıları kullanılmalı, ya da o

terimi yok edecek değerde bir kaynaktan devre sürekli beslenmelidir. Bir LC paralel tank

devresinin frekansı

1

f

2 LC

ifadesiyle verilir. Devreyi besleyen kaynak frekansı bu değerde olmalıdır. ġimdi, devreye bir

sürücü F(t) kuvveti uygulayalım.

d 2i

di 1

L 2 R i F (t ) A sin 2 f t

dt C

dt

F (t ) A sin 2 f t ifadesi sönüm terimine eĢdeğer bir sürücü kuvvet terimidir. Salınımı

sürekli besleyerek sönüm olmasını engeller.

F(t) sürücü kaynağı, her zaman devreye dıĢarıdan bağlanmaz. Yani buna gerek yoktur.

Bunun yerine LC tank devresindeki salınımı bir amplifikatörle (yükseltici) yükseltilir ve bu

yükseltilen salınımın bir kısmını geri tank devresine vererek salınımın devamlı olmasını

sağlarız. Bu iĢleme Pozitif Geri Besleme denmektedir. ġekil 1.3 te böyle bir yükseltici ve geri

besleme akıĢ diyagramı verilmiĢtir.

Geri besleme

Yükseltici

ÇIKIġ

C

L

ġekil 1.3.

OSĠLATÖR ÇEġĠTLERĠ

Bir devrede kullanılan elemanlara, yükseltme ve geri besleme iĢlemlerine bağlı olarak

çeĢitli osilatörler geliĢtirilmiĢtir. Bu osilatörlerden bazıları Hartley osilatörü, tikler bobinli

osilatör, akortlu osilatör, faz kaymalı osilatörler v.s. dir. ÇeĢitli kaynaklarda bu osilatörlerle

ilgili yeterli bilgiler mevcuttur. Biz bu deneyimizde sadece faz kaymalı osilatörü

inceleyeceğiz.

FAZ KAYMALI OSĠLATÖR

7

Bir osilasyonun olabilmesi için iki Ģart olduğunu söylemiĢtik: Yükseltme ve Geri

Besleme. Bu deneyimizde salınım elemanı olarak R ve C kullanılacaktır. Bilindiği gibi seri

bağlı RC devresinde kondansatör ya exponansiyel (üstel) olarak dolar ya da exponansiyel

boĢalır. Paralel LC devresinin aksine bu devrede hiç salınım olmaz. Ancak kondansatörün her

boĢalmasından sonra tekrar dıĢarıdan doldurulmasıyla sürekli bir salınım meydana

getirilebilir. Bu iĢlem yine bir yükselticide uygun fazda geri besleme ile yapılabilir.

C

R

Vi

Vo

ġekil 1.4.

ġekil 1.4 teki RC devresini ele alalım. Vi kaynağı da bir sinüs kaynağı olsun. Devreye

Vi kaynağının uyguladığı gerilim ve R uçlarındaki gerilim arasında aĢağıdaki ifadede verilen

kadar bir faz farkı mevcuttur. Faz farkı, salınım frekansı, R ve C değerlerine bağlıdır.

X

X

1

veya arctan C

tan C

R

2 fRC

R

ifadesindeki faz farkı, direncin keyfi olarak sıfır yapılamaması yüzünden 90 olamaz.

YaklaĢık 0 ve 90 değerleri arasında değiĢir.

Devrenin bu özelliklerini göz önüne alarak bir yükseltici transistör ile devreyi ele

alalım (ġekil 1.5.). Kullandığımız transistörün bir özelliği olarak baz gerilimiyle kollektör

gerilimi arasında 180 faz farkı olmalıdır.

R1

Rc

Vcc

ÇIKIS

Q1

C2

R2

RE

C1

ġekil 1.5.

Devrede kollektörden gelen geri-besleme sinyali ile baza giden sinyal arasında

X

tan C 2

R2

faz farkı mevcuttur. Dolayısıyla devre sönümlü giriĢim yaparak salınıma girmez. Fazın 180

olabilmesi için R ve C değerleri öyle seçilir ki faz 60 olsun. Aynı Ģekilde hazırlanmıĢ üç tane

RC devresi ard arda bağlanarak 180 faz farkı elde edilir, ġekil 1.6.

8

RB 1

Rc

Vcc

C1

C2

Q1

C3

R1

RB 2

R2

RE

ÇIKIS

C4

ġekil 1.6.

Devreye eklediğimiz yükseltici, Ortak Emitörlü Yükselticidir. Yani geri besleme,

kollektörden baza doğrudur (ÇıkıĢtan giriĢe doğru). Transistörlü RC osilatör devresinin çıkıĢ

sinyalinin frekansı ve genliği geri besleme hattındaki direnç ve kondansatörlerin değerlerine

bağlıdır. Üç kısımlı salınım devresi R1C1, R2C2, RB2C3 elemanlarından oluĢur. RC çiftleri

öyle seçilmelidir ki her bir halkada faz kayması 60 olsun. Bundan sonra yapılacak Ģey R1 =

R2 = RB2 = Rg (Ortak emitörlü yükseltecin giriĢ empedansı) ve C1 = C2 = C3 elemanlarını

seçmektir. Bu Ģartlar altında salınım frekansı

1

f

4R

2R1C 6 C

R1

olacaktır. Salınımın sürekli olabilmesi için ayrıca yükseltici transfer katsayısının (kazancının)

belirli bir değerin üzerinde olması da gerekmektedir. Bu değer ise,

29 R1 4 RC

hFE 23

RC

R1

olmalıdır. Yani transistör alternatif akım kazancının bu değerde veya daha yüksek olması

lazımdır. Aksi halde yeterli büyütme ve geribesleme olmayacağından salınım sönümlü

olacaktır.

ARAÇLAR

Güç kaynağı

Osiloskop, Voltmetre

Dirençler: 3x10k, 3.3k, 5.6k, 33k, 5k (Potansiyometre)

Kondansatörler: 3x10nF, 3x4.7nF, 47µF

Transistör: BC238

DENEYLER

RC FAZ KAYMALI OSĠLATÖR

1-ġekil 1.7 deki devreyi kurunuz.

2-Osiloskopla kollektör ve bazdaki dalga Ģekillerini görüntüleyiniz.

3-Frekansı ölçünüz ve Tablo 1.1 e yazınız. Hesapla bulunan değerle karĢılaĢtırınız.

Tablo 1.1

Ölçülen

Frekans

Hesaplanan

9

RB 1

33kohm

Rc

5.6kohm

Vcc

12V

C1

C2

P1

P2

10nF

10nF

ÇIKIS

Q1

C3

BC238BP

P3

10nF

R1

R2

10kohm

10kohm

RB 2

RE

10kohm

3.3kohm

C4

47uF

ġekil 1.7.

4-P1, P2 ve P3 noktalarındaki geri besleme sinyallerinin Ģeklini ve tepeden tepeye genliklerini

ölçerek Tablo 2 yi doldurunuz.

Tablo 1.2

Test

Noktaları

Dalga ġekli

VT-T

P1

P2

P3

5-Lissajous Ģekli yöntemini kullanarak çıkıĢ sinyali ile P1, P2 ve P3 noktaları arasındaki faz

farkını ölçerek Tablo 3 ü doldurunuz.

Tablo 1.3

b

a

sin 1 b a (Faz açısı)

P1

P2

P3

6- Devre elemanlarından hesapladığınız faz kayması ile ölçtüğünüz faz kaymasını Tablo 4 ü

kullanarak karĢılaĢtırınız.

Tablo 1.4

arctan X C R (Hesaplanan)

P1

P2

P3

10

Ölçülen

7- Rc direnci yerine 5k luk potansiyometre takarak bunun maksimum ve minimum

konumlarında çıkıĢ dalga Ģeklinin tepeden tepeye değerini ölçünüz.

8- Rc direncini maksimumu konuma alınız ve C1 = C2 = C3 = 4.7nF yaparak çıkıĢ sinyalinin

frekansını yeniden ölçünüz. Yeniden hesaplayacağınız frekans değeri ile karĢılaĢtırınız. Bu

frekans değerini 3.maddede bulduğunuz değerle karĢılaĢtırarak yorumlayınız.

SORULAR

1- Bir osilatör devresi oluĢturmak için gerekli Ģartlar nelerdir?

2- Faz farkı meydana getirmeyen yani çıkıĢı ile giriĢi arasında faz farkı 0 derece olan bir

yükseltici kullanıldığında geri besleme devresinin fazı ne olmalıdır?

3- L = 4mH ve C = 1nF olan bir LC osilatöründe titreĢim frekansı ne olur?

4- Bir RC faz kaymalı osilatör C = 4.7nF veR = 5.6k değerlerine sahipse osilatör frekansı ne

olur?

5- Bir osilatörde geri besleme devresi olarak kullanılan RC faz kaymalı devre iki bölüme

sahip olamaz. Bunun sebebi nedir?

6- Bir osilatörün geri besleme devresi -12 dB’lik bir zayıflatma yaparsa yükselticinin voltaj

kazancı ne olmalıdır?

11

DENEY NO

DENEYĠN ADI

:EII-1-B

: MULTĠVĠBRATÖRLER

KOLLEKTÖRÜ ÇİFTLENMİŞ MULTİVİBRATÖR

DENEYĠN AMACI

: Bir astable(serbest) multivibratörün dalga

incelenmesi, frekansının ölçülmesi.

Ģeklinin

ÖNBĠLGĠ

RC osilatörlere multivibratör diye isimlendirilen yeni bir tip daha ekleyeceğiz.

Multivibratörler, sinüs olmayan dalga üreticileridir. Dalga Ģekilleri kare, üçgen veya testere

diĢi olabilir. Her bir dalga Ģeklinin pek çok yerde geniĢ uygulaması vardır.

Bir multivibratör, rahatlama osilatörüdür. Ya dıĢarıdan herhangi bir uyarı olmaksızın

kendi kendilerini tetikleyerek çalıĢırlar, ya da çalıĢmaları dıĢarıdan bir osilatörle kontrol edilir.

Serbest çalıĢan multivibratörlere astable multivibratörler denmektedir. Bunların frekansları

içten olduğu gibi dıĢarıdan bağlanan senkronizasyon darbesiyle de kontrol edilir.

DıĢarıdan bir kaynaktan uyarılarak çalıĢtırılan multivibratörler gerçekte osilatör

değildir. Bu tip multivibratörlerin iki çeĢidi vardır: Monostable (tek kararlı) ve bistable (flipflop veya tetikleyici). Monostable multivibratörlerin tek bir kararlı hali, bistable

multivibratörlerin iki kararlı hali vardır.

Multivibratörlerde transistör yükseltici olarak kullanılır. Transistörün devreye bağlanıĢ

Ģekline göre bunlar kollektörü veya emitörü çiftlenmiĢ multivibratör ismini alırlar. Bu

deneyimizde biz yalnızca astable (serbest) ve kollektörü çiftlenmiĢ multivibratörü

inceleyeceğiz.

KOLLEKTÖRÜ ÇĠFTLENMĠġ MULTĠVĠBRATÖRÜN ÇALIġMASI

ġekil 1.8 de kollektörü çiftlenmiĢ bir multivibratör verilmiĢtir. Q1 ve Q2 NPN tipi

transistörlerdir. Kollektörler RL1 ve RL2 dirençleri üzerinden VCC kaynak gerilimiyle

beslenmektedir. R1 ve R2 dirençleri ise transistörlerin baz denetlemesi içindir.

ġimdi, Q1 transistörünün kollektörünü C1 kondansatörü yoluyla Q2 nin bazına, Q2 nin

kollektörünü ise, C2 yoluyla Q1 in bazına bağlayalım. Q1 in kollektöründeki herhangi bir

gerilim değiĢmesi C1 yoluyla Q2 nin bazına, Q2 kollektöründeki herhangi bir gerilim

değiĢmesi ise C2 yoluyla Q1 in bazına iletilecektir. Burada C1 ve C2 kondansatörleri

geribesleme iĢini üstlenmiĢtir.

RL1

R2

R1

C1

RL2

C2

Vcc

ÇIKIS 1

Q2

Q1

ÇIKIS 2

ġekil 1.8

Multivibratördeki iki devre birbirlerine göre simetrik seçilmiĢ olsunlar. Yani, Q1 ve Q2

transistörleri aynı tip karakteristiğe sahip, ve C1 = C2, R1 = R2, RL1 =RL2 seçilmiĢ olsunlar.

Transistörün kollektörlerinden VCC gerilimi uygulayalım. Baz uygun denetlemede olduğu için

transistörler iletimde olacaktır. Ancak her iki kollektör akımının birbirinin aynısı olacağını

12

söyleyemeyiz. Ġlk gerilimi uygulama anındaki bu küçük akım farkı Ģimdi anlatacağımız

biçimde devreyi salınıma sürükleyecektir.

Farz edelim ki, Q1 den Q2 ye göre daha fazla akım geçsin. Bu durumda Q1 in

kollektörü Q2 ye göre daha alçak gerilimde olacaktır. Bu gerilim farkı C1 yoluyla Q2 nin

bazına iletilecek ve böylelikle ileri baz gerilimi azalacaktır. Dolayısıyla Q2 nin kollektör akımı

azalacak ve gerilim daha yüksek olacaktır. Bu gerilim değiĢmesi de C2 yoluyla Q1 in bazına

iletilecektir. Q1 in baz akımı artacak ve buna bağlı olarak da kollektör akımı artacak, fakat

kollektör gerilimi azalacaktır. Bu gerilim azalması C1 yoluyla Q2 nin bazına iletilecek ve

iĢlem sırasıyla bu kollektör geriliminin azalıp artması Ģeklinde sürüp gidecektir. Çok kısa

aralıklarla bir transistörün kollektöründen diğerinin bazına giden bu geri besleme darbeleri,

bir transistörü akım doyumu noktasına sürerken diğerinin akımını kesecektir. Örneğin Q1

doyum noktasında iletim yaparken Q2 kesilimde olacaktır. Bu durumda Q1 e açık, Q2 ye de

kapalı diyoruz.

Q1 açık, Q2 kapalı kalma süresi devre elemanlarının belirlediği zaman sabitiyle

belirlenir. Bu değer yaklaĢık olarak C1R2 veya C2R1 kadardır. Bu zaman aralıklarıyla Q1 açık

Q2 kapalı, bir R1C2 kadar sonra da Q1 kapalı Q2 açık olacaktır.

Burada, multivibratör dalga Ģekillerinin nasıl meydana geldiği üzerinde duracağız.

Sadece dalga Ģeklinin periyodik kare dalga benzeri darbeler Ģeklinde olacağını bilelim yeter.

(Bu durum simetrik multivibratör içindir. Simetriklik bozulduğu zaman Ģekilde bozulacaktır.)

Simetrik multivibratörde her iki transistörün açık-kapalı zamanları birbirine eĢittir, (t1 = t2).

Q1 transistörünün kollektöründeki dalga Q2 kollektörüne göre 180 faz ile oluĢur. Yani iki

transistörün dalga Ģekli 180 faz ile oluĢur.

Multivibratörlerin tam bir periyodu T = t1 + t2 dir. Frekans ise bunun tersi, yani

f

1

t1 t 2

olacaktır. Pratik bir ifade olarak t1 ve t2 zaman sabitleri,

t 1 0,707 C1 R 2

ve

t 2 0,707 C 2 R 1

olarak bulunur. 0,707 (-3dB) katsayısı kondansatörün dolma veya boĢalma süresinin %50 sine

ulaĢması için gerekli bir katsayıdır.

SĠMETRĠK OLMAYAN MULTĠVĠBRATÖR

Eğer multivibratör devresinde, her iki zaman sabitini farklı kılacak bir değiĢiklik

yaparsak dalga Ģekli simetrik olmayan (fakat periyodik) bir çıkıĢ elde ederiz. Bu değiĢiklik R1,

R2 ve C1, C2 elemanlarından birinin değeri değiĢtirilerek yapılır. Bunlardan birisinin

değiĢmesiyle zaman sabiti de değiĢecektir. Örneğin; R1=10k, R2=100k ve C1=C2=0.01µF

alalım. C1R2 zaman sabiti C2R1 zaman sabitinden on defa daha fazla olacaktır ve çıkıĢ dalga

Ģekli de simetrikliğini kaybedecektir. Bu multivibratörlerde zaman sabiti, simetrik

multivibratörlerde olanın aksine daha karmaĢık metotlarla bulunacaktır. Onun için frekans

bağıntısını burada vermeyeceğiz. Deneysel sonuçla yetineceğiz.

ARAÇLAR

Güç kaynağı.

Osiloskop.

Dirençler; 0,5 Watt 2 tane 6,8k, 10k, 2 tane 100k ve 500 k değiĢken direnç.

Kondansatörler; 2 tane 0,01F.

Transistör; 2tane BC337 veya eĢdeğeri.

13

DENEYLER

ġekil 1.9 deki devreyi kurunuz.

RL1

R2

R1

RL2

6.8kohm

100kohm

100kohm

6.8kohm

C1

C2

Vcc

6V

0.01uF

0.01uF

ÇIKIS 1

Q2

Q1

ÇIKIS 2

BC337AP

BC337AP

ġekil 1.9.

Tablo 1.5 de verilen test noktalarını gözleyerek uygun yerleri doldurunuz.

Test noktaları

Q1 Kollektörü

Dalga Ģekli

VT-T

Q1 Bazı

Q2 Kolektörü

Q2 Bazı

Tablo 1.5

Multivibratörün frekansını, her iki transistör için ölçerek tabloda ilgili yerlere yazınız. Ayrıca

metinde verilen bağıntıdan hesapladığınız zaman sabiti ve frekansı karĢılaĢtırınız.

Frekans

Ölçülen

Hesaplanan

Tablo 1.6 (a)

Frekans

Ölçülen

Hesaplanan

t1

t2

t1

t2

Tablo 1.6 (b)

SĠMETRĠK OLMAYAN MULTĠVĠBRATÖR

Aynı devrede R2 direnci yerine bir 10k ve buna seri bağlı 500k değiĢken direnç

takınız. DeğiĢken direnci minimum konuma alınız.

14

Güç kaynağını çalıĢtırarak Tablo 3 de verilen test noktalarındaki gözlemlerinizi ilgili

yerlere iĢleyiniz. (Ģekil çizilecek) Multivibratörün frekansını ölçünüz ve kaydediniz.

Test noktaları

Dalga Ģekli

R4 min

R4 max

VT-T

Frekans

Q1 Kollektörü

Q1 Bazı

Q2 Kolektörü

Q2 Bazı

Tablo 1.7

DeğiĢken direnci yavaĢ yavaĢ maksimuma alırken dalgadaki değiĢmeyi gözleyiniz. R4

maksimum iken aldığınız ölçümleri Tablo 1.7 de yerlerine kaydediniz.

SORULAR

1. Multivibratörde PNP transistör kullanarak bir devre de siz çiziniz.

2. Bir astable (kararsız) multivibratörün bazlarındaki ve kollektörlerindeki zamana bağlı

dalga Ģekillerini çiziniz.?

3. Bir astable multivibratördeki karĢılıklı her iki kuplaj kapasitörlerini değeri 2.2nF ve baz

dirençleri 47k dur. TitreĢim frekansı nedir?

15

DENEY NO

:EII-2

DENEYĠN ADI :FARK YÜKSELTEÇLERĠ (DIFFERENTIAL AMPLIFIERS)

DENEYĠN AMACI

: Fark yükselteçlerinin öğrenilmesi ve yükselteçlerde giriĢ-çıkıĢ

iĢaretlerinin gözlenmesi.

ÖN BĠLGĠ:

Fark yükselteçleri (FY) (Differential amplifiers) genellikle doğrudan giriĢli yükseltici

tüm devrelerde kullanılmaktadır. Bu yükselteçlerin yapımı hassasiyet gerektirdiğinden, tüm

devrelerde iyi sonuçlar vermektedir. Fakat ayrı ayrı elemanlarla da iyi sonuç verenler

yapılabilir. Biz bu deneyimizde, ayrı ayrı elemanlarla yapılan fark yükselteçlerini

inceleyeceğiz.

ġekil 2.1 de Ģeması verilen fark yükselteci (kısaca FY diyeceğiz) görüldüğü gibi aynı

tip iki transistörden meydana gelmiĢtir. Ġki ayrı giriĢi ve iki ayrı çıkıĢı vardır. Devre tamamen

simetriktir. Transistörler aynı karakteristiğe sahiptir. Emitör direnci RE her iki direnç için

ortaktır. Kollektör yük dirençleri de eĢittir, RL1 = RL2. Ayrıca her iki giriĢ devresi de birbirinin

aynısıdır (R1 = R2).

+Vcc

RL2

RL1

ÇIKIS 2

ÇIKIS 1

Q1

Q2

R1

R2

RE

V1

V2

-V

EE

ġekil 2.1. Fark yükseltici prensip devresi.

Yükselteçte çıkıĢ sinyali, giriĢ sinyallerinin farkıyla doğru orantılıdır. Orantı katsayısına A

dersek (gerilim kazancı) Vçıkış A (V1 V2 ) olur. Bu eĢitlikten hemen Ģu iki önemli sonucu

çıkarabiliriz:

a) Her iki giriĢ sinyali aynı fazda ve aynı genlikte ise çıkıĢ SIFIR olur.

Vçıkış A (V1 V2 ) 0

(V1 V2 )

Bu duruma ―Ortak hal iĢlemi‖ (common mode operation) diyeceğiz. Ortak halde giriĢ

sinyalleri devre içinde toplanarak yok edilir ve çıkıĢ yoktur. Fakat gerçekte FY’nin her iki

kısmı tamamen simetrik olamayacağından giriĢ sinyalleri dengelenemez ve küçük genlikte bir

çıkıĢ olur. Bu dengesizliğin baĢka elemanlarla giderilmesi gerekir (OFFSET iĢlemi).

b) Her iki giriĢ sinyalinin genliği eĢit fakat zıt fazda (180 faz) ise (V1 = -V2) çıkıĢ

gerilimi,

Vçıkış A{(V1 (V1 )} 2V1 A 2V2 A

olacaktır. Bu duruma farklı çıkıĢ hali diyeceğiz (non-common mode operation).

TEK GĠRĠġLĠ FARK YÜKSELTĠCĠ

Bir FY genellikle çift giriĢli olarak kullanılır. Fakat Ģekil 2.2 de görüldüğü gibi tek

giriĢli de yapılabilir. Ayrıca, çıkıĢlar da her iki transistör kollektörüyle toprak arasından

16

alınarak çift yapılabilir. Yükseltecin çalıĢmasını anlayabilmek için önce tek giriĢli FY’yi ele

alalım.

+Vcc

GĠRĠġ 1

RL2

RL1

ÇIKIġ 1

ÇIKIS 1

Q1

ÇIKIS 2

Q2

R1

R2

ÇIKIġ 2

RE

V1

-V

EE

ġekil 2.2. Tek giriĢ-çift çıkıĢ FY.

ġimdi bir sinüs sinyalin giriĢe uygulandığını düĢünelim, ġekil2.2. Q1’in bazı

sürüleceğinden, kollektöründe giriĢ sinyaliyle zıt fazda büyütülmüĢ bir sinyal gözlenecektir

(ÇıkıĢ 1). RE direncinin üst noktasından alınan sinyal, giriĢ sinyaliyle aynı fazda ve yaklaĢık

aynı genlikte bir sinyal olur. Bu sinyal aynı zamanda Q2 transistörünün emitör-baz (toprak)

arasındaki sinyalin görüntüsüdür. Bu sinyalin Q2 transistörünün emitör-baz arasındaki

sinyalden 180 faz farkı olacaktır. Bir transistör için önemli olan baz (base)-emitör eklemi

üzerine düĢen sinyaldir. Dolayısıyla bu sinyal, Q2 tarnsistörünün kollektörüyle büyütülerek

ÇıkıĢ 2’yi oluĢturur. Burada çıkıĢ 2 sinyali ile çıkıĢ 1 sinyalleri zıt fazda ve aynı genliktedir.

Yani tek giriĢli FY, tek giriĢli fakat zıt fazda çift çıkıĢlı bir yükselticidir.

Eğer çıkıĢ sinyalini Q1 ve Q2 kollektörleri arasından alıyorsak bu çıkıĢ, giriĢ sinyaliyle

aynı fazda büyütülmüĢ olacaktır. Bu çalıĢma halinde, yükseltici TERS ÇEVĠRMEYEN

+VCC

RL2

RL1

ÇIKIŞ

Q1

Q2

R1

R2

RE

V1

-VEE

YÜKSELTĠCĠ ve V1 giriĢi de ters çevirmeyen giriĢ olarak isimlendirilir.

17

ġekil 2.3. Ters Çevirmeyen Yükseltici

Eğer Q1 baz direnci topraklanır ve Q2 bazından bir giriĢ sinyali uygulanırsa ve çıkıĢ

sinyalini de Q1 ve Q2 kollektörleri arasından alınırsa, çıkıĢ sinyali giriĢ sinyali ile zıt fazda

(180 faz) büyütülmüĢ olacaktır. Bu duruma TERS ÇEVĠREN YÜKSELTĠCĠ ve Q 1 giriĢine

de ters çeviren giriĢ denmektedir, ġekil 2.4.

+VCC

RL2

RL1

ÇIKIŞ

Q1

Q2

R1

R2

RE

V2

-VEE

ġekil 2.4. Ters çeviren Yükselteç.

FARKLI HAL GĠRĠġĠ (NON-COMMON MODE OPERATĠON)

18

+VCC

ÇIKIŞ

RL2

RL1

Q1

Q2

R1

R2

RE

V1

V2

-VEE

ġekil 2.5. Farklı Hal Yükseltici

FY’nin iki giriĢinden de sinyal uygulandığını düĢünelim. V1 giriĢ sinyali pozitif iken

V2 giriĢ sinyali negatif olsun (zıt fazda, aynı genlikte). Bu iki giriĢ sinyali RE direnci uçlarına

eĢit genlikte zıt fazda ulaĢacaklarından sinyaller burada birbirlerini yok ederler. Q1

kollektöründe oluĢan gerilim V1 ile zıt fazda ve büyütülmüĢ, Q2 kollektöründeki gerilim de V2

gerilimiyle zıt fazda ve büyütülmüĢ olacaktır. Dolayısıyla kollektördeki çıkıĢ sinyalleri zıt

fazlı ve büyütülmüĢ olacaktır. Eğer çıkıĢ, Q1 ve Q2 kollektörleri arasından alınırsa, elde

edilecek sinyalin genliği,

Vçıkış A{(V1 (V1 )} 2V1 A 2V2 A

olacaktır. ÇıkıĢ sinyalleri, kollektörlerle toprak arasından ayrı ayrı da alınabilir. Tek tek

çıkıĢlar, birbirlerine göre zıt fazda ve eĢit genlikte olur.

Vçıkış1 AV1 AV2

(V1 = -V2)

Vçıkış 2 AV2 AV1

ORTAK HAL ĠġLEMĠ (COMMON MODE OPERATĠON)

FY giriĢlerine aynı sinyali uygulayalım, ġek. 6. RE direnci uçlarında oluĢacak gerilim

aynı fazda olacağından, iki giriĢ sinyalinin toplamı kadar genlikte bir sinyal oluĢur. Bu sinyal

kendisine zıt fazda olan kollektör gerilimini söndürecektir ve o da diğer kollektör gerilimini

söndürecek ve çıkıĢ sinyali alınmayacaktır.

+VCC

RL2

RL1

ÇIKIŞ: 0

Q1

R1

Q2

R2

RE

-VEE

Vg

19

ġekil 2.6. Ortak Hal giriĢi.

ÇıkıĢ sinyali,

Vçıkış A (V1 V2 ) 0

olacaktır.

(V1 V2 )

ORTAK HAL BASTIRMA ORANI (COMMON MODE REJECTION RATIO, CMRR)

Bir FY’de farklı giriĢ halinde yüksek kazançlı çıkıĢ ve ortak giriĢ halinde ise çok

düĢük kazançlı çıkıĢ istenir. Farklılık halinde yükseltici kazancına A FH, ortak hal kazancına da

AOH diyelim. Ortak hal bastırma oranı,

A

CMRR FH

AOH

olarak verilir. Bu oran FY’nin çalıĢma etkinliğini ve verimini gösteren bir ölçüdür ve çok

büyük olması istenir.

RE DĠRENCĠNĠN FY ÜZERĠNE ETKĠSĠ

Ortak hal giriĢi için RE emitör direnci, söndürücü, ya da negatif geribesleme iĢlemi

yapar. RE direncinin büyümesiyle ortak halde negatif geribesleme de büyür ve sonuçta ortak

hal sinyallerine karĢı bastırma etkisi de artar. Bunun için RE direncinin büyük olması tercih

edilir. Çünkü yukarıda anlatılan sebeplerden dolayı CMRR de artar.

RE direnci istenen büyüklükte yapılamaz, bir üst sınır vardır. Emitör akımını

belirleyen bu dirençtir. Bu akım yaklaĢık olarak

V

I E EE

RE

olacaktır. RE nin artmasıyla her iki emitör ve kollektör akımı azalır. Ancak bu akım azalması

istenmez. Bunun için çoğu uygulamalarda ġek. 7 de verilen bir Q3 transistörü eklenir. Bu

transistör istenen yüksek akımı verirken büyük direnç gösterir. RE direnci bu uygulamada

küçük tutulur.

+VCC

RL2

RL1

Q1

Q2

R1

V1

Q3

R3

R4

RE

-VEE

ġekil 2.7.

FY DEVRE SEMBOLÜ

20

R2

V2

ġimdiye kadar gösterilen karmaĢık devreler yerine, FY’ler standart yapıda

olduklarından tek bir sembolle gösterilir. ġekil 2.8 de (-) iĢaretli olan ―TERS ÇEVĠREN

GĠRĠġ‖, (+) iĢaretli olan ise ―TERS ÇEVĠRMEYEN GĠRĠġ‖ tir.

Ter s Çeviren

ÇIKIS

2

3

Ter s Çevirmeyen

1

ġekil 2.8. FY devre Sembolü

ARAÇLAR

Çift çıkıĢlı güç kaynağı

Sinyal üreteci, Osiloskop, Voltmetre

Dirençler, 2x1k, 8.2k, 2x10k

Transistör, 2xBC337 ve eĢdeğeri

Transformatör, 2x12 Volt ac

DENEYLER

I- TEK GĠRĠġLĠ FARK YÜKSELTĠCĠ

1- ġekil 2.9 daki devreyi kurunuz.

2- VCC gerilimini 10 V yapınız.

3- Voltmetre ile Q1 (veya Q2) kollektörüyle toprak arasındaki gerilim 5 Volt oluncaya kadar

VEE’yi (9 Volt civarında) ayarlayınız. (Eğer 5 volt olmuyorsa Vcc kaynağını da

değiĢtirebilirsiniz.),

4- Sinyal üretecinden çok küçük genlikli ( 50mVT-T) bir sinüs sinyali giriĢe uygulayınız.

5- Osiloskopla giriĢ sinyalini ölçerek kaydediniz (Tablo 1).

6- Osilioskop giriĢlerini Q1 ve Q2 kollektörleri ile toprak arasına bağlayarak her iki çıkıĢ

sinyalini gözleyiniz. Tepeden tepeye genlikleri ve faz farklarını ölçerek Tablo 1 de yerlerine

yazınız. Faz ölçümü için Lissajous yöntemini kullanabilirsiniz.

7- Yine osiloskopla her iki transistorün baz sinyallerini gözleyerek Tablo 1 de yerlerine

yazınız. RE direncinin ucundaki sinyalin genliğini ölçerek giriĢ sinyaliyle karĢılaĢtırınız.

8- Her iki çıkıĢ gerilim kazancını hesaplayarak yine Tablo 1’e yazınız.

9- ġimdide osiloskobun tek bir kanalıyla çıkıĢ 1 ve çıkıĢ 2 arası gerilim farkını ölçerek bu

durum için kazancı bulunuz. Öteki bulduğunuz kazançla karĢılaĢtırınız.

RL1

RL2

10kohm

10kohm

10V

V cc

ÇIKIS 1

Q1

BC337AP

ÇIKIS 2

Q2

BC337AP

9V

R1

R2

1kohm

1kohm

RE

50mV 1kHz 0Deg

8.2kohm

V1

21

V EE

ġekil 2.9.

Tablo2.1

GiriĢ

Baz 1

ÇıkıĢ 1

Baz 2

VRE

ÇıkıĢ 2

Faz

Kazanç

ġekil

VT-T

X

ÇıkıĢ 1 için

ÇıkıĢ 1-ÇıkıĢ 2

arası

ÇıkıĢ 2 için

II- FARKLI GĠRĠġ HALĠ

Masanızda bulunan transformatörle ġekil 2.10’daki değiĢikliği yapınız.

Transformatörün Ģekildeki gibi bağlanmasının sebebi 1 ve 2 giriĢlerinde 180 faz farkı olan

sinyallerin oluĢumunu sağlamaktır.

Birinci deneydeki sırayı takip ederek Tablo 2.2’yi doldurunuz. Tek giriĢli FY ile farklı

giriĢli FY arasındaki en belirgin farkları maddeler halinde özetleyiniz.

RL1

RL2

10kohm

10kohm

10V

V cc

ÇIKIS 1

Q1

ÇIKIS 2

Q2

BC337AP

BC337AP

9V

R1

R2

1kohm

1kohm

1

V EE

RE

8.2kohm

50mV 1kHz 0Deg

2

Vg

ġekil 2.10.

Tablo 2.2

GiriĢ

Baz 1

ÇıkıĢ 1

Baz 2

VRE

ÇıkıĢ 2

Faz

VT-T

Kazanç

ġekil

X

ÇıkıĢ 1 için

ÇıkıĢ 2 için

ÇıkıĢ 1-ÇıkıĢ 2

arası

III- ORTAK GĠRĠġ HALĠ

22

Devrenin giriĢ kısmından transformatörü sökerek ġekil 2.11 deki değiĢikliği yapınız.

Sinyal üreteci 1kHz, maksimum 50mVT-T olacaktır. Tablo 2.3’te istenen ölçümleri yaparak

tabloyu doldurunuz.

RL1

RL2

10kohm

10kohm

V cc

10V

ÇIKIS 1

Q1

ÇIKIS 2

Q2

BC337AP

BC337AP

9V

R1

R2

1kohm

1kohm

V EE

REE

8.2kohm

50mV 1kHz 0Deg

Vg

ġekil 11.

Tablo3

GiriĢ

Baz 1

ÇıkıĢ 1

Baz 2

VRE

ÇıkıĢ 2

Faz

VT-T

ġekil

X

ÇıkıĢ 2 için

ÇıkıĢ 1-ÇıkıĢ 2

arası

Kazanç

ÇıkıĢ 1 için

23

DENEY NO

DENEYĠN ADI

DENEYĠN AMACI

: EII-3

:DOĞRUSAL TÜMDEVRELER (LINEER INTEGRATED

CIRCUITS, IC)

: Doğrusal Tümdevrelerin tanıtılması.

ÖN BĠLGĠ:

Çok büyük bir hızla geliĢen elektronik ve yarı-iletkenler teknolojisi, oldukça büyük ve

karmaĢık devrelerin yapımını zorunlu kılmıĢtır. Özellikle bilgisayar endüstrisinde, 1950’lerin

tüplerle yapılmıĢ, dört iĢlemi güç bela yapabilen birinci nesil dev bilgisayarlarla mukayese

edildiğinde, hacim küçülmesinde, karmaĢıklıkla ve iĢlem sayısı ve hızında akıl almaz bir

ilerleme olmuĢtur. Ġkinci nesil bilgisayarlarda hacim biraz küçülmüĢ, iĢlem kapasitesi ve hız

artmıĢtır, ancak bunlar da hala çok büyük ve yavaĢtır. Bu nesil bilgisayarlar transistör ve

diyotlardan yapılmaktaydı. Üçüncü nesil bilgisayarların esas elemanları IC’ler transistörlerle

ve diğer klasik devre elemanlarıyla yapılabilecek bir masa büyüklüğündeki devreleri bir toplu

iğne baĢı kadar alana sığdırarak yapılırlar.

IC’ler yalnız bilgisayarlarda değil, haberleĢme, radyo, TV, vs. gibi çeĢitli endüstri

alanlarında da yaygın olarak kullanılmaktadır. Daha önceki deneylerimizde gördüğümüz

çeĢitli yükselticiler, örneğin, daha çok daha verimli ve daha küçük olarak imal edilmektedir.

Bir tümdevre, aktif ve pasif elemanların bir bütün halinde özel tekniklerle küçük bir

alana yerleĢtirilmesiyle oluĢmuĢlardır. Aktif elemanlar; transistörler ve diyotlar, pasif

elemanlar ise dirençler ve kondansatörlerdir. Bir tümdevre artık ayrı-ayrı elamanlar olarak

değil, bir bütün halinde adlandırılır ve kullanılır.

Bundan sonra yapacağımız deneylerde yalnızca doğrusal tümdevreler üzerinde

duracağız, sayısal tümdevreler daha ileri safhalarda incelenecektir.

Bir tümdevre çeĢitli bağlantı ve konfigürasyonlar için çok sayıda terminale (bacak)

sahiptir. Örneğin UA741 tümdevresinin 8 bacağı vardır. Bu bağlantıların uygun

kullanılmasıyla, doğrusal tümdevreler pek çok değiĢik amaç için kullanılabilir. Tümdevrelerin

kullanılmasını çeĢitlendiren unsurlar, ona dıĢardan bağlanan elemanlardır.

Tümdevreler birkaç değiĢik yapıda ve kılıf Ģeklinde üretilirler. Seramik veya metal

olabilen bu kılıf Ģekilleri, TO-5, yapısında, düzgün kılıflı yapıda (flatpack) veya çift sıra

bacaklı (dual in-line) yapıda olabilir (ġekil 3.1.).

TO-5

Düzgün kılıf (flat pack)

ġekil 3.1.

Çift sıra bacaklı (dual in line)

ĠġLEMSEL YÜKSELTEÇLER (IY) (OPERATIONAL AMPLIFIERS, OPAMP)

ĠĢlemsel yükselteçler, çok yüksek kazançlı, doğrudan bağlantılı fark yükselteçleridir.

Daha önce gördüğümüz fark yükselteçlerinin geliĢtirilmiĢ ve tümdevre haline getirilmiĢ

Ģeklidir. Bu tümdevreler, bilgisayarlarda, toplama çıkarma, türev ve integral iĢlemleri için

geliĢtirilmiĢtir ve günümüzde çok amaçlı bir doğrusal yükseltici olarak kullanılmaktadır. Bir

IY’nin çalıĢması ona dıĢarıdan bağlanan elemanlarla kontrol edilir.

ġekil 3.2 de IY devre Ģeması görülmektedir. Önceki deneyde öğrendiğiniz fark

yükselticinin aynısı olarak iki giriĢe sahiptir. Bu giriĢler, TERS ÇEVĠREN GĠRĠġ (─) ve

TERS ÇEVĠRMEYEN GĠRĠġ (+) olarak iĢaretlenmiĢlerdir. Ters çeviren giriĢten uygulanan

bir gerilim, çıkıĢta iĢareti değiĢmiĢ ve büyümüĢ olarak gözlenir (Örneğin, pozitif bir giriĢ

24

gerilimi, çıkıĢta büyütülmüĢ negatif bir gerilim olarak gözlenir.). Ters çevirmeyen giriĢten

uygulanan bir sinyal ise çıkıĢtan aynı iĢaretle büyütülmüĢ olarak gözlenir.

Ters çeviren giriĢ

ÇıkıĢ

Ters çevirmeyen giriĢ

ġekil 3.2. ĠĢlemsel Yükselteci Sembolü

DıĢarıdan herhangi bir kontrol elemanı bağlanmadan, giriĢe bir gerilim

uygulandığında çıkıĢtan çok büyük bir gerilim elde edilecektir. IY’nin bu durumundaki

gerilim kazancına AÇIK HALKA KAZANCI (KA) denmektedir. Bu değer genellikle 20000

veya daha büyüktür. Yani açık halka durumunda giriĢ ve çıkıĢ gerilimleri arasında

Vç K AVg bağıntısı vardır.

Vg

KA

VÇ

Açık halka kazancı çok büyük olduğundan giriĢe uygulanan gerilim çok küçük

olmalıdır. Burada bir noktaya daha değinelim; çıkıĢ gerilimi IY besleme geriliminden daha

büyük olamaz ve normal bir IY’nin besleme gerilimi 15 V civarındadır. Bu durumda çıkıĢ

gerilimi 15 V’dan daha büyük olamaz. Örneğin açık halka kazancı 30000 olan bir IY

çıkıĢından 15 V alabilmek için, giriĢe,

Vç

15

Vg

0.5x103 0.5mV

30000

30000

gerilim uygulanmalıdır.

IY’lerin giriĢ empedansları çok yüksek (birkaç M mertebesinde) olduğundan (+) ve

(─) giriĢ uçları arasında potansiyel farkı sıfır olur. Çok yüksek giriĢ empedansı sebebiyle (+)

ve (─) giriĢ uçları arasından akan akım pratikte nanoamper seviyesindedir. Bu yüzden IY’ler

gerilime duyarlıdır ve çoğu uygulamalarda IY’ye giriĢten akım geçmediği kabul edilir.

GERĠ BESLEME ve TERS ÇEVĠREN YÜKSELTEÇ

Her ne kadar, bir IY’nin açık halka kazancı çok büyükse de, bunu dıĢarıdan bağlanan

elemanlarla istediğimiz değere ayarlama imkânımız vardır. Bu iĢleme geri besleme

denmektedir. ġekil 3.3 te verilen bağlantıyı ele alalım. R1 giriĢ direnci, R2 ise geri besleme

direncidir.

i2

R1

A

Vg

i1

R2

Vi

VÇ

ġekil 3.3. Negatif geri-besleme

25

Ters çeviren giriĢten bir Vg geriliminin uygulandığını düĢünelim. IY’nin giriĢ empedansı çok

büyük olduğundan akımın yalnızca R2 direnci üzerinden geçtiğini varsayacağız. Bu durumda

A noktası için Kirchoff Akım yasası;

i1 i2 den,

Vg Vi

V V

ç i

R1

R2

elde edilir. Bu eĢitliği yeniden düzenleyelim.

R

2 (Vg Vi ) Vç Vi

R1

olur. Vi 0 alınırsa kapalı halka kazancı KK,

Vç

R2

KK

Vg

R1

olur. Bu formüle göre eğer R1 = R2 olarak seçilirse yükseltecin kazancı ─1’e eĢit olur. Bu gibi

durumlarda, yükselteç, giriĢine uygulanan sinyali yükseltmeden sadece iĢaretini değiĢtirerek

çıkıĢa aktarır. Kazanç formülündeki (─) iĢareti giriĢle çıkıĢ arasında 180 faz farkı olduğunu

gösterir. R1 ve R2 dirençleri ile yükseltecin kapalı halka devre kazancı ayarlanabilir. Bu

bağlantıya göre kapalı halka kazancı açık halka kazancından daha küçüktür. Fakat devrenin

çalıĢması kapalı halka kazancında daha kararlıdır. Geri beslemeli kazanç geri beslemesiz

kazançtan daha küçük olduğundan kullanılan geri besleme NEGATĠF GERĠ BESLEME dir.

Pozitif geri besleme olsaydı, geri beslemeli kazanç, geri beslemesiz kazançtan daha büyük

olurdu.

TERS ÇEVĠRMEYEN YÜKSELTEÇ

ġekil 3.4 te görüldüğü gibi giriĢ sinyali IY’nin faz çevirmeyen (+) giriĢine

uygulanmıĢtır. Dolayısıyla giriĢ ve çıkıĢ sinyalleri arasında faz farkı olmaz.

Ġdeal bir IY’nin giriĢ empedansı sonsuz olması sebebiyle (+) ve (─) giriĢ uçları

arasındaki akım sıfır olacağından bu uçlar arasındaki potansiyel farkı sıfır 0 Volttur.

R2

R1

A

Vi

+V

+

-V

VÇ

Vi = 0

R2

VVgg

Vg

R1

VÇ

ġekil 3.4. Ters Çevirmeyen Yükselteç ve eĢdeğer devresi

Vi = 0 olduğundan giriĢ gerilimi R1 üzerindeki gerilime eĢittir. Dolayısıyla R1 ve R2 gerilim

bölücü gibi davranacağından giriĢ gerilimi,

R1

Vg

Vç

R1 R 2

olur. Bu denklemi yeniden düzenlersek,

Vç R1 R 2

R

1 2 KK

Vg

R1

R1

26

bulunur. Eğer bu devrede R1 direncini sonsuz ve R2 direncini de sıfır alırsak elimize kazancı

+1 olan gerilim izleyici geçer, ġek.5. Bu devrenin giriĢ empedansı çok yüksek, çıkıĢ

empedansı da düĢük olduğu için empedans uyumunda kullanılır. Empedans uyumu yapılacak

devre katları arasında maksimum enerji transferinin gerçekleĢebilmesi için bir katın çıkıĢ

empedansının diğer katın giriĢ empedansına eĢit olması gerekir.

VÇ

Vg

ġekil 3.5. Gerilim izleyici

Faz çevirmeyen yükselteç ile faz çeviren yükselteç arasındaki farklar Ģunlardır:

Faz çevirmeyen yükseltecin kazancı, faz çeviren yükselteçten 1 fazladır ve daima birden

büyüktür.

Faz çevirmeyen yükseltecin giriĢ empedansı IY (OP-AMP) giriĢ empedansına eĢit olup

çok yüksektir. Faz çeviren yükseltecin giriĢ empedansı ise R1 direnci kadardır.

Faz çevirmeyen yükselteçte giriĢ ve çıkıĢ iĢaretleri aynı fazdadır. Faz çeviren

yükselteçte ise giriĢ ve çıkıĢ sinyalleri arasında 180 faz farkı vardır.

ĠġLEMSEL YÜKSELTECĠN ÖZELLĠKLERĠ

Üretici kataloglarında, üretilen IY’nin çeĢitli uygulamalarıyla ilgili gerekli tüm teknik

bilgiler mevcuttur. Ayrıca, pek çok temel elektronik kitaplarında ve değiĢik kaynaklarda

IY’ler hakkında ayrıntılı bilgiler kolaylıkla bulunabilir. Biz burada yalnızca, deneyimizde

önemli olan bazı temel özellikleri sıralayacağız.

IY’ler askeri ve endüstri amaçlı olarak iki ayrı kategoride üretilirler. Bunlar hem çift

sıra bacaklı ve hem de metal kılıflı (TO-5) olarak üretilir. ġekil 6 da çift sıra bacaklı bir 741

tümdevrenin bacak bağlantıları verilmiĢtir.

1. GiriĢ offset

2. Ters çeviren giriĢ (─)

8 7 6 5

3. Ters çevirmeyen giriĢ (+)

4. ─VEE (Eksi besleme gerilimi)

5. GiriĢ offset

6. ÇıkıĢ

ĠĢaret 1 2 3 4

7. +VCC (Artı besleme gerilimi)

noktası

8. BoĢ

ġekil 3.6.

Bir 741 IY (OP-AMP) için bazı teknik özellikler aĢağıya sıralanmıĢtır:

-Besleme gerilimi

: 18 Vmax (15V nominal)

-Güç harcaması

: 500 mWmax

-Farklılık giriĢ gerilimi

: 30 Vmax

-ÇalıĢma sıcaklığı

: 0─70C

27

-GiriĢ bias akımı

: 800 nA

-GiriĢ direnci

: 0.3─2 M

-GiriĢ gerilim aralığı

: 13 V

-Ortak hal bastırma oranı (CMRR)

: 90 dB

-ÇıkıĢ direnci

: 75

-ÇıkıĢ kısadevre akımı

: 25 mA

-Besleme akımı

: 2.8 mA

-Büyük sinyal kazancı

: 15000

-ÇıkıĢ gerilimi salınımı

: 13 V

ġimdi de bu terimlerden bazılarını açıklayalım.

- Farklılık giriĢ gerilimi: (+) ve (─) giriĢler arasına uygulanabilecek maksimum gerilimdir.

- GiriĢ bias akımı: ÇıkıĢ geriliminin sıfır olması halinde her iki giriĢten akan akımın

ortalamasıdır.

- GiriĢ direnci: GiriĢ terminallerinden birisinin topraklanması halinde, iki giriĢ terminali

arasındaki dirençtir.

- GiriĢ gerilim aralığı: IY’nin (Op-amp) fonksiyonunu tam yapabilmesi için her iki giriĢten

uygulanabilecek maksimum gerilimdir.

- Ortak hal bastırma oranı (CMRR): Farklılık gerilim kazancının ortak hal gerilim

kazancına oranıdır.

- ÇıkıĢ direnci: ÇıkıĢ terminali ile toprak arasındaki dirençtir.

- ÇıkıĢ kısadevre akımı: ÇıkıĢın toprakla kısadevre yapılması halinde akacak maksimum

çıkıĢ akımıdır.

- Besleme akımı: IY sıfır volt çıkıĢ verirken güç kaynağından IY’ye akan besleme

akımıdır.

- Büyük sinyal gerilim kazancı: Geri beslemesiz halde çıkıĢ gerilimi maksimum değerinin

diferansiyel giriĢ gerilimine oranıdır.

- ÇıkıĢ gerilim salınımı: ÇıkıĢın offset yapılmıĢ olması halinde, bozulma olmaksızın

maksimum çıkıĢ gerilimidir.

ARAÇLAR

Ġki çıkıĢlı güç kaynağı

Osiloskop, osilatör, voltmetre

Dirençler, 2x10k, 22k, 56k, 100k, 5.6k

Tümdevre, UA741 iĢlem yükselteci

DENEYLER

I- IY KAZANCI, TERS ÇEVĠREN YÜKSELTEÇ

1. ġekil 3.7 deki devreyi kurunuz.

2. RF ve RR dirençleri yerine önce 10k’luk dirençler takarak devreyi çalıĢtırınız.

Osiloskobunuzun iki kanalını da giriĢ ve çıkıĢ sinyallerini gözlemek için kullanınız.

GiriĢe 100mV ve 1kHz sinüs sinyali uygulayınız.

3. ÇıkıĢ sinyalinin tepeden tepeye değerini ölçerek Tablo 1’e kaydediniz.

4. Lissajous yöntemiyle sinyallerin faz farkını ölçerek kaydediniz.

5. ġimdi RF direnci yerine sırasıyla 5.6k, 22k, 56k, 100k dirençleri bağlayarak

aynı ölçümleri Tablo 3.1’de yerlerine yazınız.

28

RF

RR

+

7

2

10 V

6

VÇ

3

Vg

4

+

10 V

-

ġekil 3.7.

Tablo3.1

RR

10k

″

″

″

″

RF

10k

5.6k

22k

56k

100k

GiriĢ VT-T

100mV

″

″

″

″

ÇıkıĢ VT-T

Kazanç (Vç Vg )

Kazanç ( RF RR )

Faz

II- TERS ÇEVĠRMEYEN YÜKSELTEÇ

1. Devreyi ġekil 3.8 deki gibi değiĢtiriniz.

RF

RR

+

7

2

10 V

6

VÇ

3

4

+

Vg

10 V

-

ġekil 3.8.

2. Birinci kısımda takip ettiğiniz sırayı bu devre için de aynen tekrar ediniz. Sonuçları

Tablo 3.2’de toplayınız.

Tablo 3.2

RR

RF

10k 10k

″

5.6k

″

22k

″

56k

″

100k

GiriĢ VT-T

ÇıkıĢ VT-T

Kazanç (Vç Vg )

100mV

″

″

″

″

29

Kazanç (1

RF

)

RR

Faz

III- GERĠLĠM ĠZLEYĠCĠ

1. ġekil 3.9 daki devreyi kurunuz.

2

+

7

10 V

6

-

3

VÇ

4

+

Vg

10 V

-

ġekil 3.9.

2. Sinyal üretecinden, sırasıyla 100 mV, 500 mV ve 1 V gerilimleri sırasıyla yükselteç

giriĢine uygulayarak çıkıĢ gerilimlerini ölçünüz. Sonuçları Tablo 3.3’e kaydediniz.

Tablo 3.3

GiriĢ VT-T

100mV

500mV

1V

ÇıkıĢ VT-T

Kazanç (Vç Vg )

Faz

SORULAR

1. Bir faz çeviren yükselteç devresinde kazanç giriĢe göre nasıl değiĢir? Niçin?

2. Doğrusal bir iĢlem yükselteci devresinde elde edilen maksimum çıkıĢ sinyalinin tam

değerini ne belirler?

3. Bir ĠY nin doyum voltajı seviyeleri hangi aralıkta değiĢir? Niçin?

4. Gerilim izleyiciyi hangi devreden nasıl elde edersiniz?

30

DENEY NO

DENEYĠN ADI

:EII-4

:TOPLAMA, ÇIKARMA, TÜREV, ĠNTEGRAL VE

KIYASLAYICI DEVRELER

DENEYĠN AMACI

: ĠĢlemsel yükselteçle aritmetik toplama, çıkarma, integral,

türev ve kıyaslama, iĢlemlerinin yapılmasının öğrenilmesi.

ÖNBĠLGĠ

ĠĢlemsel yükselteçlerle yapılabilecek devre sayısı oldukça fazladır. Biz bu

deneyimizde temel sayılabilecek devreleri öğreneceğiz. Bunlardan önemli kabul

edebileceklerimiz, toplama iĢlemi, türev, integral alma iĢlemi ve kıyaslama iĢlemleridir.

TOPLAMA VE ÇIKARMA ĠġLEMĠ

Toplama iĢlemi analog bilgisayarlarda gerekli olan toplama ve çıkarma iĢlemleri için

hazırlanmıĢtır. ġekil 4.1 deki ters çeviren yükselteci ele alalım. Devredeki A noktası zahiri

veya sanal toprak (Virtual ground) olarak isimlendirilir. Yani bu noktada R1, R2, R3, . . .

dirençlerinden gelen akımlarla, geribesleme direnci Rf üzerinden gelen akımlar toplanarak

sıfır olacaktır (Kirchoff akım yasası).

i

i1

R1

i2

R2

i3

R3

i4

R4

V1

V2

V3

Rf

A

─

Vç

+

V4

ġekil 4.1.

A noktası için K.A.K yazılacak olursa

i1 i2 i3 i4 .........in i

V

V

V1 V2 V3 V4

........ N ç

R1 R2 R3 R4

RN

Rf

V

V V V V

Vç Rf ( 1 2 3 4 .............. N )

R1 R2 R3 R4

RN

olur. Buradan da görüldüğü gibi çıkıĢ gerilimi ters çevrilmiĢ olarak giriĢ geriliminin

toplamıdır. Bu giriĢleri –V1, –V2 gibi iĢaretleri değiĢtirilmiĢ olarak uyguladığımızda, çıkıĢ

diğer pozitif giriĢlerden bunların çıkartılması olacaktır.

Örnek: ġekil 4.2 devresinde V1 = 0.5 V, V2 = -1 V olsun. ÇıkıĢ gerilimini bulalım.

Rf = 6k

R1 = 1k

V1

V2

─

R2 = 3k

+

ġekil 4.2.

31

Vç

R

R

6k

6k

Vç f V1 f V2 (0.5V ) (1V )

R2

3k

1k

R1

Vç (3 2) 1V

Benzer bir örneği de birim kazanç için yapalım. Yani Rf R1 R2 olsun. Bu durumda

Vç (0.5V 1V ) 0.5V olacaktır. Görüldüğü gibi giriĢ gerilimleri çıkıĢta toplanarak

verilmektedir.

TÜREV ALMA ĠġLEMĠ

Elektronik devrelerde türev ve integral alma denildiği zaman biz kare ve üçgen

dalgaların birbirlerine çevrilmesini anlıyoruz. Çünkü kare dalga üçgen dalganın türevidir veya

üçgen dalga kare dalganın integralidir. Ayrıca sinüs ve kosinüs fonksiyonları birbirilerinin

türevi veya integralidir. Bizim devremiz de bu iĢlemleri yapmaktadır. ġekil 4.3 deki devreyi

ele alalım. GiriĢten bir üçgen dalga verilmiĢ olsun. ÇıkıĢ geriliminin nasıl olacağına bakalım.

Rf

iç

C

Vg

ig

─

A

+

Vç

ġekil 4.3. Türev alma devresi

A noktası için K.A.K yazılırsa,

ig iç

dir ve iç

Vç

olur. ig için de akım yük arasındaki türev bağıntısını aĢağıdaki gibi yazarız.

Rf

Kondansatör üzerinden geçen ig akımının değeri dq/dt dir. Burada q = C.V ve C de sabittir.

dVg

dq

ig

ve bu bağıntıda q yerine CVg yazılırsa, ig C

dt

dt

olur. Akımların eĢitliğinden de

dVg

dVg

V

ç C

veya Vç Rf C

Rf

dt

dt

türev bağıntısını buluruz.

Devrenin çıkıĢ formülünden de anlaĢıldığı gibi çıkıĢ gerilimi, giriĢ geriliminin türevi

ile orantılıdır ve türevleyici devre giriĢ iĢaretinin türevini, Rf.C sabitiyle çarparak çıkıĢına

aktarır. Formüldeki (-) iĢareti, devrenin ters çeviren giriĢten iĢlem yaptığını ve giriĢle çıkıĢ

arasında 180 faz farkı olduğunu gösterir.

ġekil 4.3 deki devre, pratik uygulamalara elveriĢli değildir. Çünkü C kondansatörü,

yüksek frekanslı giriĢ sinyallerinde kısa devre özelliği göstererek, üzerine çok az bir gerilim

düĢmesine sebep olur. Bu da yükselticinin kazancını arttırır. Yüksek frekanslı giriĢ

sinyallerinde çıkıĢ iĢareti en büyük düzeye ulaĢır. Dolayısıyla giriĢ sinyalinde gürültü mevcut

ise yüksek frekans kısmı olduğu gibi yükseltilir. Bu istenmeyen durumu engellemek için ġekil

32

4.4 deki gibi giriĢe seri bağlı bir R1 direnci eklenir. Böylece yüksek frekanslarda devre

kazancına Rf R1 oranı gibi bir sınır getirilir.

Rf

C

R1

Vg

─

Vç

+

ġekil 4.4. Pratikte kullanılabilen türev alma devresi

Türev alıcı devrenin giriĢine uygulanan iĢaretin türevini alabilmesi için aĢağıdaki Ģartların

yerine gelmesi gerekir:

1

1. f giriş f c

olmalıdır. Yani giriĢe uygulanan sinyalin frekansı, fc kritik

2 R1C

frekansından küçük veya eĢit olmalıdır.

2. Devrenin zaman sabitesi (T = Rf.C) ile giriĢe uygulanan sinyalin periyodu birbirine eĢit

veya yakın bir değerde olmalıdır.

Eğer, devrede bu Ģartlardan birisi veya ikisi sağlanamıyorsa, devre, giriĢine uygulanan

sinyalin türevini alamaz ve kazancı Rf R1 olan ters çeviren yükselteç gibi çalıĢır.

ĠNTEGRAL ALMA ĠġLEMĠ

Ġntegral alma iĢlemi türev alma iĢleminin tersidir. Türev alma devresinde C ve R’nin

yeri ġekil 4.5 deki gibi değiĢtirilirse integral alma iĢlemi yapan devre elde edilir.

Cf

iç

Vg

R1

─

ig

+

Vç

ġekil 4.5. Ġntegral iĢlemi yapan devre

Bu devre için de denklemler aĢağıdaki gibi yazılarak gerekli integral bağıntısı bulunur.

ig iç

iç

ig

dV

dq

ve iç C ç

dt

dt

Vg

R1

33

dir. Akımlar eĢitlendiğinde

Vg

dV

1

C ç veya Vç

Vg dt

R1

dt

R1C

elde edilir. Böylelikle çıkıĢ geriliminin giriĢ geriliminin integrali ile orantılı olduğu görülmüĢ

olur.

Op-Amp devresindeki, giriĢ ofset geriliminin, iĢlemsel yükselteci (Op-Amp) doyuma

götürmesini engellemek için ġek. 6 daki gibi geri besleme kondansatörüne paralel bir Rf

direnci bağlanır.

Rf

Cf

Vg

R1

─

Vç

+

R2

ġekil 4.6. Pratikte kullanılabilir bir integral alıcı devre

GiriĢ akımlarının eĢit olmayıĢından dolayı meydana gelebilecek ofset gerilimini ve bu

gerilimin etkilerini gidermek amacıyla yine ġek. 6 da görüldüğü gibi ters çevirmeyen giriĢle

toprak arasına bir de R2 direnci bağlanmıĢtır. Aynı zamanda bu devre pratikte kullanılan

integral alıcı devredir. R2 direncinin değeri, R2 R1 // Rf ifadesinden bulunur.

Ġntegral alıcı bir devrenin, giriĢine uygulanan bir iĢaretin integralini alabilmesi için

aĢağıdaki Ģartların sağlanması gerekir:

1

1. f giriş f c

olmalıdır. Yani giriĢe uygulanan sinyalin frekansı, fc kritik

2 Rf Cf

frekansından büyük veya eĢit olmalıdır.

2. Devrenin zaman sabitesi (T = R1.Cf) ile giriĢe uygulanan sinyalin periyodu birbirine eĢit

veya yakın bir değerde olmalıdır.

FARK YÜKSELTECĠ

Ters ve ters çevirmeyen giriĢler ġek. 7 deki gibi birlikte kullanıldığında fark yükselteç

devre elde ederiz.

R2

R1

─

V1

R3

+

V2

R4

ġekil 4.7. Fark yükselteci

34

Vç

Burada kazanç K K

Vç

dir.

V2 V1

Özel bir durum olarak R1 R3 , R2 R4 seçilirse

R

R

KK 2 4

R1 R3

olur. ÇıkıĢ,

R

Vç 2 (V2 V1 )

R1

elde edilir.

GERĠLĠM (VOLTAJ) KIYASLAYICI (COMPARATOR)

Dijital devrelerle analog sinyalleri birleĢtirdiğimizde, genellikle iki voltaj seviyesinden

hangisinin daha büyük olduğunu bilmemiz gerekir. Kıyaslayıcı devre, isminden de anlaĢıldığı

gibi, bir kıyaslama yapar ve kıyaslanan sinyalin bağıl boyutuna bağlı olarak iki farklı

seviyenin sadece birinde çıkıĢ verir.

Bir kıyaslayıcı genellikle değiĢen bir giriĢ voltajını sabit bir referans voltajına kıyaslar.

ġekil 4.8 deki gibi ters çevirmeyen uçtan yapılan giriĢ referans voltajından birazcık büyük

olduğunda, kıyaslayıcının çıkıĢı en uç pozitif (+V) sınır değerini alır. GiriĢ referanstan azıcık

küçük olduğunda ise, çıkıĢ en uç negatif (-V) sınır değerini alır.

Geri beslemesiz çalıĢan bir iĢlemsel yükselteç son derece yüksek açık halka voltaj

kazancına sahiptir ve pratikte açık halka kazancını sınırlayan faktör +V, –V besleme voltaj

değerleri olduğu için çıkıĢtan yaklaĢık +V veya –V gerilim değeri kadar sinyal alınır. GiriĢler

arasındaki en küçük bir fark bile çıkıĢın iki uç değerden birinde (+V veya –V) doyuma

gitmesine sebep olacaktır. IY bu özelliği ile basit bir kıyaslayıcı gibi davranır.

Vç

Vg

+V

VÇ

Vr

-V

Vg

Vr

ġekil 4.8. Gerilim Kıyaslayıcı ve transfer eğrisi

Vg > Vr olursa, çıkıĢtan yaklaĢık +V değeri alınır. (Vç = +V)

Vg < Vr olursa, çıkıĢtan yaklaĢık -V değeri alınır. (Vç = -V)

Devre bu haliyle ters çevirmeyen çalıĢma özelliğindedir. Çünkü Vg giriĢ voltajı ters

çevirmeyen (+) giriĢe uygulanmıĢtır. Ters çeviren giriĢe sabit referans voltajı uygulanmıĢtır.

GiriĢ ve referans (-), (+) uçlar arasında yer değiĢtirirse yukarıdaki kıyaslamanın tam tersi olur.

ARAÇLAR

Ġki çıkıĢlı doğru akım güç kaynağı.

Osiloskop, Sinyal üreteci

Dirençler; 1k, 3.3k, 5.6k, 12k, 2x10k

Kondansatörler; 100 nF, 10nF

Tümdevre; UA741

35

DENEYLER

TOPLAMA (ÇIKARMA) YÜKSELTECĠ

1. ġekil 4.9 daki devreyi kurunuz.

Rf = 12k

3.3k

+

7

5.6k

V1

+

10 V

6

2

VÇ

V2

+

3

4

5V

5V

+

-

-

10 V

-

ġekil 4.9.

2. V1 ve V2 gerilimlerini 1.5 V ve 2 V’a ayarlayınız ve yükseltici çıkıĢ gerilimini ölçerek

toplama denklemini doğrulayınız.

3. V1 ve V2 gerilimlerinden birisini ters çevirerek çıkarma iĢlemini doğrulayınız. Sonuçları

Tablo 4.1’e kaydediniz.

Tablo 4.1

GiriĢ

V1

1.5

1

V2

2

3

ÇıkıĢ

Hesapla

Ölçülen

GiriĢ

V1

—1.5

1

ÇıkıĢ

Hesapla

Ölçülen

V2

2

—3

GERĠLĠM KIYASLAYICI

1. ġekil 4.10 daki devreyi kurunuz.

10k

+

7

2

10k

Vg

+

5V

-

VÇ

3

Vr

10 V

6

4

+

+

10 V

5V

-

-

ġekil 4.10.

2. Osiloskobun birinci kanalını Vg’ye bağlayınız. Ġkinci kanalını da çıkıĢı gözlemek için

Vç’ye bağlayınız. Vr yi (referans voltajı) 0 V’a ayarlayınız. Vg yi -5 V ile +5 V aralığında

değiĢtirirken çıkıĢı da Osiloskoptan izleyiniz. ÇıkıĢta atlama olduğu andaki Vg giriĢ

voltajını Tablo 4’e kaydediniz.

3. Vr nin 1, 3, -1, -2, -3 V değerleri için ikinci maddedeki iĢlemleri tekrarlayarak Tablo

4.4’e kaydediniz.

Tablo 4.4

Vg

Vr (V)

1

2

3

-1

36

Vç

-2

-3

TÜREV ALICI DEVRE

1. ġekil 4.11 deki devreyi kurunuz.

Rf = 10k

R1

Vg

1k

C

+

7

100 nF

10 V

6

2

VÇ

3

4

+

10 V

-

ġekil 4.11.

2. Sinyal üretecinden 1 VT-T ve 1 KHz üçgen dalgayı giriĢe uygulayınız.

3. Osiloskopla giriĢ ve çıkıĢ iĢaretlerini gözleyiniz.

4. Frekansı 100 Hz ile 100 kHz arasında değiĢtirerek çıkıĢta meydana gelen değiĢmeleri

gözleyiniz. Dalga periyodu T ile Rf.C zaman sabitinin oranını bulunuz.

5. Sinyal üretecinden bu sefer giriĢe 100mVT-T, 1kHz sinüs dalgası vererek, giriĢ ve çıkıĢ

dalgaları arasındaki faz farkını bulunuz. Bulduğunuz faz iliĢkisinden giriĢ ve çıkıĢ

dalgaları arasında nasıl bir bağlantı olduğunu belirtiniz.

6. 100 Hz ve 100 kHz frekanslarındaki çıkıĢ sinyallerini gözleyerek Tablo 5’e yazınız.

7. Aynı iĢlemleri kare dalga giriĢi için de yapınız.

Tablo 4. 5

GiriĢ dalga Ģekli

1 kHz

ÇıkıĢ dalga Ģekli

100 Hz

100 kHz

Faz

Üçgen

Sinüs

Kare

T Rf C

ĠNTEGRAL ALICI DEVRE

1. ġekil 12 deki devreyi kurunuz.

2. Sinyal üretecinden 2 VT-T ve 10 KHz kare dalgayı giriĢe uygulayınız.

3. Osiloskopla giriĢ ve çıkıĢ iĢaretlerini gözleyiniz.

4. Frekansı 100 Hz ile 100 kHz arasında değiĢtirerek çıkıĢta meydana gelen değiĢmeleri

gözleyiniz. Dalga periyodu T ile R1.Cf zaman sabitinin oranını bulunuz.

37

5. Sinyal üretecinden bu sefer giriĢe 100mVT-T, 1kHz sinüs dalgası vererek, giriĢ ve çıkıĢ

dalgaları arasındaki faz farkını bulunuz. Bulduğunuz faz iliĢkisinden giriĢ ve çıkıĢ

dalgaları arasında nasıl bir bağlantı olduğunu belirtiniz.

6. 100 Hz ve 100 kHz frekanslarındaki çıkıĢ sinyallerini gözleyerek Tablo 6’ya yazınız.

7. Aynı iĢlemleri Üçgen dalga giriĢi için de yapınız.

Rf = 100k

10 nF

C

R1

Vg

+

7

10 V

6

2

10k

VÇ

3

R2

4

+

10k

10 V

-

ġekil 4. 12.

Tablo 4.6

GiriĢ dalga Ģekli

ÇıkıĢ dalga Ģekli

100 Hz

10 kHz

Üçgen

Sinüs

Kare

T R1Cf

38

100 kHz

Faz

DENEY NO

DENEYĠN ADI

:EII-5

: ĠġLEM YÜKSELTEÇLERĠNĠN FREAKANS-KAZANÇ

KAREKTERĠSTĠĞĠ VE KARE DALGA ÜRETECĠ

DENEYĠN AMACI

: ĠĢlem yükselteçlerin frekans kazanç karakteristiklerinin

bulunması ve iĢlem yükselticiler kullanılarak kare dalga üretecinin çalıĢma ilkesinin

öğrenilmesi.

ÖN BĠLGĠ

ĠĢlem yükselteçleri frekansa karĢı oldukça duyarlıdır. Yani, yükselme zamanları

oldukça uzun olduğundan çok hızlı bir gerilim yükselmesine anında cevap veremezler. Belirli

bir süre sonra cevap verirler. Eğer giriĢten uygulanan sinyalin periyodu yükselme zamanı ile

kıyaslanabilir ölçüde ise Ġ.Y nin kazancı küçülecektir.

Yükselme zamanı (Rise time) bir sinyali belirli bir düĢük değerden belirli bir yüksek

değere yükseltmek için geçen zamandır. Genellikle bir darbenin (puls) ön kenarını %10 dan

%90 a yükseltmek için geçen zaman olarak ifade edilir.

Deneyde kullandığımız 741 tüm devrelerin yükselme zamanları 0.3s civarındadır. Bu

süre oldukça uzun bir yükselme zamanıdır. ĠĢlemsel yükselteçlerin frekans kazanç

karakteristikleri deneysel yollarla saptanır ve bu karakteristikler kataloglarda verilir. Örnek bir

741 tümdevre frekans-kazanç karakteristiği dB cinsinden ġekil 5.2 de verilmiĢtir.

Kazanç

dB

Av=1000

Av=100

dB 20log

Av=50

Vç

Vg

Av=10

Frekans

MHz

ġekil 5.2. Bir tümdevre (Op-Amp) frekans-kazanç karakteristiği

Kapalı halka frekans kazanç karakteristiği açık halka karakteristiği sınırları içinde

kalır. Kazanç küçüldükçe, kazanç daha geniĢ bir frekans aralığında (bant geniĢliğinde ) sabit

kalır. Kazanç büyüdükçe sabit kazanç frekans aralığı daralır. Frekans aralığını daraltan etki

açık halka kazancıdır. ġekil 5.2 deki aralıklı çizgiler çeĢitli kapalı halka kazançlarını

göstermektedir.

Frekans-kazanç karakteristikleri, iĢlem yükselteçlerde yapılan ac devrelerinde oldukça

önemlidir. Örneğin Ġ.Y ile yapılan bir sinyal üretecinde önce bu karakteristiğe bakılır ve

çalıĢılacak frekansın üzerindeki etkisi önceden gözden geçirilir ve önlem alınır.

KARE DALGA ÜRETECĠ

ġekil 5.3’te verilen devre gerçekte bir serbest salınımlı multivibratördür. Ancak çoğu

hassas uygulama gerektirmeyen devrelerde kare dalga sinyal üreteci olarak kullanılır.

Devre, ilk bakıĢta anlaĢılacağı gibi bir fark yükselticidir. Devrenin ilk açılması ile

oluĢacak kararsızlık, giriĢlere farklı gerilim uygulanmasına sebep olur. Bu giriĢ darbesi, Ġ.Y

de büyültülerek geri besleme direnci Rg üzerinden C kondansatörünü doldurur. Bu sırada +

39

giriĢten R1, R2.ve R3 dirençleri yolu ile bir referans gerilimi verilmiĢtir. C kondansatörü

uçlarındaki gerilim, -giriĢ gerilimidir, referans gerilimi seviyesinin biraz üzerine çıkıncaya

kadar çıkıĢ pozitif bir değerdedir. Kondansatör gerilimi, referans gerilimi geçtiği anda çıkıĢ

derhal negatif değere geçer (kondansatörün çalıĢma prensibi) ve kondansatör boĢalmaya

baĢlar (Rg direnci üzerinden). Kondansatör gerilimi referans geriliminin biraz altına

düĢünceye kadar çıkıĢ negatif kalır. Kondansatör gerilimi referans geriliminin biraz altına

düĢtüğü anda, çıkıĢ tekrar pozitif değere yükselir ve kondansatör dolmaya baĢlar. Bu iĢlem

sırasıyla birbirini takip eder.

ÇıkıĢ geriliminin maksimum ve minimum değerleri besleme gerilimlerine bağlıdır.

Besleme gerilimi tam simetrik ise çıkıĢ sinyali de simetriktir, eğer besleme simetrik değilse,

çıkıĢ simetrikliği de bozulur.

Devrenin çalıĢma frekansı Rg, C ve gerilim bölücü; R1, R2 elemanlarının değeri ile

belirlenir. KarmaĢık hesaplamaya gitmeden çalıĢma frekansı,

1

f

2 R1

2 R ç C ln(1

)

R2

olduğunu vermekle yetineceğiz.

Rç=12k

C

─

Vç

+

R2=100k

R3=12k

R1=12k

ġekil 5.3. Kare dalga üreteci devresi

ĠĢlem yükselteçleri ile yapılacak devre sayısının sınırsız olduğunu söylemiĢtik. Bunun

içine çeĢitli sinyal üreteçleri, (Sinüs, kare , üçgen, asimetrik dalgalar ve darbeler), aktif pasif

süzgeçler, da yükselticiler ve anolog ve sayısal dönüĢtürücüler en çok kullanılanlardır. ÇeĢitli

kaynaklarda değiĢik uygulamaları kolaylıkla elde etmek mümkündür.

ARAÇLAR

1. Ġki çıkıĢlı güç kaynağı

2. Osiloskop, osilatör, voltmetre

3. Dirençler, 2x12k, 68 k, 100k potansiyometre, 47k potansiyometre, 4.7k, 1k

4. Tümdevre; UA741 iĢlem yükselteci

DENEYLER

A) ĠġLEM YÜKSELTEÇLERĠN FREKANS-KAZANÇ KARAKTERĠSTĠĞĠ

Not: ĠĢlem yükselteçlerinin açık halka kazançları çok yüksek olduğundan, tüm frekans aralığı

için frekans-kazanç karakteristiklerini elde etmemiz mümkün değildir. Bu karakteristiği

kapalı halka karakteristiklerinden bulacağız.

1- ġekil 5.4 deki devreyi kurarak gerekli bağlantıları yapınız.

40

R2 =

100k

R1

1k

Vg

+

7

2

3

10 V

6

VÇ

-

4

+

10 V

ġekil 5.4.

2- GiriĢ voltajını (Vg) sinyal üretecinden 200mVT-T genlikli sinüs dalga olarak uygulayınız. R1

direncini ölçüm sonuna kadar değiĢtirmeyiniz.

3- Potansiyometreden önce R2 direncini 5 k olarak ayarlayınız (Ohmmetreyle).

4- Osiloskopla çıkıĢ sinyalinin genliğini sırasıyla, giriĢ sinyalinin 100Hz. 1kHz, 10kHz,

20kHz, 50kHz, 100kHz, 200kHz. 300kHz. 400kHz, 500kHz, 1MHz frekansları için ölçerek

Tablo 5.1 e kaydediniz.

5- Aynı ölçümleri sırasıyla 10 k, 20 k, 50 k, 80 k, 100 k değerleri için de

tekrarlayarak Tablo 5.1 e kaydediniz.

6- Her bir frekans ve geribesleme direnç değerleri için tüm devrenin gerilim kazancını

hesaplayarak, elde ettiğiniz sonuçları her bir kapalı halka kazancına karĢı frekans değerleri

olarak aynı grafik üzerine çiziniz ( DüĢey eksen kazanç, yatay eksen frekans ).

7- Ayrı bir grafik kâğıdına, düĢey eksen dB yatay eksen frekans olmak üzere aynı grafiği

yeniden çiziniz.

8- Eğrilerin bükülme sınırlarında açık halka kazancını yaklaĢık olarak çiziniz.

9- Her iki eğri demetini karĢılaĢtırarak kazancın frekansla nasıl bir bağıntıya sahip

olabileceğini söyleyiniz.

Tablo 5.1

Frekans

R2 (5k)

R2 (10k)

R2 (20k)

R2 (50k)

R2 (80k)

R2 (100k)

Vç(T-T)

Vç(T-T)

Vç(T-T)

Vç(T-T)

Vç(T-T)

Vç(T-T)

100Hz

1kHz

10kHz

20kHz

50kHz.

100kHz

200kHz

300kHz

400kHz

500kHz

800kHz

1MHz

B) KARE DALGA ÜRETECĠ

1- ġekil 5.5 deki devreyi kurarak gerekli bağlantıları yapınız.

41

2- Osiloskopla her iki giriĢ ve çıkıĢ sinyalinin frekans ve genliklerini potansiyometrenin

herhangi iki konumu için ölçerek Tablo 5.2 ye kaydediniz.

3- 47k’luk potansiyometre ile frekansı değiĢtirerek çıkıĢ sinyalini gözleyiniz.

Potansiyometrenin maksimum ve minimum konumlarında, frekans ve genlikleri ölçerek

Tablo 5.3 e kaydediniz.

C=0.1

F

Rç=12k

2 7

─

3 +

4

+

V

6

ç

R2=68k

R3=12k

R=47k

R1=4.7k

10 V

+

10 V

-

ġekil 5.5.

4- Potansiyometrenin maksimum ve minimum konumlarında R1, R2 dirençlerinin değerlerini

dikkate alarak, gözlenmesi gereken frekansı hesaplayınız ve ölçümlerinizle karĢılaĢtırınız.

5- Sonuçları yorumlayınız.

Tablo 5.2.

Potansiyometre

ÇıkıĢ

Frekans

Genlik

- GiriĢ

Frekans

Genlik

+ GiriĢ

Frekans

Genlik

Konum 1

Konum 2

Tablo 5.3.

Potansiyometre

ÇıkıĢ

Frekans

Genlik

- GiriĢ

Frekans

Genlik

Minimum

Konum

Maksimum

Konum

42

+ GiriĢ

Frekans

Genlik

DENEY NO

DENEYĠN ADI

DENEYĠN AMACI

:EII-6

: MANTIK DEVRELERĠ (LOGĠC CIRCUITS)

: Mantık kapılarının incelenmesi.

ÖN BĠLGĠ

Günümüzün modern elektronik bilimi iki ayrı dalda geliĢmektedir. Bunlar ANALOG

(Benzer) ve DIGITAL (Sayısal) elektroniktir.

Analog elektronikte, bir fiziksel büyüklük baĢka fiziksel büyüklüklere (burada

elektriksel niceliklere) çevrilerek incelenir. Metallerin dirençlerinin sıcaklıkla değiĢmesinden

yararlanılarak yapılan elektriksel bir termometre analog elektroniğe bir örnektir. Sıcaklıkla

değiĢen direnç, üzerinden geçen akımın ve gerilimin değiĢmesine sebep olur. Akım ve

gerilimdeki bu değiĢme, uygun yükselticilerle yükseltilerek, yine uygun bir ölçü aletinde

doğrudan sıcaklık olarak okunabilir. Sayısal elektronikte durum farklıdır. Herhangi bir

büyüklük (matematiksel ve fiziksel) sayısal elektronikte darbelere dönüĢtürülür. Bu iĢlem

analog-sayısal dönüĢtürücülerle yapılır. Ayrıca, el hesaplayıcılarında ve bilgisayarlarda

olduğu gibi belirli karekterlerin darbe Ģekilleri devrede iĢleme sokulur.

Sayısal elektroniğin esas elemanları mantık devreleridir. Mantık devrelerinin giriĢ ve

çıkıĢları sadece iki halden ibarettir. Büyüklükleri gerilim veya akım olarak standart ölçülerde

olan bu haller ya YÜKSEK (HIGH), ya da ALÇAK (LOW) durumlardır. Bu durumlara H

veya L denilebildiği gibi 1 ve 0 da denmektedir. Biz deneylerimizde sadece 0 ve 1 olarak

ifade edeceğiz. Görüldüğü gibi 0 ve 1, ikili sayı sisteminin sayılarıdır. Bilgisayarların ikli sayı

sistemi ile çalıĢmaları da bu yüzdendir.

Sayısal hallere verilebilecek en basit örnek evlerimizdeki elektrik anahtarlarıdır.

Anahtarın bir konumunda lamba yanar, bu hale 1, diğer konumda söner, bu hale de 0

diyebiliriz. BaĢka bir konum söz konusu değildir. Mantık devrelerinin giriĢleri 0 veya bir,

çıkıĢları da 0 veya 1 olabilir. BaĢka bir durum kabul edilmez.

Mantık devreleri temel bazı KAPI veya GEÇĠġ (GATE) devrelerinden oluĢur. Bu kapı

devreleri VE (AND) VEYA (OR), VEYA DEĞĠL (NOR) VE DEĞĠL (NAND), TERS

ÇEVĠREN (INVERTER) veya bunların çeĢitli Ģekillerde birleĢtirilmeleriyle yapılan basit

düzeneklerdir.

Bunlardan en basit olanları, VE ve VEYA mantık kapılarıdır. Önce basit anahtarlarla

bu mantık kapılarını kavramaya çalıĢalım.

1) Seri bağlı iki anahtarla yapılmıĢ devreyi ele alalım.

ġekil 6.1.

Her iki anahtar kapalı olmadıkça lamba yanmaz. Bu da bize VE mantığını vermektedir.

2) Paralel bağlı iki anahtarı gözönüne alalım.

43

ġekil 6. 2.

Her iki anahtar açık olmadığı sürece lamba yanar. Bu bize VEYA mantığını vermektedir.

Elektronik devrelerde mekanik anahtarlar değil, bunların görevini yapacak diyod veya

transistörlü kapı devreleri kullanılır. Yukarıdaki iĢlemlerin aynısını diyodlarla yapalım.

A) Diyod VE devresi

ġekil 6.3.

Yukardaki devrede her iki giriĢ 0 V olduğunda her iki diyot da ileri denetlemede

olacağından çıkıĢ 0.7 V dur. Bu 0.7 V luk voltaj silikon eklem diyodunun ileri denetleme

voltajıdır. Ġki diyottan birinin griĢi 0 V olduğunda bu diyot ileri denetlemede olcacağından

yine çıkıĢ yaklaĢık olarak 0.7 V olacaktır.

Her iki giriĢ +5 V olduğunda diyotların ikisi de ters denetlemede olacağından çıkıĢ

voltajı, çıkıĢta yük direnci olmaması Ģartıyla, kaynak voltajı olacaktır.

ÇıkıĢa bir RL yük direnci bağlandığında çıkıĢ voltajı 5xRL/(R1+RL) lik bir değere

indirgenir. Bu durum aĢağıdaki Ģekilde ve ilgili voltajlara karĢılık gelen mantık durumları da

yandaki tabloda gösterilmiĢtir

ġekil 6.4.

44

B) Diyod VEYA devresi

ġekil 6.5.

Yandaki voltaj doğruluk tablosunun mantık durumları aĢağıdaki tabloda gösterilmiĢtir.

Yukardaki devrede her iki giriĢ 0 V ise, çıkıĢ 0 voltdur. Ġki diyottan birinin giriĢi +5 V

ise bu diyot ileri denetlemede olacağından akım diyot ve yük direncinden akacaktır ve çıkıĢ

voltajı giriĢ voltajından yaklaĢık olarak 0.7 V daha az olacaktır. Bunun sebebi silikon eklem

diyodun üzerine düĢen ileri denetleme voltajıdır. Bu da yaklaĢık olarak 0.7 V dur. Her iki giriĢ