Çukurova Üniversitesi

Biyomedikal Mühendisliği

BMM212 Elektronik-1 Laboratuvarı Deney Föyü

Deney#9

Alan Etkili Transistörlü Kuvvetlendiriciler

Doç. Dr. Mutlu AVCI

Arş. Gör. Mustafa İSTANBULLU

ADANA, 2015

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

DENEY 9

Alan Etkili Transistörlü (FET) Kuvvetlendiriciler

1. Amaç

Bu deneyin amacı, alan etkili transistör (field effect transistor, FET) elemanının çalışma prensibinin

anlaşılması ve akım-gerilim karakteristiklerinin çıkarılmasıdır.

2. Temel Bilgiler

Elektriksel işaret; anlamlı bilgi içeren, elektriksel olarak veri işlenmesini mümkün kılan, herhangi bir

kaynaktan doğrudan veya dönüşüm vasıtasıyla elde edilen zamana bağlı değişen dalga şekilleridir.

Eğer işaret devamlı olup devamlı zamana göre ifade edilebiliyorsa analog işaret, belirli zaman anlarına

göre ifade ediliyorsa ayrık, ayrık işaretin sayısal kodlanması olarak ifade ediliyorsa sayısal işaret olarak

adlandırılır. Analog işaretleri işleyen devrelere de analog devreler adı verilir. Kuvvetlendirici devreleri

analog devrelerdir. Bir kuvvetlendirici girişine uygulanan işareti büyüterek bir çıkış işareti oluşturan

devre topolojisidir.

Elektronik devrelerde, bağımsız bir kaynaktan alınan zamanla değişen bir işaretin kullanışlı hale

gelmesi için çoğu zaman kuvvetlendirilmesi gerekir. Örneğin Şekil 1'de bir mikrofon çıkışından alınan

işaret gösterilmiş olsun. Bu işaretin devrede hoparlörü sürebilmesi için kuvvetlendirilmeye ihtiyacı

vardır. Kuvvetlendirici buradaki işareti büyütme fonksiyonunu yapan bir elektronik devredir.

Kuvvetlendirici devresinde bulunan bir FET’in saturasyon bölgesinde çalışabilmesi için

öngerilimlenmesi gerektiğinden bu kuvvetlendirici devresinin diğer bir girişi de DC gerilim kaynağıdır.

Şekil 1 Bir kuvvetlendirici devresinin şematik gösterimi

Kuvvetlendirici devreleri bir çalışma noktası etrafında ( Q – noktası ) yeterince küçük bir işaret için

lineer (doğrusal) kabul edilebilir. Lineer kuvvetlendirici kabulü devreye süperpozisyon teoreminin

uygulanabileceğini gösterir. Bu devrelerde DC analiz ve AC analiz ayrı ayrı yapılarak çıkış cevabı bu iki

analiz cevabının toplamı olarak ifade edilebilir.

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Şekil 1'de gösterilen blok diyagramına iki farklı giriş olduğu için iki analiz yapmak gerekir. Yapılacak

olan ilk analiz devre DC bir giriş barındırdığı için DC analiz ve ikincisi ise diğer AC girişten kaynaklanan

frekanstan bağımsız küçük işaret AC analizdir. Süperpozisyon teoremine göre; birden fazla bağımsız

giriş barındıran lineer bir devrenin çıkış cevabı, devrenin bu girişlere ayrı ayrı verdiği çıkış cevaplarının

toplamıdır. Lineer bir kuvvetlendirici devresi için DC analiz, devredeki bağımsız AC gerilim kaynaklarını

kısa devre, akım kaynaklarını açık devre, kapasitörleri yine açık devre alarak yapılır. Bu analize DC

analiz denir ve kuvvetlendirici devresindeki transistörün Q çalışma noktasını belirler. Küçük işaret AC

analizi olarak adlandırılan frekanstan bağımsız yeterince küçük giriş işareti içeren AC analiz ise

devredeki DC gerilim kaynaklarının kısa devre, akım kaynaklarının açık devre ve kapasitörlerin kısa

devre alınmasıyla yapılır. Devrenin çıkış cevabı, daha öncede belirtildiği gibi, bu iki analizin çıkış

cevaplarının toplamıdır. DC çalışma noktası üzerinde bir küçük işaret AC karakteristik gösterileceği

için, DC çalışma noktasının küçük işaret AC tavra etkisi, transistörün frekanstan bağımsız küçük işaret

eşdeğerinin parametrelerinin DC çalışma noktasına göre hesaplanması ile yansıtılır.

Şekil 2 zamanla değişen bir gerilim kaynağı ve buna seri olarak bağlanmış DC gerilim kaynağı ile

birlikte bir ortak kaynaklı NMOS devresini göstermektedir. Burada zamanla değişen kaynak bir

sinüsoidal işaret üretmektedir.

Şekil 2 Ortak kaynaklı bir NMOS devresi

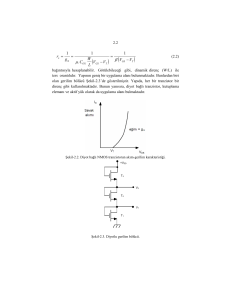

Şekil 3 ise transistör karakteristik eğrisini, DC yük hattını ve Q-noktasını gösteren bir grafiktir. Çıkış

geriliminin giriş geriliminin doğrusal bir fonksiyonu olabilmesi için devrede kullanılan FET’in

saturasyon bölgesinde öngerilimlenmesi gerekmektedir. Şekil 3 ayrıca 𝑣𝑖 sinusoidal kaynağın

uygulanmasının bir sonucu olarak gate-source gerilimindeki, drain akımındaki ve drain-source

gerilimindeki sinusoidal değişimi de göstermektedir. Toplam gate-source gerilimi 𝑉𝐺𝑆𝑄 ve 𝑣𝑖 ’nin

toplamıdır. 𝑣𝑖 değeri arttıkça 𝑉𝐺𝑆 ’nin anlık değeri artacak ve öngerilimleme noktası yük hattı

üzerinde yukarı doğru hareket edecektir. 𝑉𝐺𝑆 ’nin büyük değerleri daha büyük drain akımı ve buna

bağlı olarak da daha küçük 𝑉𝐷𝑆 gerilimine tekabül eder. 𝑣𝑖 ’nin negatif değerlerinde ise 𝑉𝐺𝑆 ’nin anlık

değeri azalacak ve yük hattı üzerindeki öngerilimleme noktası ise aşağı yönlü hareket edecektir. Daha

küçük 𝑉𝐺𝑆 değerleri daha küçük drain akımına ve buna bağlı olarak da daha büyük 𝑉𝐷𝑆 gerilimine

karşılık gelecektir.

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Şekil 3 Ortak kaynaklı NMOS transistör karakteristik eğrisi ve yük hattı

Şekil 2’deki devreye göre;

𝑣𝐺𝑆 = 𝑉𝐺𝑆𝑄 + 𝑣𝑖 = 𝑉𝐺𝑆𝑄 + 𝑣𝑔𝑠

yazılır ve burada 𝑉𝐺𝑆𝑄 DC bileşen, 𝑣𝑔𝑠 ise AC bileşendir. Anlık drain akımı;

𝑖𝐷 = 𝐾𝑛 (𝑣𝐺𝑆 − 𝑉𝑇𝐻 )2

olarak tanımlanmıştır. Yukarıdaki eşitlikler yerine konulursa;

2

𝑖𝐷 = 𝐾𝑛 [𝑉𝐺𝑆𝑄 + 𝑣𝑔𝑠 − 𝑉𝑇𝐻 ] = 𝐾𝑛 [(𝑉𝐺𝑆𝑄 − 𝑉𝑇𝐻 ) + 𝑣𝑔𝑠 ]2

ya da

2

𝑖𝐷 = 𝐾𝑛 (𝑉𝐺𝑆𝑄 − 𝑉𝑇𝐻 ) + 2𝐾𝑛 (𝑉𝐺𝑆𝑄 − 𝑉𝑇𝐻 )𝑣𝑔𝑠 + 𝐾𝑛 𝑣𝑔𝑠 2

elde edilir.

Son eşitlikteki ilk terim DC drain akımı 𝐼𝐷𝑄 , ikinci terim ise 𝑣𝑔𝑠 ile doğrusal olarak bağlı olan zamanla

değişen drain akımıdır. Üçüncü terim ise işaret kaynağının karesi ile orantılıdır. Sinusoidal bir giriş

kaynağı için eşitlikteki üçüncü terim çıkış gerilimi üzerinde istenmeyen harmonikler üretir. Bu

harmonik bileşenlerinin minimize edilmesi için;

𝑣𝑔𝑠 ≪ 2(𝑉𝐺𝑆𝑄 − 𝑉𝑇𝐻 )

olmalıdır. Bu durum eşitlikteki üçüncü terimin ikinci terimden çok küçük olmasına neden olur. Bu

durumda 𝑣𝑔𝑠 2 ’li terimin ihmal edilmesiyle;

𝑖𝐷 = 𝐼𝐷𝑄 + 𝑖𝑑

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

eşitliği elde edilir. Burada toplam akım değerinin DC ve AC bileşenleri süperpozisyon teoremi gereği

ayrı ayrı ifade edilebilir. Böylece drain akımının AC bileşeni;

𝑖𝑑 = 2𝐾𝑛 (𝑉𝐺𝑆𝑄 − 𝑉𝑇𝐻 )𝑣𝑔𝑠

olarak ifade edilir. Burada küçük işaret drain akımı küçük işaret gate-source gerilimine

transkondüktans 𝑔𝑚 ile bağlıdır. Bu ilişki;

𝑔𝑚 =

𝑖𝑑

= 2𝐾𝑛 (𝑉𝐺𝑆𝑄 − 𝑉𝑇𝐻 )

𝑣𝑔𝑠

ile tanımlanır.

Transkondüktans 𝑔𝑚 parametresi ayrıca türev alınarak da elde edilebilir.

𝑔𝑚 =

𝜕𝑖𝑑

= 2𝐾𝑛 (𝑉𝐺𝑆𝑄 − 𝑉𝑇𝐻 )

𝜕𝑣𝑔𝑠

ve

𝑔𝑚 = 2√𝐾𝑛 𝐼𝐷𝑄

olarak yazılabilir.

Küçük İşaret Eşdeğer Devre

MOSFET’in küçük işaret parametreleri tanımlandıktan sonra artık Şekil 4’te verilen basit bir FET

devresinin küçük işaret eşdeğer devresi tanımlanabilir. Şekil 5 Şekil 4’te gösterilen devrenin küçük

işaret AC modelidir.

Şekil 4 Ortak kaynaklı NMOS kuvvetlendirici devresinin AC eşdeğeri

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Şekil 5 a) Küçük işaretparametreleri ile birlikte gösterilen ortak kaynaklı NMOS transistör b) NMOS transistörün

basitleştirilmiş küçük işaret eşdeğer devresi

Şekil 5’te gösterilen küçük işaret eşdeğer devresi saturasyonda kutuplanmış olan MOSFET’in çıkış

resistansı eklenerek genişletilebilir.

İdeal durumlar göz önünde bulundurulduğunda MOSFET saturasyon bölgesinde öngerilimlendiğinde

drain akımı drain-source geriliminden bağımsızdır. Fakat MOSFET’in 𝑖𝐷 − 𝑣𝐷𝑆 karakteristiğinde

saturasyon bölgesindeki grafiğin eğimi sıfır değildir. Saturasyon bölgesindeki grafiğin eğimi

MOSFET’in çıkış resistansından kaynaklanır ve kanal uzunluk modülasyon parametresine (𝜆)bağlıdır.

Şekil 6’daki karakteristik eğrisine bakıldığında grafikteki eğriler 𝑣𝐷𝑆 = −𝑉𝐴 noktasında birleşirler. Bu

durumda drain akımı;

𝑖𝐷 = 𝐾𝑛 [(𝑣𝐺𝑆 − 𝑉𝑇𝐻 )2 (1 + 𝜆𝑣𝐷𝑆 )]

olarak tanımlanır. Burada λ kanal-uzunluk parametresidir.

Şekil 6 Kanal uzunluk modülasyon parametresinin etkisi

λ değeri 𝑉𝐴 ile ilişkilidir. Yukarıdaki eşitlikten görüleceği gibi 𝑖𝐷 = 0 için 𝑣𝐷𝑆 = −𝑉𝐴 dır ve buradan;

𝑉𝐴 =

1

𝜆

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

elde edilir. Böylece MOSFET’in çıkış resistansı;

2

𝑟0 = [𝜆𝐾𝑛 (𝑉𝐺𝑆𝑄 − 𝑉𝑇𝐻 ) ]−1

ya da

𝑟0≅ [𝜆𝐼𝐷𝑄 ]−1 =

1

𝑉𝐴

=

𝜆𝐼𝐷𝑄 𝐼𝐷𝑄

olarak tanımlanır.

Küçük işaret eşdeğer direncinin MOSFET çıkış direnci ile birlikte gösterildiği devre Şekil 7’de

verilmiştir.

Şekil 7 Ortak kaynaklı NMOS devrenin küçük işaret eşdeğer devresi

ORTAK KAYNAKLI KUVVETLENDİRİCİ

Şekil 8 bir gerilim bölücü ile öngerilimlenmiş ortak kaynaklı MOSFET kuvvetlendirici devresini

göstermektedir. Şekil 9 ise Şekil 8’deki devrenin küçük işaret eşdeğer devresini göstermektedir.

Şekil 8 Ortak kaynaklı MOSFET kuvvetlendirici

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Şekil 9 Ortak kaynaklı MOSFET kuvvetlendirici küçük işaret eşdeğer devresi

Şekil 9’daki devreye göre çıkış gerilimi,

𝑉0 = −𝑔𝑚 𝑉𝑔𝑠 (𝑟0 //𝑅𝐷 )

giriş gerilimi ise,

𝑅𝑖

𝑉𝑔𝑠 = (

) . 𝑉𝑖

𝑅𝑖 + 𝑅𝑆𝑖

olarak elde edilir. Böylece küçük işaret gerilim kazancı;

𝐴𝑣 =

𝑉0

𝑅𝑖

= −𝑔𝑚 (𝑟0 //𝑅𝐷 ). (

)

𝑉𝑖

𝑅𝑖 + 𝑅𝑆𝑖

olarak bulunur.

ORTAK SAVAKLI (DRAIN) KUVVETLENDİRİCİ

MOSFET kuvvetlendirici devrelerinden ikincisi ortak savaklı kuvvetlendirici devresidir. Şekil 10’da bu

devreye bir örnek verilmiştir. Şekilden de görüleceği gibi çıkış işareti source terminalinden alınmış,

drain terminali ise 𝑉𝐷𝐷 ’ye bağlanmıştır. AC eşdeğer devrede 𝑉𝐷𝐷 toprak haline dönüştüğünde

devreye ortak savaklı (drain) adı verilir.

Şekil 10 NMOS ortak savaklı kuvvetlendirici

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Şekil 10’da verilen devrenin DC analizi daha önce gösterilen analizlerle aynıdır. Bu nedenle burada

küçük işaret analizi üzerinde durulacaktır.

Şekil 11(a)’da devrenin küçük işaret eşdeğer devresi verilmiş, Şekil 11(b)’de ise aynı devrenin

toprakları ortaklanarak düzenlenmiş hali gösterilmiştir.

Şekil 11 a)NMOS ortak savaklı devrenin küçük işaret eşdeğer devresi b)a’daki devrenin düzenlenmiş hali

Şekil 11’e göre çıkış gerilimi;

𝑉0 = (𝑔𝑚 𝑉𝑔𝑠 )(𝑅𝑠 //𝑟0 )

olarak elde edilir. Devrenin girişinden çıkışına doğru KVL yazılırsa,

𝑉𝑖𝑛 = 𝑉𝑔𝑠 + 𝑉0 = 𝑉𝑔𝑠 + 𝑔𝑚 𝑉𝑔𝑠 (𝑅𝑠 //𝑟0 )

elde edilir. Buradan gate-source gerilimi ise;

1

𝑉𝑖𝑛

𝑔𝑚

𝑉𝑔𝑠 =

=[

]. 𝑉𝑖𝑛

1

1 + 𝑔𝑚 (𝑅𝑠 //𝑟0 )

+ (𝑅𝑠 //𝑟0 )

𝑔𝑚

ile ifade edilir. Yukarıdaki eşitliğe bakıldığında NMOS elemanın gate-source arası, değeri

1

𝑔𝑚

olan bir

direnç gibi görünür ve eşitlik basit bir gerilim bölücü formunda yazılmıştır. Early geriliminden

kaynaklanan 𝑟0 direnci ihmal edilirse; source terminaline bakıldığında etkin direç

Devrenin girişinde 𝑉𝑖 değeri;

𝑉𝑖𝑛 = (

𝑅𝑖

)𝑉

𝑅𝑖 + 𝑅𝑠𝑖 𝑖

olarak bulunur. Burada 𝑅𝑖 = 𝑅1 //𝑅2 ’dir. Eşitlikte yerlerine konulduğunda;

𝐴𝑣 =

ya da

𝑉0

𝑔𝑚 (𝑅𝑆 //𝑟0 )

𝑅𝑖

=

.(

)

𝑉𝑖 1 + 𝑔𝑚 (𝑅𝑆 //𝑟0 ) 𝑅𝑖 + 𝑅𝑆𝑖

1

𝑔𝑚

olarak görünür.

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

𝐴𝑣 =

(𝑅𝑆 //𝑟0 )

𝑅𝑖

)

1

+ (𝑅𝑆 //𝑟0 ) 𝑅𝑖 + 𝑅𝑆𝑖

𝑔𝑚

.(

olarak yazılır. Bu eşitliğe bakıldığında gerilim kazancının her zaman 1’den küçük olacağı

görülmektedir.

KAYNAKLAR:

1. Microelectronics Circuit Analysis and Design, Neamen D., 2010

2. Microelectronic Circuit Design, Jeager R., Blalock T., 2011

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Adı, Soyadı:

Öğrenci No:

3. Hazırlık Çalışması

1. BSH105 transistörünü kullanarak ortak geçitli (gate) bir kuvvetlendirici devresini çizerek DC

analizini yapınız ve küçük işaret eşdeğer modeliyle birlikte gerilim kazancını bulunuz.

Transistör parametrelerini BSH105 kataloğundan elde ediniz.

2. Aşağıdaki devrenin girişine 𝑉𝐼 = 10𝑉 uygulandında 𝑉0 = 0.2𝑉 elde edebilmek için 𝑅𝐷

direncinin değeri ne olmalıdır? (𝑉𝐷𝐷 = 10𝑉, 𝑉𝑇𝐻 = 0.7𝑉, 𝐾𝑛 = 4

𝑚𝐴

𝑉2

)

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

4. Deney Çalışması

1.

2.

3.

4.

Aşağıdaki devreyi kurunuz.

Devrenin küçük işaret gerilim kazancını bulunuz.

Devrenin 𝑉0 − 𝑡 ve 𝑉𝑖𝑛 − 𝑡 grafiklerini çiziniz.

Bulduğunuz sonucu hesaplamalarınızla karşılaştırınız.

NOT: Devredeki NMOS transistör CD4007’dir. Pspice simulasyonu için kütüphane dosyasının

ORCAD’e eklenmesi gerekmektedir.

V1

5Vdc

R2

10k

1Meg

R1

C1

V2

VOFF = 0

VAMPL = 100m

FREQ = 1000

AC =

1u

C2

1u

0

M2

R4

10k

nnMOS

0

0

0

Şekil 12

Aşağıdaki kutuya Şekil 12’deki devrenin küçük işaret modelini çiziniz ve gerilim kazancını bulunuz.

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Aşağıya deney sonucunda elde ettiğiniz dalga grafiklerini çiziniz.

Ç.Ü. Biyomedikal Mühendisliği

BMM 212 Elektronik Lab. 1 Deney#9

Adı, Soyadı:

Öğrenci No:

5. Sonuç Tartışma

1. BJT’li ve MOSFET’li kuvvetlendiriciler arasındaki farklar nelerdir?

2. CMOS nedir, anlatınız. Bir CMOS evirici devresi tasarlayarak analizini yapınız ve hangi amaçlar

için kullanıldığını yazınız.