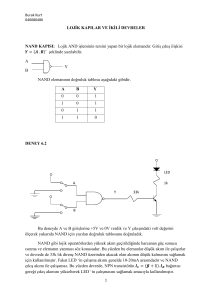

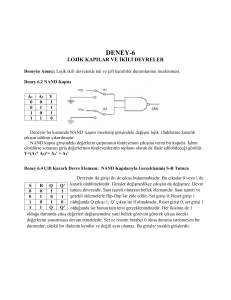

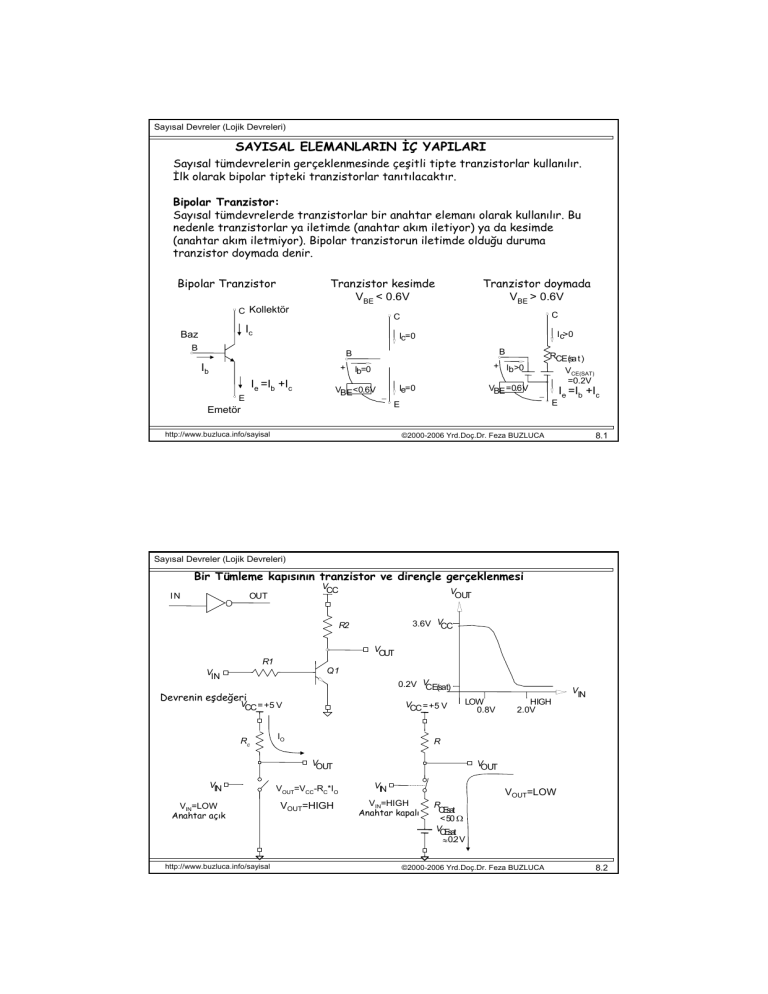

Sayısal Devreler (Lojik Devreleri)

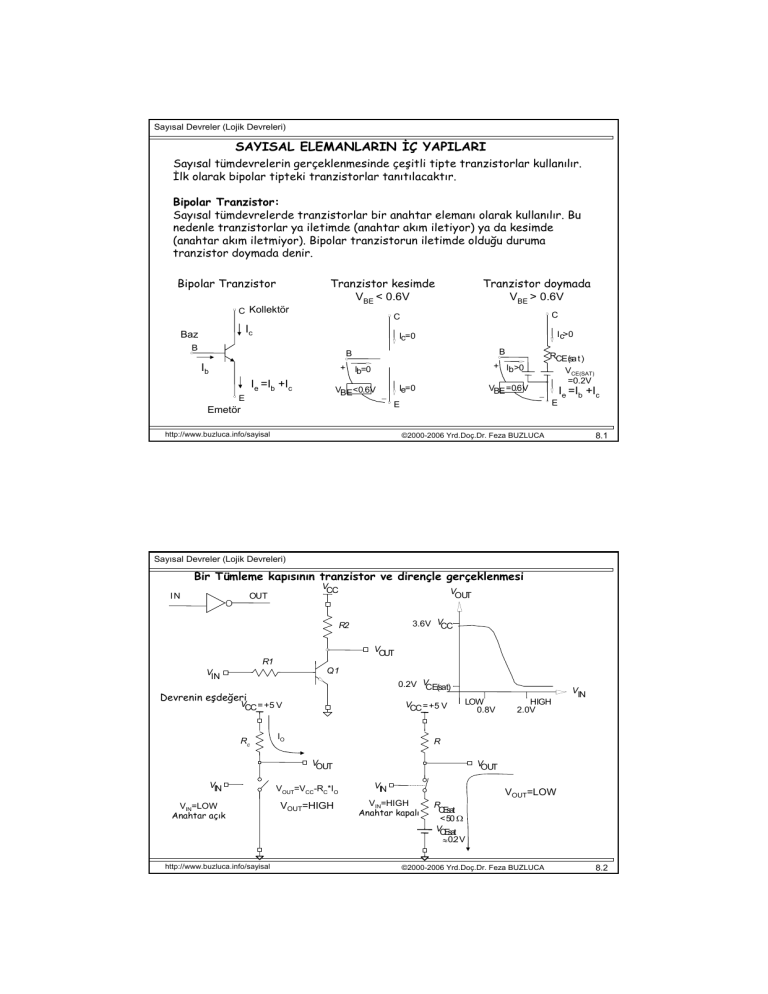

SAYISAL ELEMANLARIN İÇ YAPILARI

Sayısal tümdevrelerin gerçeklenmesinde çeşitli tipte tranzistorlar kullanılır.

İlk olarak bipolar tipteki tranzistorlar tanıtılacaktır.

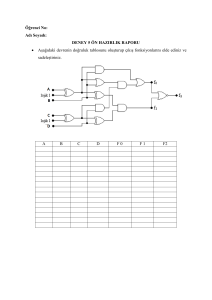

Bipolar Tranzistor:

Sayısal tümdevrelerde tranzistorlar bir anahtar elemanı olarak kullanılır. Bu

nedenle tranzistorlar ya iletimde (anahtar akım iletiyor) ya da kesimde

(anahtar akım iletmiyor). Bipolar tranzistorun iletimde olduğu duruma

tranzistor doymada denir.

Bipolar Tranzistor

Tranzistor kesimde

VBE < 0.6V

C Kollektör

C

C

Ic

Baz

Tranzistor doymada

VBE > 0.6V

Ic>0

Ic=0

B

B

B

Ib

+

Ie =Ib +Ic

VBE<0.6V

E

RCE(sa t)

VCE(SAT)

=0.2V

+ Ib>0

Ib=0

−

Emetör

VBE =0.6V

Ie=0

E

http://www.buzluca.info/sayisal

−

Ie =Ib +Ic

E

8.1

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

Sayısal Devreler (Lojik Devreleri)

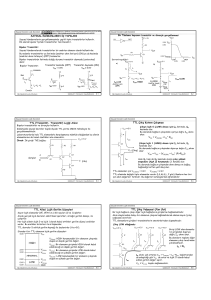

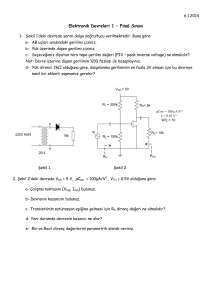

Bir Tümleme kapısının tranzistor ve dirençle gerçeklenmesi

VCC

OUT

IN

VOUT

3.6V VCC

R2

VOUT

R1

Q1

VIN

0.2V VCE(sat)

Devrenin eşdeğeri

VCC =+5 V

Rc

VCC =+5 V

IO

LOW

0.8V

VIN=LOW

Anahtar açık

http://www.buzluca.info/sayisal

VIN

R

VOUT

VIN

HIGH

2.0V

VOUT=VCC-RC*IO

VOUT=HIGH

VOUT

VIN

VOUT=LOW

VIN=HIGH

Anahtar kapalı

R

CEsat

<50 Ω

VCEsat

≈0.2V

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

8.2

Sayısal Devreler (Lojik Devreleri)

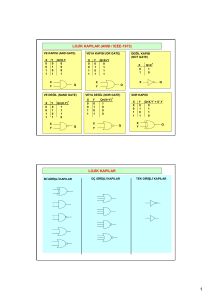

TTL (Tranzistor- Tranzistor) Lojiği Ailesi

Bipolar tranzistorlar ve dirençler kullanılır.

Örnek: İki girişli TVE bağlacı

VCC=+5 V

R1

R2

R4

Q3

A

Girişler

Q2

Q1

B

Z Çıkış

Q4

R3

http://www.buzluca.info/sayisal

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

8.3

Sayısal Devreler (Lojik Devreleri)

TTL Çıkış Katının Çalışması

VCC=+5 V

R

IOH

Q3

VO Çıkış

Q4

IOL

Çıkışın lojik 0 (LOW) olması için Q4 iletimde,

Q3 kesimde olur. Bu durumda bağlacın çıkışından

içeriye doğru IOL akımı akar.

VOL = VCE(Q4) + IOL* RQ4

Çıkışın lojik 1 (HIGH) olması için Q3 iletimde,

Q4 kesimde olur. Bu durumda bağlacın çıkışından

dışarıya doğru IOH akımı akar.

VOH = VCC – (VCE(Q3) + IOH* (R+RQ3))

Hem Q3 hem de Q4 kesimde olursa çıkış yüksek

empedans (high Z) konumunda olur. Bu

durumda bağlacın çıkışından akım akmaz ve

bağlaç bağlandığı hattan yalıtılmış olur.

VOH(MIN) = 2.5V

TTL elemanlar için VOL(MAX) = 0.4V

TTL ailesinde değişik tipte elemanlar vardır (LS,ALS,L, F gibi). Bunların

her biri için akım değerleri farklıdır. Bu değerler kataloglardan

öğrenilebilir.

http://www.buzluca.info/sayisal

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

8.4

Sayısal Devreler (Lojik Devreleri)

TTL Çıkış Yelpazesi (Fan Out)

Bir lojik bağlacın çıkışı diğer lojik bağlaçların girişlerine bağlanmaktadır.

Akım olaylarından dolayı bir elemanın çıkışına bağlanabilecek eleman

sayısı sınırlıdır.

TTL elemanların girişleri tranzistorların emetörlerinden oluşmaktadır.

Çıkış LOW olduğunda:

VCC=+5 V

VCC=+5 V

VCC=+5 V

VCC=+5 V

R1

R1

R1

R

IIL

IIL

IIL

Q3

VOL

Q4

Girişi LOW olan

elemanların

girişinden dışarıya

doğru IIL akımı akar.

Bu akımların toplamı

diğer elemanın çıkışı

tarafından

yutulmaktadır.

IOL < ΣIIL

IOL akımı çok artarsa VOL = VCE(Q4) + IOL* RQ4

bağıntısından da anlaşıldığı gibi VOL de artar ve

lojik ‘0’ olarak kabul edilen gerilim değeri aşılır.

IOL

http://www.buzluca.info/sayisal

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

8.5

Sayısal Devreler (Lojik Devreleri)

Çıkış HIGH olduğunda:

VCC=+5 V

VCC=+5 V

VCC=+5 V

VCC=+5 V

R

R1

R1

R1

IOH

IIH

Q3

VOH

Q4

IIH

IIH

Girişi HIGH olan

elemanların

girişinden içeriye

doğru IIH akımı akar.

Bu akımların toplamı

diğer elemanın

çıkışından

çekilecektir.

IOH < ΣIIH

IOH akımı çok artarsa VOH = VCC – (VCE(Q3) + IOH* (R+RQ3))

bağıntısından da anlaşıldığı gibi VOH azalır ve lojik ‘1’ olarak

kabul edilen gerilim değerinin altına düşer.

Bir elemanın çıkış yelpazesi, LOW ve HIGH konumları için

hesaplanan değerlerden küçük olana eşittir.

TTL elemanlara ait VOH, VOL, VIH, VIL, IOH, IOL, IIH, IIL gibi değerler bu

elemanların kataloglarında yer almaktadır.

http://www.buzluca.info/sayisal

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

8.6

Sayısal Devreler (Lojik Devreleri)

CMOS (Complementary MOS) Lojiği Ailesi

MOS FET (Metal-Oxide Semiconductor Field-Effect Tranzistor)

kullanılır. Lojik bağlaçlarda kullanılan MOS tranzistorlar birer ayarlı

direnç gibi düşünülebilir.

Drain

Gate-Source (VGS)arasına uygulanan gerilime göre

Drain Source (RDS)arasındaki direnç değişir.

Tranzistor tıkamadayken RDS ≥ 1MΩ

Tranzistor iletimdeyken RDS ≤ 100Ω

Gate

Source

İki tip MOS tranzistor vardır.

b) p kanallı MOS: PMOS.

a) n kanallı MOS: NMOS.

−

dra in

gate

+

V

gs

source

gate

+

dra in

sou rce

V

gs

-

VGS arttıkça RDS direnci azalır.

Normalde: VGS ≥ 0V

http://www.buzluca.info/sayisal

VGS azaldıkça RDS direnci azalır.

Normalde: VGS ≤ 0V

8.7

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

Sayısal Devreler (Lojik Devreleri)

CMOS Tümleme Bağlacı

VDD = +5.0 V

IN

OUT

Q2

(p-channel )

VOUT

Q1

V IN

(n-channel )

http://www.buzluca.info/sayisal

V IN

Q1

Q2

VOUT

0.0 (L)

5.0 (H)

off

on

on

off

5.0 (H)

0.0 (L)

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

8.8

Sayısal Devreler (Lojik Devreleri)

CMOS Tümleme Bağlacının Anahtar Modeli

VD D = +5.0 V

Q2

VIN Low ise

iletimde

(p-cha nne l)

VOUT

0 = 1 Durumu:

VD D = +5.0 V

Q1

VIN

V IN = L

VIN High ise

iletimde

(n-cha nne l)

VOUT = H

1 = 0 Durumu:

VDD = +5.0 V

V IN = H

http://www.buzluca.info/sayisal

VOUT = L

8.9

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

Sayısal Devreler (Lojik Devreleri)

CMOS TVE (NAND) Bağlacı

A

B

VDD

Q2

Z

Q4

A B

Q1 Q2 Q3 Q4

Z

on

off

on

off

H

H

H

L

Z

A

Q1

B

Q3

http://www.buzluca.info/sayisal

L

L

H

H

L

H

L

H

off

off

on

on

on

on

off

off

off

on

off

on

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

8.10

Sayısal Devreler (Lojik Devreleri)

CMOS TVE (NAND) Bağlacı Anahtar Modeli

VDD

VDD

VDD

Z =H

Z =H

Z =L

A =L

A=H

A=H

B =L

B =L

B =H

0 TVE 0 = 1

0 TVE 1 = 1

http://www.buzluca.info/sayisal

1 TVE 1 = 0

8.11

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

Sayısal Devreler (Lojik Devreleri)

CMOS TVEYA (NOR) Bağlacı

VDD

A

Q2

B

Q4

A

B

A B

Z

Q1

http://www.buzluca.info/sayisal

Z

Q3

L

L

H

H

L

H

L

H

Q1 Q2 Q3 Q4

Z

on

off

on

off

H

L

L

L

off

off

on

on

on

on

off

off

off

on

off

on

©2000-2006 Yrd.Doç.Dr. Feza BUZLUCA

8.12