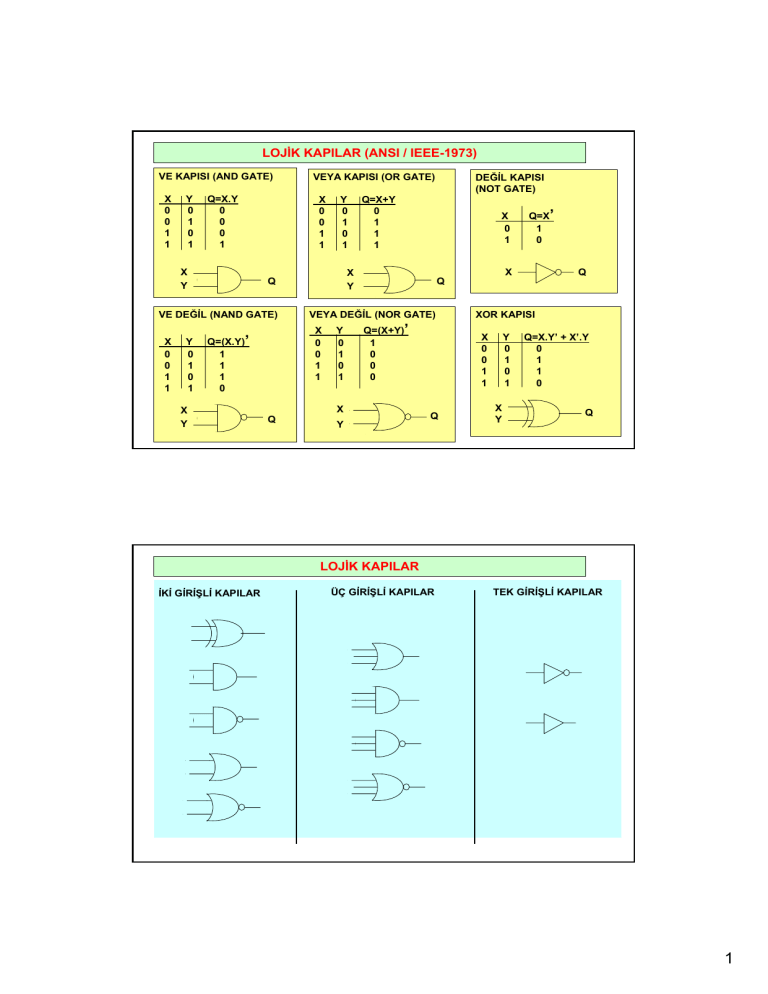

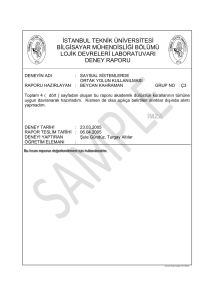

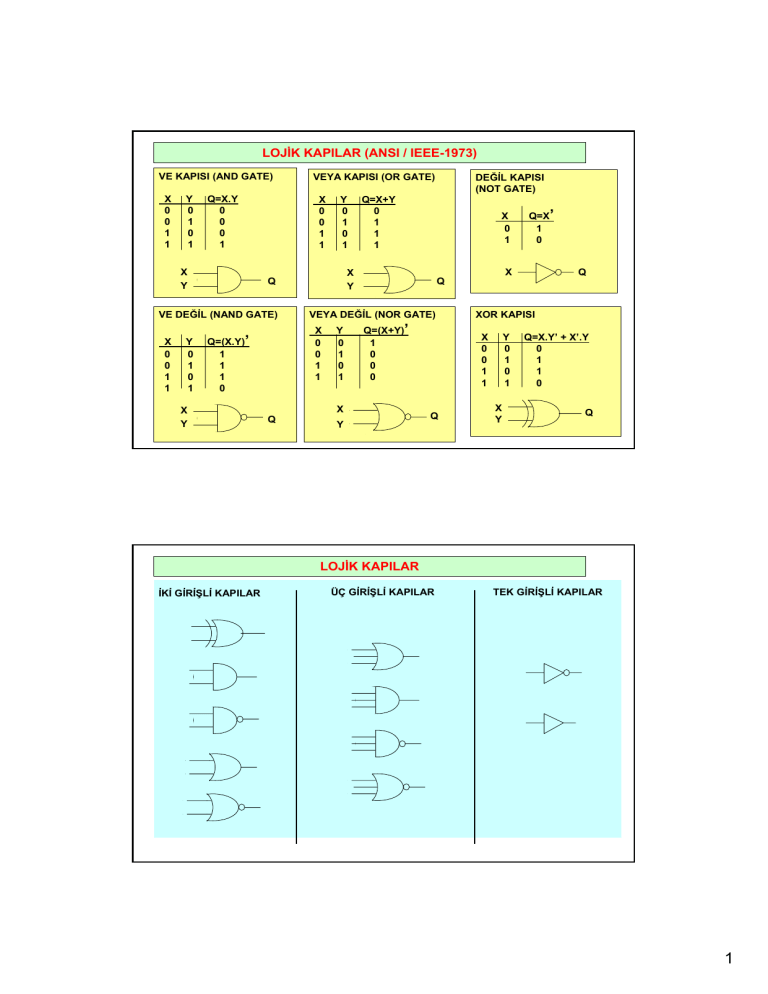

LOJİK KAPILAR (ANSI / IEEE-1973)

VE KAPISI (AND GATE)

X

0

0

1

1

Y

0

1

0

1

Q=X.Y

0

0

0

1

X

Y

X

0

0

1

1

Y

0

1

0

1

Y

0

1

0

1

X

Y

Q

X

0

1

Y

0

1

0

1

Q=(X+Y)’

1

0

0

0

X

Y

Q

XOR KAPISI

X

0

0

1

1

Q

Q=X’

1

0

X

Q

VEYA DEĞİL (NOR GATE)

X

0

0

1

1

Q=(X.Y)’

1

1

1

0

DEĞİL KAPISI

(NOT GATE)

Q=X+Y

0

1

1

1

X

Y

Q

VE DEĞİL (NAND GATE)

X

0

0

1

1

VEYA KAPISI (OR GATE)

Y

0

1

0

1

X

Y

Q=X.Y’ + X’.Y

0

1

1

0

Q

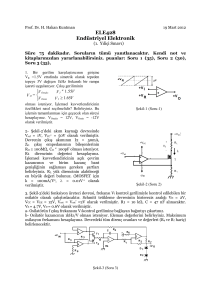

LOJİK KAPILAR

İKİ GİRİŞLİ KAPILAR

ÜÇ GİRİŞLİ KAPILAR

TEK GİRİŞLİ KAPILAR

1

ANSI/IEEE-1973

ANSI/IEEE-1984

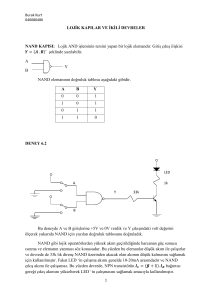

ÖRNEK BİR SAYISAL DEVRE VE DOĞRULUK TABLOSU

X

Y

F

Q

Z

x

Y

Z

p

X

0

0

0

0

1

1

1

1

Y

0

0

1

1

0

0

1

1

Z

0

1

0

1

0

1

0

1

F

0

0

0

0

0

0

1

1

p

0

1

0

0

0

0

0

0

Q

0

1

0

0

0

0

1

1

F=X.Y

P=X’.Y’.Z

Q=F+P

=X.Y+X’Y’Z

Q

2

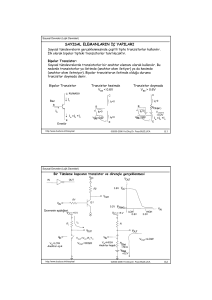

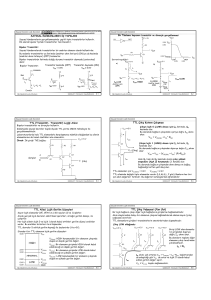

SAYISAL LOJİK AİLELER

SAYISAL ELEMANLAR SADECE LOJİK İŞLEMLERİ İLE DEĞİL AYNI ZAMANDA AİT

OLDUKLARI TEKNOLOJİYE GÖREDE SINIFLANDIRILIRLAR

•İLK LOJİK İŞLEM AİLESİ:

•RTL: DİRENÇ TRANZİSTOR LOJİK

•DTL: DİYOT TRANZİSTOR LOJİK

•STANDART OLARAK KABUL EDİLEN LOJİK AİLE:

•TTL: TRANZİSTOR TRANZİSTOR LOJİK

•YÜKSEK HIZLI İŞLEM AİLESİ

•ECL: EMİTTER BAĞLAMALI LOJİK

•YÜKSEK ELEMAN YOĞUNLUĞU OLAN TÜMDEVRELER:

•MOS: METAL OKSİT YARIİLETKEN

•DÜŞÜK GÜÇ TÜKETİMİ OLAN TÜMDEVRELER:

•CMOS: COMPLEMENTARY (TÜMLEYİCİ) MOS

Vcc

Vcc

D1

A

RC

R

D2

D1

A

Y

D2

B

Y

RB

Y

A

R

B

DİYOD AND KAPISI

Vcc= VR+ VD + VA

Vcc=5v iken

VD1= VD2=5V Î VY=?

VD1= VD2=4V Î VY=?

VD1= 0V, VD2=5V Î VY=?

DİYOD VEYA KAPISI

TRANZİSTOR NOT KAPISI

Vcc= Vce + Ic.Rc

Vce= Vcc - IcRc

= Vcc – β.Ib.Rc

= Vcc – β.(Va-Vbe).Rc/Rb

= Vcc – β.(Va-0.6).Rc/Rb

Vce≤ Vce(sat) iken

Ic= ( Vcc-Vce(sat) )/ (Rc+Rce(sat))

Rce(sat) ≤ 50Ώ

Ic= ( Vcc-Vce(sat) )/ Rc olarak

hesaplanır

3

A

C

B

E

D

Z

F

Vcc

Vcc

D3

R1

C

A

R3

E

D4

D1

D5

D

R2

D2

Z

D6

B

F

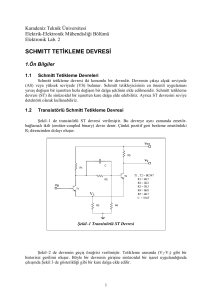

Soru: Diyotlar ile oluşturulmuş AND ve OR kapılarının ardarda bağlantısının

Vcc= 5V, Giriş işaretleri 0V ve 5 V (lojik 0 ve 1) olarak alındığında

Girişlerin (VA, VB, VD, VF) lojik değerlerine bağlı olarak, çıkış (Vc, VE, Vz)

gerilimlerinin ifadelerini belirleyiniz. Bu bağlantı hakkında neler söylenebilir. (Direnç

değerlerinin çıkış gerilimleri üzerindeki etkisi tartışılacaktır)

Örnek: VA=VB=5V Î D1, D2 TIKAMADADIR. DOLAYISI İLE

VD=0 V Î VE= VCC - VR1 - VD3 = VE= VCC - VR1 - 0.6

VD=5 V Î VE= VCC-VD = 4.4V

DTL LOJİK

Vcc

• D1 VE D2 DİYODLARI

AND KAPISINI

OLUŞTURUR.

Vcc

RC

R1

D3

D1

A

D4

Y

X

D2

B

R2

Q

• D3 VE D4 DİYODLARI

TRANZİSTORU İLETİME

GEÇİREN Vx GİRİŞ

GERİLİMİNİ

YÜKSELTMEKTİR.

DTL NAND GATE

A

0

0

1

1

B Vx

Vy Tran. Q

0 <1.8 <0.6 OFF 1

1 <1.8 <0.6 OFF 1

0 <1.8 <0.6 OFF 1

1

1.8 0.6 ON

0

4

DTR LOJİK VE SOURCING CURRENT, SINKING CURRENT

Vcc

Vcc

D1

R1

RC

D3

Vcc

Vcc

ILEAK

D4

D1

R1

RC

D3

D4

OFF

ON

D2

D2

R2

R2

Vcc

GND

Vcc

Vcc

D1

R1

Vcc

Vcc

RC

D3

D4

D1

R1

RC

D3

D4

ON

OFF

D2

D2

R2

R2

Vcc

Vcc

RTL LOJİK

Vcc

RC

Q

Rb

C

Rb

Rb

B

A

RTL NOR GATE

Çalışmasını açıklayınız

5

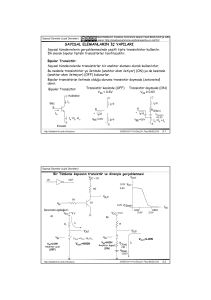

TRANZISTOR – TRANZISTOR LOGIC (TTL)

Vcc

R1

4KΏ

R2

1.6KΏ

X=1 VE Y=1 ÎQ2 VE Q3

TRANZİSTORLARI İLETİMDE

Q1 VE Q4 TRANZİSTORLARI

KESİMDEDİR.

R3

130Ώ

Va

VQ2C=VBEon + VCESAT

Vc

Q4

X

Q4’ÜN İLETİMDE OLMASI İÇİN

EN AZ

Q1

D1

Vb

VCESAT+VBEon+VD1

Q2

Y

Q3

Z

Vd

R4

1KΏ

OLMALIDIR. D1, Q3 İLETİMDE

İKEN Q4’ÜN TIKAMADA

KALMASI İÇİN KULLANILMIŞTIR.

AKIM Q3 ÜZERİNDEN İÇERİYE

DOĞRU (SINK)

İKİ GİRİŞLİ TTL NAND KAPISI

X=0 VEYA Y=0 ÎQ1 İLETİMDE, Q2 VE Q3 KESİMDE, Q4 İLETİMDEDİR.

AKIM Q4 ÜZERİNDE DIŞARIYA DOGRU (SOURCE)

İKİ GİRİŞLİ TTL NOR KAPISI

Vcc

R1

R2

R3

Q5

X

Q3

Q1

D1

Z

R4

Y

Q6

R5

Q2

Q4

GND

Çalışmasını açıklayınız

6

EMITER COUPLED LOGIC (EMITTER BAĞLAMALI LOJİK)

Vcc

R1

300Ώ

R2

330Ώ

V1

X

Q1

V0

Q1’

Q3

R5

Q2

VBB

Y

VE

R4

R6

R3

1.3K

GND

X

0

0

1

1

Y

0

1

0

1

Q1

OFF

OFF

ON

ON

Q1’

OFF

ON

OFF

ON

Q3

ON

OFF

OFF

OFF

ÖZEL KARAKTERİSTİKLER

GÜRÜLTÜ PAYI (NOISE MARGIN)

VCC

VOH : “LOJİK 1” OLARAK ÜRETİLECEK

MİNİMUM ÇIKIŞ GERİLİMİ

VCC

VOL : “LOJİK 0” OLARAK ÜRETİLECEK

VOH

MAKSİMUM ÇIKIŞ GERİLİMİ

YÜKSEK DURUM

GÜRÜLTÜ PAYI

VIH : “LOJİK 1” OLARAK KABUL

VIH

LOJİK

OLMAYAN

DURUM

EDİLEBİLEN MİNİMUM GİRİŞ GERİLİMİ

LOJİK

OLMAYAN

DURUM

VIL : “LOJİK 0” OLARAK KABUL

EDİLEN MAKSİMUM giriş GERİLİMİ

VIL

VOL

0

çıkış

DÜŞÜK DURUM

GÜRÜLTÜ PAYI

0

giriş

TTL İÇİN DEĞERLER

VOH : 2.4 V

VOL : 0.4 V

VIH : 2 V

VIL : 0.8 V

YDGP: 2.4 – 2 = 0.4

DDGP: 0.8 – 0.4 = 0.4

7

ÇIKIŞ YELPAZESİ (FAN OUT)

Bir kapının çıkış yelpazesi, o kapının çıkışına bağlanabilecek ve kapının normal çalışmasını

etkilemeyecek standart yüklerin sayısı

IOL

IOH

IIH

TTL İÇİN

IOH : 400 µA

IIH : 40 µA

IOL : 16 mA

IIL : 1.6 mA

IIH

( IOH / IIH )

( IOL / IIL )

IIH

IIL

IIL

IIL

Oranlarından

Küçük olanı

seçilir.

GEÇİŞ ZAMANI (TRANSITION TIME)

GEÇİKMEYE NEDEN OLAN TÜMDEVRE İÇİNDE BULUNAN

ELEMANLARIN SAHİP OLDUKLARI ÇALIŞMA

ŞARTLARINDAKİ KAPASİTİF ETKİLERDİR.

YÜKSELME SÜRESİ

(RISE TIME)

DÜŞME SÜRESİ

(FALL TIME)

GEÇİKME ZAMANI (PROPAGATION DELAY)

İKİLİ SİSTEM İŞARETİNİN DEĞERİNDE BİR DEĞİŞİM

OLDUĞUNDA İŞARETİN GİRİŞTEN ÇIKIŞA (İŞARET

YOLU ÜZERİNDE) OLUŞAN GEÇİKMEDİR.

Giriş ve çıkış işaretinin %50 noktaları arasındaki zaman

farkı olarak tanımlanır. (Nanosn mertebesindedir.)

Bir TTL kapısı için

tpHL=7 nsn

tpLH=11 nsn

tpHL: 1 Î 0

GEÇİŞ SÜRESİ

tpLH: 0 Î 1

GEÇİŞ SÜRESİ

8

SORU: Aşağıdaki devrede bulunan elemanlar için propagation delay =0.01 mikrosn. dir. X girişi

olarak verilen işarete karşın Y çıkış işaretini çiziniz.

x

y

A

B

C

1 mikrosn

x

A

B

C

y

GÜÇ KAYBI (POWER DISSIPATION)

HER ELEKTRONİK DEVRE ÇALIŞMASI ESNASINDA BİR GÜÇ HARCAR. BU GÜÇ KAYBI Mw (mili

WATT) OLARAK İFADE EDİLİR VE KAPININ İHTİYACI OLAN GÜÇ MİKTARINI BELİRLER.

BİR KAPIDA KAYBOLAN GÜÇ MİKTARI ÇEKİLEN Icc AKIMI VE BESLEME GERİLİMİ Vcc İLE

BELİRLENİR.

GÜÇ=Vcc x Icc

IccH=Kapının çıkışı yüksek gerilim seviyesinde iken güç kaynağından çekilen akım (TTL NAND

kapısında Vcc=5V iken IccH=1 mA)

IccL=Kapının çıkışı düşük gerilim seviyesinde iken güç kaynağında çekilen akım(TTL NAND kapısında

Vcc=5V iken IccL=3 mA)

Ortalama Güç kaybı

Icc (ort)= (IccH + IccL) / 2

Pd (ort)= Icc (ort) x Vcc

9

AÇIK KOLLEKTOR (OPEN COLLECTOR) ÇIKIŞ

ÇIKIŞ TRANSİSTÖRÜ ÜZERİNE DIŞARIDAN BİR YÜK BAĞLAMAK İÇİN KULLANILAN ÇIKI ŞEKLİ. BU

ÇIKIŞLARDAN, ÇIKIŞ İŞARETİNİ KULLANABİLMEK İÇİN YÜK BAĞLAMAK GEREKLİDİR.

YÜK OLARAK

LED

ROLE

SELENOİD VALF

……..

Vcc

YÜK

BAĞLANABİLİR

ÜÇ DURUMLU ELEMANLAR (THREE STATE)

AYNI HATTI ORTAK OLARAK PAYLAŞAN ELEMANLARIN ÇIKIŞLARI 3 DURUMLUDUR.

CS

SAYISAL

SİSTEM

1

A0

A1

CS

CS

SAYISAL

SİSTEM

2

B0

B1

CS

X0

CS

SAYISAL

SİSTEM

3

X1

CS

10

ÜÇ DURUMLU TTL NAND KAPISI

R1

R2

R3

Va

Vc

X

Q4

Q1

D1

Vb

Q2

Y

Q3

R4

Z

CS

SORULARINIZ

11