3. 1

3. MOS øùLEMSEL KUVVETLENDøRøCøLER

øúlemsel kuvvetlendiriciler, genelde, gerilim kontrollu gerilim kayna÷ı

iúlevini yerine getirirler. ødeal iúlemsel kuvvetlendiricide gerilim kazancı sonsuz,

giriú direnci sonsuz, çıkıú direnci sıfır, band geniúli÷i sonsuzdur; sıcaklı÷a

ba÷ımlılık ve distorsiyon sorunları yoktur. Pratikte, bu özelliklere yaklaúılmaya

çalıúılır. MOS teknolojisiyle gerçekleútirilen iúlemsel kuvvetlendirici yapılarında

temel özellikler:

1.Kazanç Kd = 100... 105 (40dB-100dB)

2.Sınırlı lineerlik bölgesi: VO = Kd . (VP -VN ) lineer ba÷ıntısı VO çıkıú geriliminin

sınır de÷erleri arasında, baúka bir deyiúle VDD nin bıraz altı ile -VSS nin biraz üstü

arasinda geçerli.

3.dengesizlik gerilimi MOS yapılarda 5 - 15 mV mertebesinde,

4. kazanç-band geniúli÷i çarpımı 1 - 10 MHz ,

5. yükselme e÷imi 1 - 20 V/Psn,

6. çıkıú direnci açık çevrimde 0.1:-5k: de÷erleri arasında,

7. gürültü gerilimi 10 - 50 PV (bipolarda 3-5PV).

8. besleme kayna÷ındaki de÷iúimleri bastırma 60-80dB

9. Dinamik aralı÷ı 90dB

baúlıkları altında özetlenebilir.

MOS iúlemsel kuvvetlendiricilerin performansı klasik bipolar yapılara

göre farklılık gösterir. En önemli temel fark, MOS yapılarda kuvvetlendiricilerin

yükünün tam olarak belirlenmiú ve kapasitif olmasıdır. Bu kapasitif yük, genelde,

birkaç pF mertebesindedir.

3.1. CMOS iúlemsel kuvvetlendirici

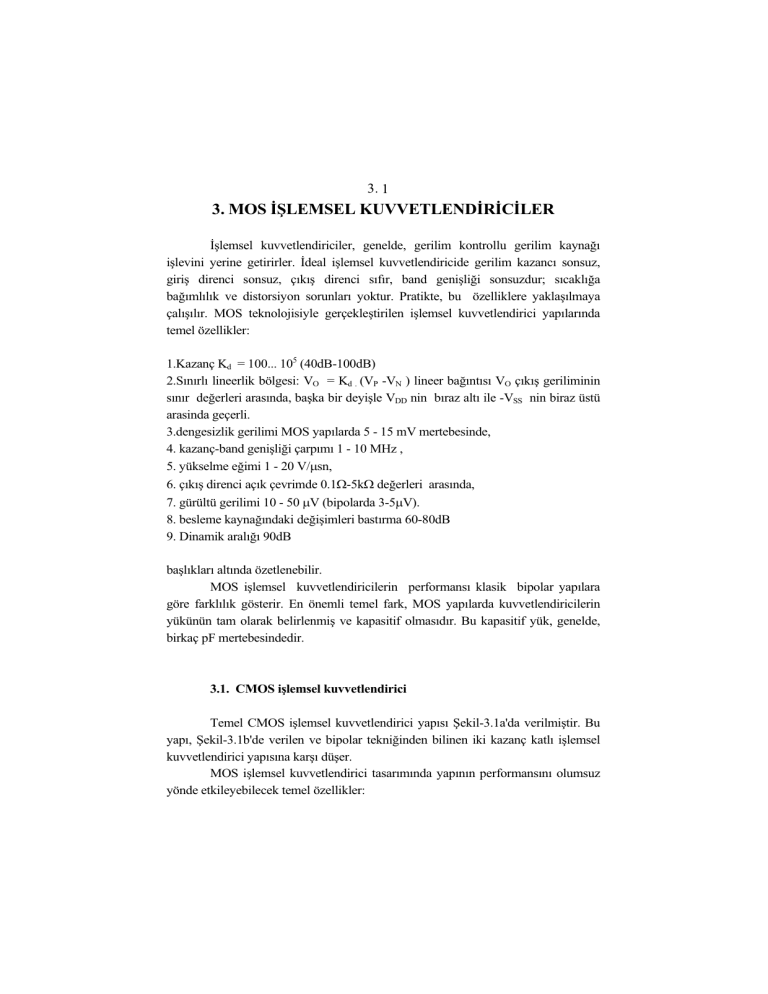

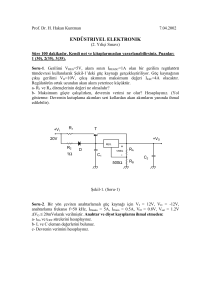

Temel CMOS iúlemsel kuvvetlendirici yapısı ùekil-3.1a'da verilmiútir. Bu

yapı, ùekil-3.1b'de verilen ve bipolar tekni÷inden bilinen iki kazanç katlı iúlemsel

kuvvetlendirici yapısına karúı düúer.

MOS iúlemsel kuvvetlendirici tasarımında yapının performansını olumsuz

yönde etkileyebilecek temel özellikler:

3. 2

1. Kazancın sonlu olması,

2. Lineerlik bölgesinin sonlu olması,

3. dengesizlik gerilimi,

4. frekans e÷risi,

5. gürültü

alt baúlıkları altında sıralanabilir.

+VCC

+VDD

IO1

IO1

IO2

IO2

+

+

Vi

Vi

CC

T1

-

CC

VO

T2

T1

-

T6

T6

T3

VO

T2

T3

T4

T4

-VSS

-VEE

(a)

(b)

T5

T8

T7

+V DD

I7

IO

VO

T1

I6

T2

IB

T6

T3

T

-V SS

(c)

ùekil-3.1. a) øki kazanç katlı CMOS iúlemsel kuvvetlendirici, b) yapının bipolar tekni÷indeki

karúılı÷ı, c) gerçekleútirme devresi

Devrenin açık çevrim kazancı, kazanç katları için verilen yöntemle kolayca

hesaplanabilir. MOS tranzistorun giriú direncinin çok yüksek olması nedeniyle ilk

kat ikinci kat tarafından yüklenmez. Gerilim kazancı iki katın kazançları ayrı ayrı

hesaplanarak bulunabilir. ølk katın gerilim kazancı hesaplanırsa

3. 3

KV 1 =

g m1

go2 + go4

(3.1)

bulunur. Burada gm1 giriú tranzistorlarının e÷imi, gO2 ve gO4 de tranzistorların çıkıú

iletkenlikleridir. Benzer úekilde hareket edilirse, ikinci katın kazancı da

KV 2 = -

g m6

go6 + go7

(3.2)

olarak elde edilir. Toplam kazanç bu iki kazancın çarpımı olur. Bu tür yapılarda

birkaç bin mertebesinde gerilim kazancı sa÷lanması istenir. her bir kat 50 civarında

kazanç sa÷lar. Bu tür yapılar genellilkle anahtarlanmıú kapasiteli süzgeçlerde

kullanılırlar ve bu civardaki kazanç söz konusu uygulama alanı için yeterli olur.

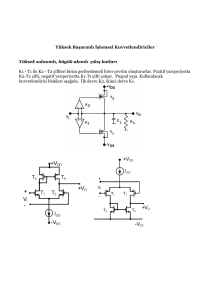

3.1.1. CMOS iúlemsel kuvvetlendiricilerde dengesizlik

CMOS iúlemsel kuvvetlendiricilerde çıkıúı sıfıra getirecek dengesizlik

geriliminin iki bileúeni bulunur. Bunlardan birincisi, uygun olmayan boyut ve

kutuplama nedeniyle ortaya çıkan sistematik dengesizlik, ikincisi ise imalat

toleranslarından kaynaklanan rastgele dengesizliktir.

Sistematik dengesizlik

T5

T8

T1

IO/2

T7

IO

I7

T2

I6

VO

T4

Vi2

IO/2

IB

T6

T3

-VSS

IG

I6

T2

T1

+VDD

I7

IO

IO/2

VO1

T7

8

IO/2

IB

T3

T5

+VDD T

+

VGS3

-

T4

+

VGS6

-

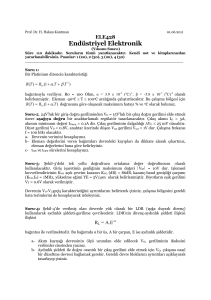

ùekil-3.2. CMOS iúlemsel kuvvetlendiricide sistematik dengesizlik

T6

-VSS

3. 4

MOS iúlemsel kuvvetlendiricilerde kat baúına sa÷lanan gerilim kazancı

düúüktür, dolayısıyla ikinci kat da dengesizlik üzerine etkilidir. ølk katın giriúleri

ùekil-3.2'de gösterilen biçimde referans noktasına ba÷lansın, yani topraklansın. T1 T5 tranzistorları ile kurulmuú olan giriú fark kuvvetlendiricisi asimetrik çıkıúlı,

yapının T6-T7 tranzistorlarıyla kurulmuú bulunan çıkıú katı da yine asimetrik

çıkıúlıdır ve T7 tranzistoru aktif yük görevini üstlenmektedir. ødeal durumda her iki

giriú ucunun da toprak potansiyelinde bulunması nedeniyle, VO çıkıú gerilimin ve

buna ba÷lı olarak IG akımının sıfır, dolayısıyla da T6 ve T7 tranzistorlarının savak

akımlarının I6 = I7 olması gerekir.

Yapıda, aynı geçit-kaynak gerilimi altında aynı savak akımı aktı÷ından, T4

tranzistorunun sava÷ındaki gerilim T3 tranzistorunun savak gerilimine eúit olur.

Dolaysıyla her iki tranzistorun VDS gerilimleri aynıdır. Bu gerilim ise T6

tranzistorunun VGS geçit-kaynak gerilimine eúittir. Oysa, T6 tranzistorunun çıkıú

gerilimini sıfır yapmak üzere gereksinme gösterdi÷i geçit gerilimi bundan farklı

olabilir. Bu nedenle,T3, T4 ve T6 nın akım yo÷unlukları, bu üç elemanda aynı

olacak biçimde W/L oranlarının seçilmesi zorunlu olur.

Devrede denge durumunda

(W / L )1 = (W / L )2 ve (W / L )3 = (W / L )4

V DS 3 = V DS 4

oldu÷undan tüm akım ve gerilimler simetriktir.

V GS 3 = V GS 6

ise

I 6 = I 7 , I G = 0 ve V DS 6 = 0 ( V SS ) = V SS

olur. Bu úart yerine gelmiyorsa

IG z 0

olur ve bir dengesizlik oluúur. Bu dengesizlik sistematik dengesizlik olarak

isimlendirilir.VGS6 'nın çıkıúı sıfıra getiren de÷erini VGS6M ile gösterelim. Böylece

giriú dengesizlik gerilimi

3. 5

V OS =

V GS 6 - V GS 6 M

V GS 3 - V GS 6 M

=

Kd

Kd

biçiminde ifade edilebilir. Bu ba÷ıntıda Kd giriú katının fark iúaret kazancını

göstermektedir. Elemanların doymada oldukları varsayılır ve kanal boyu

modülasyonu da ihmal edilirse

§ ·

2.¨ I O ¸

©2¹

V GS 3 = V DS 3 = V GS 4 = V DS 4 = V TN k n '.(W/L )3

yazılabilir. Benzer úekilde T6 için

V GS 6 = V TN +

2. I 6

k n '.(W/L )6

elde edilir. I6 = I7 ve VGS6 = VGS3 olması gerekti÷inden

V GS 3 = V TN +

2. I 7

k n '.(W/L )6

olur. Böylece

(W / L )3

( I O / 2)

=

(W / L )6

I7

úartı elde edilir. T5 ve T7 tranzistorlarının geçit-kaynak gerilimleri birbirine eúittir.

Kanal boyu modülasyonunun da ihmal edilebilece÷i gözönünde tutulursa

(W / L )5

IO

=

(W / L )7

I7

bulunur. Bütün bunların biraraya getirilmesiyle

(W / L )3

(W / L )4

1 (W / L )5

IO

=

= .

=

(W / L )6

(W / L )6

2 (W / L )7

2. I 7

úartı elde edilir.

(3.3)

3. 6

Rastgele dengesizlik

Rastgele dengesizlik. tranzistorların eúik gerilimleri ve W/L oranları

arasında imalat toleransları nedeniyle ortaya çıkan farklılıktan ileri gelir. T1 - T2

giriú tranzistorlarının ve T3 -T4 yük tranzistorlarının geometrisindeki (W/L

oranlarındaki) toleranslar nedeniyle aynı kutuplama úartları altında bu tranzistorların

savak akımları, yahut prosesteki farklılıklar nedeniyle aynı savak akımı için gereken

kutuplama gerilimleri, dolayısıyla eúik gerilimleri farklı olabilir.

ølk önce T3-T4 yük tranzistorlarının akımlarının aynı kutuplama úartları altında

farklı oldukları varsayılsın. Bu durumda, tranzistorların akımları

I3 =

1

1

(1 - H 1 ). I O z I 4 = .(1+ H 1 ). I O

2

2

olur. Bu dengesizli÷i düzeltmek için devrenin giriúine uygulanması gereken fark

giriú gerilimi

V OS 1 =

H1 . I O

g mi

(3.4)

de÷erindedir. Giriú dengesizlik geriliminin VOS1 bileúenini azaltmak üzere giriú

tranzistorlarının e÷imlerinin artttırılması yahut IO kutuplama akımının azaltılması

gerekir.

økinci adımda giriú elemanlarının boyutları ve eúik gerilimleri dengesiz, yük

elemanları ise dengeli olsun. Buna göre

(W / L )1 = (1 - H 2 ).(W / L )2

V T1 = V T 2 - ' V T

yazılabilir. Eúik gerilimlerinin dengesizli÷ini gidermek üzere 'VT farkı kadar bir

dengesizlik geriliminin giriúe uygulanması gerekli olur. Böylece giriú dengesizlik

geriliminin bu ikinci bileúeni

(3.5)

V OS 2 = ' V Ti

biçiminde ifade edilebilir. Giriú tranzistorlarındaki geometrik dengesizlikten ileri

gelen dengesizlik için

3. 7

k1

2

' I 1 = - H 2 . I 1 = - H 2 . .(V GS 1 - V T 1 )

2

H 2 .I O

VOS3=

gmi

(3.6)

yazılabilir. Ba÷ıntıdan fark edilebilece÷i gibi, VOS3 bileúeni, VOS1 bileúeninde oldu÷u

gibi, (W/L)1 oranı arttırılarak veya IO kutuplama akımı azaltılarak küçültülebilir. Her

iki etken de (VGS1 -VT1) farkını azaltacak yönde etkisini gösterir. 'VT farkı ise IO

kutuplama akımı ve (W/L)1 oranından ba÷ımsızdır.

Yük tranzistorlarının eúik gerilimleri arasında oluúacak bir fark da giriú

dengesizlik gerilimi üzerine etkili olur. Bu dengesizli÷i düzeltmek için giriúe

uygulanacak dengesizlik bileúeni

V OS 4 =

§g ·

' V T3-4

= ' V T3-4 .¨ m3 ¸

Kd1

© g m1 ¹

(3.7)

úeklinde ifade edilebilir.

Bütün bunların biraraya getirilip düzenlenmesiyle rastgele dengesizli÷e iliúkin

dengesizlik gerilimi için

§ g m3 ·

V OS = ' V T1-2 + ' V T3-4 .¨

¸

© g m1 ¹

+

(V GS -V T )1-2 ª ' (W / L1-2 ) '(W / L3-4 ) º

.«

¬ W / L1-2

2

W / L3-4 »¼

(3.8)

ba÷ıntısı elde edilir. Bu ba÷ıntıda ilk terim giriú tranzistorları eúik gerilimleri

arasındaki dengesizli÷i, ikinci terim yük elemanları eúik gerilimleri arasındaki

dengesizli÷i vermektedir. W/L oranlarının uygun seçilip yük tranzistorlarının

e÷imleri giriú tranzistorlarının e÷imlerinden küçük tutulursa, yük elemanlarının eúik

gerilimlerinden ileri gelen dengesizlik terimi minimize edilebilir. Üçüncü terim ise

giriú tranzistorları ve yük tranzistorlarına iliúkin W/L oranları arasındaki

dengesizli÷ini vermektedir. Giriú tranzistorlarının düúük bir (VGS - VT) farkı ile

çalıútırılmasıyla, bu terimi minimize etmek mümkündür. Pratikte (VGS - VT) farkı

50mV ile 100mV mertebesinde tutulur.

3. 8

3.1.2. Frekans kompanzasyonu

dB

-20dB/dek

20log|KVO|

20log|1/E1|

-40dB/dek

-60dB/dek

20log|1/E2|

sp1

0

-90o

sp2

sp3

Z

Z

-180o

-270o

I

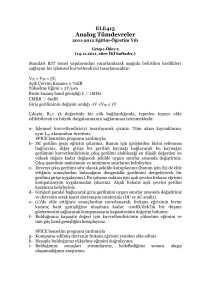

ùekil-3.3. øúlemsel kuvvetlendiricinin açik çevrim kazanç-frekans ve faz-frekans

karakteristi÷i.

øúlemsel kuvvetlendiriciler, genellikle, negatif geribesleme uygulanarak

çalıútırılırlar. Negatif geribesleme ile çalıúmada en önemli sorun kararlılık

sorunudur. ødeal iúlemsel kuvvetlendiricide band geniúli÷inin sonsuz ve bu nedenle

kuvvetlendiriciye osilasyon tehlikesi olmaksızın istenildi÷i kadar negatif

geribesleme uygulanabilmesine karúılık, gerçek bir iúlemsel kuvvetlendiricide

durum de÷iúiktir. Gereçek iúlemsel kuvvetlendiricinin frekans band geniúli÷i sonsuz

de÷ildir ve açık çevrimde çalıúmada transfer fonksiyonunun yüksek frekanslar

bölgesinde kutupları vardır. Gerçek iúlemsel kuvvetlendiricinin genlik-frekans ve

faz frekans e÷rileri ùekil-3.3'de görülmektedir.

Uygulanan bir negatif geribeslemenın frekans e÷risini ne úekilde

etkileyece÷i, yine ùekil-3.3 üzerinde gösterilmiútir. E1 kadar bir geribesleme

uygulanması durumunda E.K >> 1 ise geribeslemeli durumdaki kazanç 1/E1 olur.

Devrenin kararlı kalabilmesi için uygulanan negatif geribeslemenin hiçbir úekilde

pozitife dönmemesi, baúka bir deyiúle kazanç 0 dB de÷erine ulaúana kadar hiç bir

frekansta faz dönmesinin 180o olmaması gereklidir. Kazanç 0 dB de÷erini aldı÷ında

faz dönmesini 180o de÷erine tamamlayan de÷ere faz payı adı verilir. Faz

dönmesinin 180o oldu÷u frekansta kazancın 0dB ile olan farkına da kazanç payı

3. 9

ismi verilmektedir. Sistemin kararlı kalabilmesi için bu iki büyüklü÷ün de pozitif

olması gereklidir.

E1 kadar bir geribesleme uygulanması durumunda, úekilden de fark

edilebilece÷i gibi, faz dönmesi 180o den az olur ve devre kararlı kalır.

E2 kadar bir geribesleme uygulanması durumunda ise kesim frekansında faz

dönmesi 180o den büyük olur ve devre osilasyon yapar, yani kararsız olur. E.KV

çarpımına sistemin çevrim kazancı adı verilir. Devrenin kararlı olabilmesi için

çevrim kazancının faz payının arttırılması gerekir. Bu iúleme frekans

kompanzasyonu adı verilir. Kompanzasyon yapılmadan, devrenin kazancı KVf <

1/EX yapılamaz, kuvvetlendirici osilasyon yapar.

Frekans kompanzasyonu için en basit yöntem yapının band geniúli÷ini

daraltmaktır. Bunun için transfer fonksiyonuna bir düúük frekanslı bir baskın kutup

yerleútirilir, böylece çevrim kazancı E.KV = 1 iken faz kaymasının 180oC'den küçük

tutulması sa÷lanmıú olur. En zor durum E=1 durumudur ki, bu durumda çevrim

kazancı devre kazancına eúit olur. Kompanzasyonlu devre için elde edilen kazançfrekans ve faz-frekans e÷rileri ùekil-3.4'de verilmiútir. ùekilden görülebilece÷i gibi,

yapılan kompanzasyonla frekans e÷risinin en düúük açık çevrim kutbu frekansı olan

ZP1 açısal frekansına kadar -20 dB/dekat yahut 6 dB/okt'lık bir e÷imle düúmekte ve

bu bölgede faz -90o olmaktadır. Kompanzasyonlu durumdaki baskın kutup öyle

seçilir ki, ZP1 de kazanç 1, yani 0 dB, olur. Faz payı 45o oldu÷undan, sistem kararlı

kalır. Buna göre, kompanzasyonlu devrenin açık çevrim baskın kutbu

|s pD | =

1

.|s p1|

KV

(3.9)

biçiminde yazılabilir.

Baskın kutbu sPD olacak úekilde kompanze edilmiú ve frekans e÷risi

ùekil-3.4'deki biçimde de÷iúen bir kuvvetlendiriciye KVf > 1 olacak úekilde

geribesleme uygulansın. Bu durumda elde edilecek frekans e÷risi ùekil-3.5'de

verilmiútir. Zx açısal frekansında çevrim kazancı 1 olur. Faz payı ise 90o dir.

Devrenin -3dB düúme noktası band geniúli÷i Zx oldu÷una göre, devreye gerekenden

fazla kompanzasyon uygulanmıú ve band geniúli÷inin fazlaca daraltılmıú oldu÷u

kolayca fark edilebilir. Bunun baúlıca nedeni, devrenin birim kazanç band

geniúli÷ine

göre

kompanze

edilmiú,

ancak

daha

yüksek

3. 10

ùekil-3.4. Kompanzasyonlu durumda kazanç-frekans ve faz-frekans e÷rileri.

ùekil-.3.5. Kvf > 1 olması durumu.

3. 11

kazançta kullanılıyor olmasıdır. Genel amaçlı iúlemsel kuvvetlendiricilerde frekans

kompanzasyonu dıúarıdan uygulanarak çeúitli kazanç de÷erleri için esneklik

sa÷lanır. Tümdevre tekni÷inde ise, özellikle geniú çapta tümleútirme söz konusu

oldu÷unda bu yola baúvurma olana÷ı bulunmamaktadır; zira dıúarıdan eleman

ba÷lanması söz konusu de÷ildir. Daha etkin bir yöntem, önceki yapılarda yapıldı÷ı

gibi devrenin orijinal kutuplarına dokunulmadan transfer fonksiyonuna baskın

kutup eklenmesi yerine, en düúük açık çevrim kutbu sP1'in devreye eklenecek bir ek

kondansatör yardımıyla düúük frekanslar bölgesine kaydırılması yöntemidir. Bunun

için sP1 kutbunun hangi elemanlar tarafından belirlendi÷inin bilinmesi

gerekmektedir. Daha yüksek frekanslı sP2 ve sP3 kutupları ise yapılan iúlemden

etkilenmezler. Kullanılacak kompanzasyon kondansatörü de genellikle bir MOS

kapasite olarak kolaylıkla gerçekleútirilebilir. Bu durumda frekans e÷risi

kompanzasyonsuz haldeki ikinci kutba, sP2 kutbuna, kadar -20dB/dek yahut 6dB/okt'lık bir e÷imle düúmekte ve bu kutba ulaúıldı÷ında kazanç 1 de÷erini, faz

payı ise 45o de÷erinin almaktadır. Bu durumda elde edilen frekans ve faz e÷rileri

ùekil-3.6'da verilmiútir. ùekilden fark edilebilece÷i gibi, bu yöntemin

uygulanmasıyla, önceki duruma göre daha büyük bir band geniúli÷i elde

edilmektedir. Daha büyük band geniúli÷ine gereksinme duyulması durumunda ise,

ileride ele alınacak olan özel ve yüksek performanslı iúlemsel kuvvetlendirici

yapılarından yararlanılmaktadır.

ùekil-3.6. Kutup kaydırma yöntemi.

3. 12

Genel amaçlı kullanılmada frekans kompanzasyonu için baúvurulan en yaygın yol,

frekans e÷risinin en düúük açık çevrim kutbuna kadar -20dB/dek'lık e÷imle

düúmesini sa÷lamaktır. Bunun için genellikle ikinci kazanç katının giriú ve çıkıú

uçları arasına bir kompanzasyon kapasitesi ba÷lanır. Böylece, negatif kazançlı bu

ikinci kazanç katı bir integratöre dönüútürülmüú olur. Yapı Miller integratörü

oluúturdu÷undan,

bu

kompanzasyon

Miller

kompanzasyonu

olarak

isimlendirilmektedir.

CC

V2

+VP

R1

gm1 .V1

+VN

+VO

C1

R2

C2

gm2 .V2

V1 = VP - VN

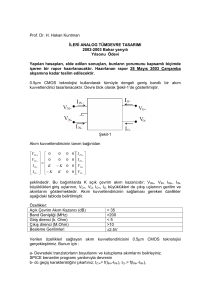

ùekil-3.7. øki kazanç katlı iúlemsel kuvvetlendiricinin küçük iúaret eúde÷er devresi.

Ele alınan iki katlı iúlemsel kuvvetlendirici yapısının frekans analizi küçük

iúaret eúde÷er devresi yardımıyla yapılabilir. Küçük iúaret eúde÷er devresi ùekil-3.7'

de verilmiútir. Devrenin yüksek frekanslar bölgesinde iki kutbu ve sa÷ yarı

düzlemde bir sıfırı vardır. Sıfır ve kutuplar

s0 =

CC

(3.10)

-1

g

(1+ m2 .R2 ).C C .R1

(3.11)

- g m 2 CC

C 2 C1 + C 2 CC + CC C1

(3.12)

s1 =

s2 =

g m2

úeklindedir. Bu sonuç bipolar tranzistorlu devreler için de geçerlidir. Ancak, eleman

özellikleri açısından ele alındı÷ında, iki yapı arasında belirgin farklar ortaya çıkar.

Bipolar yapıda sP2 ve sO nun de÷erleri, e÷imin yüksek olmasının bir sonucu olarak,

yüksektir ve bunların getirdi÷i faz kayması iúlemsel kuvvetlendiricinin birim kazanç

band geniúli÷i frekansında ihmal edilebilir. MOS tranzistorlu devrelerde ise böyle

3. 13

de÷ildir. MOS tranzistorun e÷iminin düúük olması nedeniyle sorun çıkar. sP2 ve sO

iúlemsel kuvvetlendiricinin Z1 = gm1/CC birim kazanç band geniúli÷ine daha yakın

olurlar. C1 << CC ve C2 úartı altında

s2

Z1

g m2 . C C

g m1 . C 2

g

= m2

g m1

=-

s0

Z1

olur. Sa÷ yarıdüzlemdeki sıfır birim kazanç band geniúli÷ine iki katın e÷imlerinin

oranıyla ba÷lıdır.

Fiziksel olarak kompanzasyon kapasitesi yüksek frekanslarda do÷rudan

do÷ruya ileri yönde bir iúaret yolu oluúturur ve ikinci kat tranzistorunun geçidi ile

savak ucunu kısa devre ederek bu tranzistoru diyot ba÷lı tranzistora dönüútürür. C1

ve C2 nin etkisi ihmal edilirse, alçak frekanslarda integratör iúlevini yerine getiren

ikinci kat tranzistoru, yüksek frekanslarda kompanzasyon kapasitesinin etkisiyle

diyot ba÷lı tranzistor biçiminde ilk kata yük olarak gelir. Bunun direnci 1/gm2

oldu÷undan, yüksek frekanslarda kazanç gm1/gm2 biçimini alır. Bu kazancın iúareti

alçak frekanslardaki kazancınkinin tersidir; bu nedenle ,uygulanan kompanzasyon,

herhangi bir negatif geribeslemeyi pozitif geribeslemeye çevirir.

Sorunu gidermek üzere bir yaklaúım, çıkıútan geriye do÷ru kompanzasyon

kapasitesi yolu üzerine bir kaynak izleyici koymak, böylece ileri yönde geçiúi

engellemektir. Ancak, bu yöntem fazla eleman ve kutuplama akımı gerektirir. Böyle

bir yapı örne÷i ùekil-3.8'de verilmiútir.

Daha basit bir yöntem, kompanzasyon kapasitesine seri bir sıfırlama direnci

getirmektir. Bu yöntemin uygulanması, ùekil-3.9'da gösterilmiútir. Bu durumda

devrenin sıfırı

s0 =

1

ª 1

º

- RZ »

C C .«

¬ g m2

¼

(3.13)

ba÷ıntısıyla verilmektedir. Bu ba÷ıntıya göre, RZ = 1/gm2 yapıldı÷ında, sıfır sonsuza

kayar ve etkisi giderilir. RZ daha da arttırılırsa, sıfır sol yarıdüzleme kayar ve

kuvvetlendiricinin faz payını iyileútirir.

3. 14

CC

+1

V2

+VP

R1

+VN

+VO

C1

gm1.V1

R2

C2

gm2.V2

V1 = VP - VN

ùekil-3.8. Kompanzasyon yolu üzerine kaynak izleyici yerleútirilmesi.

Di÷er bir sorun kapasitif yüklenme sorunudur. Bu durumda baskın olmayan kutup

ikinci katın e÷iminin ilk katın e÷imine oranına ve yük kapasitesinin kompanzasyon

kapasitesine oranına ba÷lıdır. ÿlk ve ikinci kat e÷imleri benzer ve yük kapasitesi ile

kompanzasyon kapasitesi aynı mertebede ise, birim kazançta faz payı azalır.

CC

V2

+VP

R1

+VN

RZ

gm1.V1

+VO

C1

R2

gm2.V2

V1= VP - VN

ùekil-3.9a. Sıfırlama direnci.

C2

3. 15

Im

artan RZ

RZ = 0

Re

ùekil-3.9b. Sıfırlama direncinin sıfıra etkisi

3.1.3. Kompanze edilmiú CMOS øúlemsel kuvvetlendiricinin geçici hal cevabı,

yükselme e÷imi

CC

_

gm1.Vin

+

+VO

ùekil-3.10. Yükselme e÷imini incelemek için kullanılan model.

øúlemsel kuvvetlendirici, kompanzasyonlu durumda, ZPD << Z <<ZP1

aralı÷ında çalıútırılsın. Bu aralıkta kuvvetlendiricinin giriú katı frekanstan ba÷ımsız

bir gerilim kontrollu akım kayna÷ı, ikinci kat ise CC kompanzasyon kapasitesi giriú

ile çıkıú uçları arasına ba÷lanmıú ve davranıúı frekanstan ba÷ımsız olan ideal bir

kuvvetlendirici ile temsil edilerek modellenebilir. Bu yoldan hareket edilerek

oluúturulan model, ùekil-3.10 da verilmiútir. Devreden hareket edilirse VO çıkıú

gerilimi için

3. 16

V O (s) =

g mi

.V IN (s)

s. C C

(3.14)

ba÷ıntısı elde edilir. jZ domenine geçilirse, devrenin kazancının modülü

KV (jZ ) =

g mi

(3.15)

jZ CC

olur. sp2 >> Z1 úartı altında birim kazanç band geniúli÷i

Z1 =

g mi

(3.16)

CC

olur. Yapının transfer fonksiyonu

KV (s) =

KO

s

1s p1

(3.17)

biçiminde ifade edilebilir. Bu úekilde modellenen iúlemsel kuvvetlendirici evirici

yapısı içine alınarak yükselme e÷imi incelensin. Devrenin giriúine

vin (t) = V 1 .u(t)

úeklinde bir basamak gerilimi uygulansın. Bu durumda elde edilecek çıkıú iúareti

t

ª

vo (t) = - V 1 .u(t).K O .«1 - exp(W

¬

º

)»

¼

(3.18)

olur. Ba÷ıntıdan fark edilebilece÷i gibi, giriúe küçük genlikli bir basamak iúareti

uygulanması durumunda çıkıú iúareti üstel bir de÷iúim göstermektedir. Giriúe büyük

genlikli bir iúaret uygulanması durumunda ise do÷rusal (sabit e÷imli) bir yükselme

ve düúme elde edilir. Baúka bir deyiúle, çıkıú iúaretinin de÷iúim hızının alabilece÷i

maksimum bir de÷er bulunmaktadır ve çıkıú iúareti en fazla bu hızla de÷iúebilir.

Çıkıú iúaretinin maksimum de÷iúim hızı yükselme e÷imi olarak isimlendirilir. Çıkıú

iúaretinin küçük ve büyük genlikli giriú iúaretleri için ne úekilde de÷iúece÷i ùekil3.11 'de gösterilmiútir. Yükselme e÷imi, iúlemsel kuvvetlendiricinin çalıútırıldı÷ı

devre yapısına göre farklılık gösterebilir. Bu bölümde, iki kazanç katlı

kuvvetlendirici yapısının faz döndüren kuvvetlendirici ve gerilim izleyici olarak

çalıútırılması durumları ele alınacaktır.

3. 17

R

Vin

_

+

R

+VO

Vin

kücük iúaret

t1

t

t2

VO

t

büyük iúaret

yükselme

e÷imi

VO

ùekil-3.11. Çıkıú iúaretinin küçük ve büyük genlikli iúaretler için de÷iúimi.

R

+VDD

T3

Vin

CC

T4

IO

R

IO

_

T2

T1

kesimde

+

V1

0

+VO

0

IO

-V1

-VSS

ùekil-3.12. Faz döndüren kuvvetlendirici.

Faz döndüren kuvvetlendirici yapısı içinde yer alan iúlemsel kuvvetlendirici bloku

ùekil-3.12'de verilmiútir. VIN giriú gerilimi 0 iken T1 ve T2 tranzistorları eúit

3. 18

gerilimlerle kutuplanmıúlardır, bu nedenle bu tranzistorların akımları da birbirine

eúit ve IO/2 de÷erinde olurlar. Giriúe úekilde gösterilen yönde büyük genlikli bir

basamak iúareti uygulandı÷ı varsayılsın. Bu durumda T1 tranzistoru iyice iletime

sürülür ve IO akımının tümünü akıtır. T2 tranzistoru ise kesime sürülür ve akımı sıfır

olur. T1 tranzistorundan akan IO akımı diyot ba÷lı T3 tranzistorundan ve akım aynası

dolayısıyla yansıyarak T4 tranzistorundan da akar ve CC kondansatörünü doldurur.

Sabit akımla dolan kondansatörün uçlarındaki gerilim zamanla lineer olarak, yani

sabit e÷imle, artar. Kompanzasyon kapasitesi, negatif kazançlı ikinci kazanç katı ile

birlikte bir integral alıcı devre oluúturdu÷undan, çıkıú iúaretinin yükselme e÷imi

SR =

IO

dV O

=

dt maks

CC

(3.19)

olur. Bilindi÷i gibi, kompanzasyon kapasitesinin de÷eri

CC =

g mi

(3.20)

Z1

ba÷ıntısıyla, giriú tranzistorlarının e÷imi ve seçilmiú olan birim kazanç band

geniúli÷i cinsinden ifade edilmektedir. Giriú katının e÷imi

g mi =

W

L

P .C OX . . I O

(3.21)

oldu÷undan, çıkıú iúaretinin yükselme e÷imi

SR =

I O .Z 1

= Z1 .

g mi

IO

W

P .C OX .

L

(3.22)

olur. Faz döndüren kuvvetlendirici yapısının yükselme e÷imi, ba÷ıntıdan fark

edilebilece÷i gibi, birim kazanç band geniúli÷i arttırılarak, giriú katının kutuplama

akımı arttırılarak, yahut giriú tranzistorlarının (W/L) oranları azaltılarak arttırılabilir.

MOS tranzistorlarda e÷imin de÷eri bipolar tranzistorlara göre çok düúüktür.

Sa÷lanacak kazanç ve dengesizlik gibi olaylar ele alındı÷ında, bu durum önemli bir

sakınca oluúturmaktadır. Ancak, yükselme e÷imi dikkate alındı÷ında, MOS

yapılarda elde edilebilecek yükselme e÷iminin, aynı özellikteki bipolar iúlemsel

kuvvetlendiricidekinden daha yüksek de÷erler elde edilebilece÷i görülür. Bunun

baúlıca nedeni, verilen belirli bir birim kazanç band geniúli÷i için (3.16) ba÷ıntısı

uyarında, e÷imin düúük olmasından ötürü, bulunacak CC kompanzasyon kapasitesi

de÷erinin daha küçük olmasıdır.

3. 19

Benzer bir inceleme, negatif yönde uygulanacak giriú basamak iúaretleri

için de yapılabilir. Yükselme e÷imi

SR =

IO

CC

(3.23)

olur.

Gerilim izleyici (faz döndürmeyen kuvvetlendirici) için yükselme e÷imi

Vin

V1

_

t

+

Vin

-

+

+VO VO

V1

t

ùekil-3.13. Gerilim izleyici ve basamak yanıtı.

Gerilim izleyici yapısı ve bunun basamak iúaretine cevabı ùekil-3.13 'de

verilmiútir. ùekilden kolayca izlenebilece÷i gibi, giriú iúaretinin yükselen kenarına

karúı düúen çıkıú iúaretinde ilk önce basamak úeklinde bir yükselme, daha sonra ise

rampa biçimli sabit e÷imli bir yükselme ile karúılaúılmaktadır. Giriú iúaretinin düúen

kenarına karúı düúen çıkıú iúareti ise, yükselen kenardakinden farklı olarak, yavaú ve

sabit e÷imli bir de÷iúim izlemektedir. Bu iki durum ayrı ayrı ele alınsın. Faz

döndürmeyen kuvvetlendiricinin , ùekil-3.14'deki gibi, bir giriú katı ve integratör

olarak ele alınmıú ikinci kazanç katı modeliyle temsil edildi÷i varsayılsın. Pozitif

yöndeki giriú basama÷ına cevabı inceleyelim.

IO akım kayna÷ına gelen eúde÷er da÷ılmıú kapasite oldukça büyük de÷erlidir. T1

ve T2 tranzistorlarının kaynakları bunların kendi tabanlarına ba÷lıdır. Baúka bir

deyiúle, bunlar p kuyulu olarak gerçekleútirilmiúlerdir ve her birinin kendi tabanı

bulunmaktadır. Bu úekilde oluúturulan tranzistorlarda kuyu ve esas taban arasında

büyük de÷erli bir kapasitif etki ortaya çıkar. Öte yandan giriúe uygulanan basamak

biçimli gerilim sıçraması vi(t) = V1.u(t) biçiminde birim basamak fonksiyonu

3. 20

cinsinden verilebilir. Bu durumda T1 ve T3 tranzistorları kesimde, T2 tranzistoru

iletimde oldu÷undan,T2 tranzistorundan IO + iw de÷erinde bir akım akar. Ortak

kaynak noktasında Cw da÷ılmıú kapasitesi ve IO akım kayna÷ının oluúturdu÷u

empedans, T2 tranzistorunun kayna÷ından içeriye do÷ru bakıldı÷ında görülen 1/gm2

empedansından çok büyük olur. Bu nedenle

v w (t) = vin (t)

+VDD

T3

CC

T4

IO+iw

_

IO+i w

T1 T2

Vin

+

VO

iw

IO

CW

T1, T 3, T4 kesimde

T2 iletimde

-VSS

+VDD

T3

CC

T4

IO - i w

IO - i w

IO - i w

T1

Vin

CW

iw

_

T2

IO

-V SS

+

VO

T1 , T3 , T4 iletimde

T2 kesimde

ùekil- 3.14. Gerilim izleyicinin pozitif ve negatif gerilim sıçramaları için modellenmesi

3. 21

yazılabilir. Böylece Cw kapasitesinden akan ıw akımı

i w (t) = C w

dv w (t)

dvin

= Cw

dt

dt

biçiminde ifade edilebilir. Giriúe uygulanan basamak iúaretine

karúı düúen çıkıú iúareti de÷iúimi

1 t

³ ( I O + i w )dt

CC 0

IO

C w t dvin

³

t +

dt

v o (t) =

CC

C C 0 dt

v o (t) =

v o (t) =

IO

Cw

t +

V 1 u(t)

CC

CC

(3.24)

olur. Bu ba÷ıntıdaki ilk terim zamanla lineer de÷iúen bir yükselme, ikinci terim ise

ilk baúta izlenen basamak biçimli yükselmeyi verir.

Kuvvetlendiriciye negatif bir gerilim sıçraması uygulandı÷ında, T2

tranzistoru kesime, T1, T3 ve T4 tranzistorları ise iletime sürülürler. Bu durumda

iletime sürülen tranzistorlardan IO - ıw akımı akar. CC nin bir ucu görünürde toprak

potansiyelinde, Cw ise Vw potansiyeli ile toprak arasında olur. Bu durumda çıkıú

iúaretinin de÷iúim hızı

dv o

I O - iw

iw

=

= dt

CC

Cw

Cw

iw = I O

Cc + C w

dv o

IO

= dt

CC + C w

(3.25)

biçiminde ifade edilebilir. Negatif yöndeki yükselme e÷imi, yapının eúde÷erinde Cw

da÷ılmıú kapasitesinin bulunması nedeniye, IO/CC de÷erinden IO/(CC+Cw) de÷erine

düúmekte, yani 1 + Cw/CC oranında azalmaktadır.

3. 22

3.1.4. CMOS iúlemsel kuvvetlendiricilerde gürültü

CMOS iúlemsel kuvvetlendiricilerde gürültü, yapıda iúaret yolu üzerindeki

tranzistorların her biri için gürültü gerilimi kayna÷ı da dikkate alınarak incelenebilir.

øki kazanç katlı iúlemsel kuvvetlendirici yapısı için elde edilen gürültü eúde÷eri

ùekil-3.15'de verilmiútir. Böyle bir yapıda, gürültü, eúde÷er bipolar yapıdakine göre

10 kat daha yüksektir. Yapıda yer alan üç kat, kat giriúine indirgenmiú eúde÷er

gürültü gerilimi yakna÷ı ve gürültüsüz kuvvetlendirici cinsinden ayrı ayrı

modellenmiútir. T5 akım kayna÷ı tranzistorundan ileri gelen gürültü ise, iúlemsel

kuvvetlendiricinin CMRR ortak iúareti bastırma miktarı oranında bastırılır ve etkisiz

kılınır.

+VDD

vn3 vn4

T3

VA

vn1

vin

T1

T4

vn6

T6

Av

n2

vn8

T8

T2

vo

vn9

T9

vn7

T5

T7

VB

vi

vnd

-VSS

+

Kd

_

A

KS

vns

B

KO

vno

vo

ùekil-3.15.øki kazanç katlı iúlemsel kuvvetlendiricide gürültü eúde÷eri.

3. 23

Giriú tranzistorlarına iliúkin vn1 ve vn2 gürültü kaynaklarından A noktasına

yansıyan gürültü,

Kd =

gm

vA vA

=

=

vn1 v n 2 g o 2 + g o 4

(3.26)

gürültü kazancı ile ifade edilebilir. Benzer úekilde hareket edilerek, T3 ve T4

tranzistorlarına iliúkin vn3 ve vn4 gürültü kaynaklarından A noktasına kadar gürültü

kazancı da tanımlanabilir. vn3 gürültü geriliminden yansıyan akım bileúeni

i = g m3 . v n 3

olur. Bu bileúen T4 tranzistoru ile aynalanır. Böylece

vA =

g m3 .v n 3

go2 + go4

elde edilir. Benzer úekilde, T4 tranzistoruna iliúkin vn4 gürültü gerilimi için

Kv =

g m3

vA

vA

=

=

go2 + go4

vn3

vn4

(3.27)

yazılabilir. Bütün bu gürültü kaynaklarının A noktasında oluúturaca÷ı gürültü gücü

dikkate alınır ve bu gürültüyü oluúturan gerilim fark kuvvetlendiricisinin giriúine

indirgenirse

v 2A = K 2d .( v n12 + v n2 2 ) + K v2 .( v n3 2 + vn 4 2 )

oldu÷undan

2

2

nd

2

v = v n1 + v n 2

2

§g ·

+ ¨¨ m 4 ¸¸ . v n 3 2 + v n 4 2

© g m1 ¹

(3.28)

elde edilir. Ba÷ıntıdan fark edilebilece÷i gibi, vnd2 'yi minimize etmek için n1 ve vn2

'nin etkilerinin düúük tutulması, ve gm4 << gm1 úartının sa÷lanması gerekli

olmaktadır. Bu úartlardan ilkinin yerine gelebilmesi için T1-T2 çiftini oluúturan

tranzistorların W.L yüzeyi ile bunların gm e÷iminin büyük tutulması gerekir.

Bu

ise kırmık üzerinde yer kaybı ve ek güç harcaması anlamına gelmektedir.

gm4 <<

3. 24

gm1 úarının sa÷lanması için kutuplamanın elverdi÷i oranda yük tranzistorlarının L

kanal boyu arttırılmalıdır. Bu ise, giriú ve yük tranzistorları için ayrılan yüzeyin belli

oldu÷u varsayımı altında, T1 - T2 çiftine ayrılan alan büyük, T3-T4 çiftine ayrılan

alanın kiçik tutulaca÷ı anlamına gelir.

Bir NMOS tranzistordaki 1/f gürültüsü, bir p kanallı tranzistordakine göre 3

defa kadar daha yüksek olur.

øki kazanç katı arasında seviye öteleme amacıyla yerleútirilmiú olan ve T6T7 tranzistorları ile kurulan kaynak izleyici için benzer yoldan hareket edilerek

eúde÷er gürültü gerilimi hesaplanırsa

v 2ns

= vn6

2

§ g m7 ·2

2

+ ¨

¸ .vn7

© g m6 ¹

(3.29)

elde edilir. Bu eúde÷er gerilim, aúa÷ıdaki biçimde iúlemsel kuvvetlendiricinin

giriúine de indirgenebilir:

2

n

v = v

2

nd

v 2ns

+ 2

Kd

oldu÷undan

2

2

nd

2

v = v n1 + v n 2

2

§g ·

+ ¨¨ m 4 ¸¸ . v n 3 2 + v n 4 2

© g m1 ¹

2

ª

º

§ g m7 ·

2

¸ .vn 7 2 »

«v n 6 + ¨

¨g ¸

«¬

»¼

© m6 ¹

+

2

Kd

(3.30))

elde edilir. Ba÷ıntıdan kolayca fark edilebilece÷i gibi, Kd2 >> 1 úartının sa÷landı÷ı

alçak frekanslarda vns kolayca ihmal edilebilir. Kazancın düútü÷ü yüksek

frekanslarda ise durum böyle de÷ildir. Bu gürültü etkisini düúük düzeyde tutabilmek

üzere gm6 e÷iminin büyük tutulması gerekece÷i kolayca fark edilebilir.

økinci kazanç katından ileri gelen gürültü ise önemli de÷ildir ve eúde÷er

giriú gürültü gerilimine katkısı ihmal edilebilir.

3. 25

3.2. Yüksek baúarımlı iúlemsel kuvvetlendiriciler

Buraya kadar ele alınan basit iki kazanç katlı iúlemsel

kuvvetlendirici yapıları, daha çok, sC süzgeci yapılarına uygun topolojilerdir.

Yüksek frekanslı aktif süzgeç yapıları, yüksek do÷ruluklu ve hızlı D/A ve A/D

çeviriciler, enstrümantasyon kuvvetlendiricileri gibi uygulamalar söz konusu

oldu÷unda, bu tür basit yapılar yetersiz kalırlar. Standart iki katlı yapının en

önemli sakıncası, bu tür yapılarda kazancın düúük olmasıdır. øúlemsel

kuvvetlendiricinin kazancı, kat kazançlarının çarpımı ile belirlenir. Ele alınmıú

olan iki katlı yapılarda açık çevrim kazancı 80dB kadar olur. Yapıya ek katlar

yerleútirilerek kazancın arttırılması yoluna gidilmesi uygun bir çözüm de÷ildir;

zira, ek katlarla beraber transfer fonksiyonunun kutup sayısı da artar ve frekans

kompanzasyonu zorlaúır. Bu nedenle, kazancın yükseltilmesi için yapıda

de÷iúiklikler yapılması gerekli olur. Bunun yanısıra, bazı uygulamalarda, band

geniúli÷inin büyük olması da gerekebilir.

Yüksek performanslı iúlemsel kuvvetlendiriciler , yüksek de÷erde birim

kazanç band geniúli÷i (kazanç-band geniúli÷i çarpımı) ve yükselme e÷imi elde

etmek üzere kullanılan yapılardır. Bu tür iúlemsel kuvvetlendiriciler genellikle

daha

fazla

güç

harcarlar.

daha

önce

de

belirtildi÷i

gibi,

iúlemsel

kuvvetlendiriciler genellikle iki grupta incelenebilir: Bunlardan birincisi, geçiú

iletkenli÷i kuvvetlendiricisi, ya da kısa adıyla OTA’dır. Bu tür yapıların çıkıú

direnci oldukça yüksektir. økinci grup ise, çıkıú direnci düúük olan iúlemsel

kuvvetlendirici yapılarıdır. Yüksek çıkıú dirençli iúlemsel kuvvetlendirici

yapıları için tamponlanmamıú (ayırıcı çıkıú katı kullanılmamıú) iúlemsel

kuvvetlendiriciler deyimi de kullanılmaktadır. øúlemsel kuvvetlendiricilere

iliúkin bölümde buraya kadar ele alınan yapılar tamponlanmamıú iúlemsel

kuvvetlendirici yapılarıdır. Tamponlanmamıú iúlemsel kuvvetlendiriciler düúük

de÷erli yükleri süremezler. Bu nedenle, bazı özel uygulamalar için kapasitif

yükleri ve düúük empedanslı yükleri sürmek üzere yararlanılabilecek

yöntemlerin araútırılması gerekir.

3. 26

Yukarıda bahsedilen iki grup iúlemsel kuvvetlendirici arasındaki temel

fark, yüksek performanslı iúlemsel kuvvetlendiricilerde kullanılan çıkıú katı

yapılarından ileri gelir. Bu çıkıú katları sadece MOS tranzistorlarla

kurulabilece÷i gibi, MOS tranzistorlar ve CMOS teknolojisinde bulunan bipolar

tranzistorlardan yararlanılarak da oluúturulabilir. Devreye çıkıú katı eklenmesi,

açık çevrim transfer fonksiyonuna ek kutuplar gelmesine neden olur ki, bunun

da frekans kompanzasyonunu zorlaútıraca÷ı açıktır.

Bazı uygulamalarda düúük gürültülü iúlemsel kuvvetlendiricilere

gereksinme duyulabilir. Düúük gürültülü iúlemsel kuvvetlendirici elde etmek

üzere,kuvvetlendiricinin giriú katında PMOS tranzistorlar kullanılır.

Bu bölümde yüksek performanslı iúlemsel kuvvetlendirici yapıları ele alınarak

incelenecektir.

3.2.1. Ortak kaynak-ortak geçitli kuvvetlendirici ile iúlemsel kuvvetlendirici

gerçekleútirilmesi

Bir çok uygulamada kat kazancının yeteri kadar büyük de÷erli olması,

tek bir ortak kaynak-ortak geçitli kuvvetlendirici kullanılarak sa÷lanabilir. (ùekil3.16). Böyle bir çözümün yararı, tek bir kat ile daha iyi bir frekans e÷risi elde

edilebilmesidir. Alçak frekanslarda çalıúmada, devrenin sa÷ladı÷ı kazanç, iki katlı

kuvvetlendiricinin sa÷ladı÷ı kazançla aynı olur. Ancak, yapıda çıkıú dü÷ümünün

empedansı, iki katlı yapının çıkıú empedansına göre gm.ro oranında yükseltilmiútir.

Devrenin gerilim kazancı ise giriú tranzistorlarının e÷imi ile çıkıú dü÷ümü

empedansının çarpımıdir. Bu yapının sa÷ladı÷ı önemli bir yarar, baskın kutbun CL

yük kapasitesi ile belirlenmesi, baúka bir deyiúle, bu kapasitenin aynı zamanda

kompanzasyon kapasitesi iúlevini yerine getirmesidir. øki kazanç katlı yapıda ise,

daha önceki bölümlerde gösterildi÷i gibi, durum böyle de÷ildir. øki katlı

kuvvetlendiricide yük kapasitesinin arttırılması baskın olmayan kutbu etkiler ve faz

payını azaltır. Burada ele alınan tek katlı yapıda ise yük kapasitesinin arttırılması

faz payını iyileútirmektedir. Yapının transfer donksiyonunda T3 ve T4 kaskod

tranzistorlarının ve akım kayna÷ı tranzistorlarının geçit-kaynak kapasitelerinden

ileri gelen baskın olmayan kutup bulunur. Bunun frekansı tranzistorların geçiú

frekansı mertebesindedir.

3. 27

+VDD

IO '

VK2

T10

A

IO '

B

VK3

IO/2 IO/2

+

VI

-

T1

I

T11

T7

I

T2

C

D

T8

VO

IO

T5

T6

T3

T4

CL

T9

VK1

-VSS

ùekil-3.16. Ortak kaynak- ortak geçitli kuvvetlendirici yapısı ile iúlemsel

kuvvetlendirici gerçekleútirilmesi.

MOS tranzistorlarda geçiú frekansı

fT =

gm

C gs

úeklinde ifade edilir. Etkin kanal uzunlu÷unun 4Pm, (VGS-VT) farkının birkaç yüz

milivolt mertebesinde olması durumunda, baskın olmayan kutup birkaç yüz MHz

mertebesinde olur. Giriú tranzistorlarının e÷imlerinin uygun seçilmeleri

durumunda, iyi bir faz payı ile yüksek de÷erli bir kapalı çevrim band geniúli÷i elde

edilebilir. Ancak, kaskod devrenin etkisiyle, çıkıú iúaretinin dalgalanma aralı÷ının

iki kazanç katlı yapıya göre biraz daha düúük olaca÷ını belirtmekte yarar vardır.

ùekil-3.16'daki yapıda T3-T8 tranzistorlarıyla oluúturulan blok, kompozit

yükü oluúturur. Bu yük katlanmıú yüktür; baúka bir deyiúle, eúlenik tranzistorlar

kullanılmasıyla yük VDD geriliminden ayrılmıú ve -VSS gerilimine götürülmüútür.

Sükunet durumunda, IO akımı T1 -T2 tranzistorlarına eú olarak paylaútırılmaktadır.

3. 28

T10 - T11 tranzistorları VK1 gerilimi ile IO' akımını akıtacak biçimde kutuplanırlar.

Böylece, I akımı

I = IO ' -

1

IO

2

olur. Giriúe bir 'Vın gerilimi uygulansın. Bu durumda savak akımları +'IO =

gm1.'Vin/2 kadar de÷iúir. IO' akımı sabit kalır. Bu nedenle, I akımları da ±'I kadar

de÷iúir. T3-T6 tranzistorları kaskod bir akım aynası oluútururlar. Böylece, T3-T5

deki de÷iúim, T4-T6 koluna yansıtılmıú olur. Böylece, iúlemsel kuvvetlendiricinin

çıkıú gerilimi de÷iúimi

' v o = g m1 . RO . ' vin

ve kazancı da

K v = - g m1 .RO

(3.31))

olur. Yapının çıkıú direnci ise

RO =

go2

g m6 . r o 6

1

( g o 2 + g o11 )

+

g m8 . r o8

(3.32))

biçiminde ifade edilebilir. RO.CL zaman sabiti transfer fonsiyonunun baskın

kutbunu belirler:

s p1

( g + g o11 )

g o2

+ o2

g .r o6

g m8 8. r o8

1

= m6

C L RO

CL

(3.33))

Baskın olmayan kutuplar, A, B, C dü÷ümlerindeki düúük empedans de÷erlerinin

da÷ılmıú kapasitelerle yüklenmeleriyle belirlenir.

A dü÷ümündeki etkin direnç 1/gm7 , B dü÷ümündeki etkin direnç 1/gm8, C

dü÷ümündeki etkin direnç ise 1/gm6 + 1/gm4 de÷erindedir. Buna göre

| s p 2 | ,| s p 3 | ,| s p 4 |!! | s p1 |

olur. sp1 ve KVO açık çevrim kazancına ba÷lı olarak iúlemsel kuvvetlendirici

kararsız olabilir.

3. 29

3.2.2. Wilson (veya kaskod) akım kayna÷ı kullanılması

+VDD

T3

T1

T4

T2

I

+V

Iref

-VSS

ùekil-3.17. Wilson akım kayna÷ının yük olarak kullanılması.

Kazancı arttırmanın di÷er bir yolu, Wilson (veya kaskod) akım kayna÷ı

devrelerinden yararlanmaktır. Kaskod akım kayna÷ının yük olarak kullanılıúı ùekil3.17'de verilmiútir. Kaskod akım kayna÷ının çıkıú direnci

RO = r o 2 . g m2 .

g m3

g m1

go3 + go

biçiminde ifade edilir. Bu ba÷ıntıda rO = 1/gO büyüklü÷ü Iref akım kayna÷ının çıkıú

direncini göstermektedir. Yapıda

r o 2 . g m 2 !! 1 , RO !!

1

g o3 + g o

olur. V geriliminin alabilece÷i en büyük de÷erde T2 tranzistoru doymada

kalmalıdır. Buna göre

v maks = V DD - 2.|V GS 3| +|V TP |

3. 30

olur. Kaskod akım kayna÷ının bir iúlemsel kuvvetlendirici yapısında kullanılıúı

ùekil-3.18'de gösterilmiútir. T3-T6 tranzistorları , yine kaskod devre olarak

düzenlenmiú olan fark kuvvetlendiricisinin yükünü oluútururlar. Bu yapıda

(W / L )1 = (W / L )2 , (W / L )3 = (W / L )4

(W / L )5 = (W / L )6 , (W / L )7 = (W / L )8

olarak seçilir. Fark kuvvetlendiricisinin çıkıú direnci

1

RO =

go4

g m6 . r o 6

+

(3.34)

go2

g m8 . r o 3

ba÷ıntısıyla ifade edilebilir.

+VDD

T3

T11

T4

VK1

T5

T6

T12

T10

T7

T8

T14

+VO

VK2

CC

T1

-

T2

+

T13

T9

VK3

-VSS

ùekil-3.18. Wilson akım kayna÷ının iúlemsel kuvvetlendirici yapısında kullanılması.

g m 6 . r o 6 ve g m8 . r o8 !! 1

olması durumunda çıkıú direnci

RO !!

1

go4 + go2

olur. Fark kuvvetlendiricisinin sa÷ladı÷ı kazanç

3. 31

(3.35)

KV = - g m1 . RO

biçiminde yazılabilir. økinci kat ise kaynak izleyici olarak düzenlenmiútir. Yapıdaki

T14 tranzistoru kompanzasyon kondansatörüne seri olarak ba÷lanmıútır. Direnç

bölgesinde çalıúan bu tranzistor RZ sıfırlama direnci görevini üstlenmektedir. RZ

sıfırlama direncinin MOS tümdevre tekni÷inde daima bu úekilde çalıúan bir

tranzistorla gerçekleútirildi÷ini belirtmekte yarar vardır. Yapıda ek elemanlar

kullanıldı÷ı için, bu tür bir iúlemsel kuvvetlendiricinin rastgele dengesizli÷i

genellikle büyük olur.

Yapıda, fark kuvvetlendiricisinin arkasına bir seviye öteleyici ve çıkıú katı

bloku ba÷lanmıútır. Seviye öteleyici ve CL yük kapasitesi nedeniyle devrenin

transfer fonksiyonunda ek kutuplar ortaya çıkar; bu kutuplar baskın kutup de÷ildir,

ancak yapının band geniúli÷ini sınırlayan birer etken olarak kendilerini gösterirler.

CC = CL olması durumunda, band geniúli÷i CL ile sınırlanır.

3.2.3. Tamponlanmıú iúlemsel kuvvetlendirici yapıları

Basit iki kazanç katlı kuvvetlendirici yapısına bir çıkıú katı eklenerek,

devrenin sadece büyük de÷erli kapasitif yükleri de÷il, aynı zamanda düúük

empedanslı yükleri sürmesi de sa÷lanabilir. Böyle bir devrenin blok úeması

ùekil-3.19’da verilmiútir. ølk yapı, tamponlanmamıú iúlemsel kuvvetlendirici

yapısını oluúturmaktadır. økinci kat ise birim kazançlı bir çıkıú katıdır.

+

+

VI

_

-

V2

1

tamponlanmamı

birim kazanclı

iúlemsel kuvvetlendirici

çıkıú katı

VO

ùekil-3.19. Yüksek performanslı iúlemsel kuvvetlendirici yapısı.

3. 32

Tamponlanmamıú iúlemsel kuvvetlendiricinin iki kazanç katı oldu÷u

düúünülecek olursa, eldeki üç katlı yapının nasıl kompanze edilece÷inin

belirlenmesi gerekir. Kompanzasyonsuz durumda iúlemsel kuvvetlendiricinin

açık çevrim kazancı

VO ( s)

V I ( s)

KVO

(3.36)

§ s

·§ s

·§ s

·

1¸¨

1¸¨

1¸

¨

© s p1 ' ¹© s p 2 ' ¹© s p 3 ' ¹

úeklindedir. Burada sp1’ ve sp2’ büyüklükleri, tamponlanmamıúm iúlemsel

kuvvetlendiricini kompanze edilmemiú durumdaki kutuplarını, sp3’ ise çıkıú

katının kutbunu göstermektedir. Burada sp1’< sp2’<sp3’ oldu÷u kabul edilecektir.

Yapıda CL yük kapasitesi arttıkça sp3’ azalacak, RL arttıkça sp3 artacaktır.

sp2

sp3'

jZ

V

sp2' sp1'

sp3

(a)

jZ

sp3'=sp3 sp2' sp1

V

(b)

ùekil-3.20. a) økinci ve üçüncü kata, b) ikinci kata Miller kompanzasyonu uygulanması

durumunda iúlemsel kuvvetlendiricinin kutuplarının yer e÷rileri.

3. 33

økinci ve üçüncü kata Miller kompanzasyonu uygulanırsa, ùekil-3.20a’da

görülen yeni kutuplar elde edilir. CC kapasitesinin de÷eri arttıkça, ikinci ve

üçüncü kutuplar jZ eksenine do÷ru bükülürler. Bu ise faz payının düúük

olmasına neden olur. Miller kompanzasyonu sadece ikinci kata uygulanırsa, bu

yeni durumda ùekil-3.20b’deki kutuplar elde edilir. Böylece kutupların jZ

eksenine do÷ru bükülmeleri ortadan kaldırılmıú olur. Ancak, çıkıú katının kutbu

ise daha önceki yerinde kalır. Bu iki yaklaúımdan hangisinin seçilece÷i, faz payı

için öngörülen de÷ere ba÷lıdır.

ùekil-3.21’de yukarıda blok úeması verilen yapının açık devre úeması

görülmektedir. ùekildeki iúlemsel kuvvetlendirici üç kattan oluúmaktadır. Giriú

katı bir fark kuvvetlendiricisidir. Bu katın çıkıúına bir ara kuvvetlendirici ile bir

çıkıú katı ba÷lanmıútır. T1,T3 ve T2,T4 eviricileri ara kuvvetlendiriciyi

oluútururlar. Bu katın görevi kazancı ve kompanzasyonu sa÷lamak, ayrıca T5 ve

T6 tranzistorlarını sürmektir. Çıkıú katı ise birim kazanç sa÷lamak üzere

düzenlenmiú bir geçiú iletkenli÷i katıdır.

Devredeki iki eviricinin giriú-çıkıú karakteristikleri ùekil-3.22’de

görülmektedir. ùekildeki a ve b e÷rileri sırasıyla T1, T3 ve T2,T4 eviricilerine

iliúkin karakteristiklerdir ve bunlar T5 ile T6 tranzistorlarını sürmek üzere

kullanılmaktadır. ùekilde belirtilen geçiú gerilimi

VC

VB V A

úeklinde tanımlanmıútır. VA ve VB büyüklükleri, T5 ve T6’yı kesime sürecek olan

evirici giriú gerilimleridir. Güç harcamasının düúük olabilmesi için VC

geriliminin sıfırdan büyük olması gerekir; ancak, kabul edilemeyecek

mertebedeki geçiú distorsiyonundan kaçınmak için, VC geriliminin çok büyük

tutulmaması gerekir. Bu kriter, eviricilerin uygun boyutlandırılmasıyla yerine

getirilebilir. Böylece, VC geriliminin sıfırdan büyük, ancak yeterince küçük

olması da sa÷lanmıú olur. Çıkıú katı B sınıfında çalıútırıldı÷ından, her bir evirici

için ayrı bir frekans kompanzasyonu gerekli olur.

MOS çıkıú katı kullanan CMOS iúlemsel kuvvetlendiricilere di÷er bir

örnek ùekil-3.23’de görülmektedir. Bu devre tamponlanmamıú iúlemsel

kuvvetlendirici ile negatif geribeslemeli çıkıú katı kombinezonundan oluúur.

3. 34

T7

T3

+VDD

T4

T6

Iref

VO

C1

giriú katı

RL

C2

_

T1

+

T2

T5

-VSS

ùekil-3.21. Düúük empedanslı yükleri sürmeye elveriúli CMOS iúlemsel kuvvetlendirici.

VO

T1-T3 eviricisi

VDD

T2 AKTøF

T2-T4 eviricisi

T2

DOYMADA

b

a

T1

DOYMADA

T1 AKTøF

VI

VA

VB

ùekil-3.22. ùekil-3.21.’deki eviricilere iliúkin giriú-çıkıú karakteristikleri.

Devredeki tamponlanmamıú iúlemsel kuvvetlendiricinin çıkıú katı, T16 ve T17

eviricilerini sürmek amacıyla kullanılmıútır. Devrede yer alan tamponlanmamıú

iúlemsel kuvvetlendirici genellikle aktif yüklü bir fark kuvvetlendiricisidir. T16

ve T17 tranzistorları ise evirici katını oluútururlar. A1 kuvvetlendiricisi ile T6

tranzistoru, çıkıútaki gerilim dalgalanmasının pozitif yarıperiyodu için birim

3. 35

kazanç sa÷lar. A2 ile T6A ise aynı iúlemi negatif yarıperiyotta gerçekleútirir. Çıkıú

katı AB sınıfında çalıútı÷ından, devrenin negatif yarıperiyodu, pozitif

yarıperiyodunun simetri÷i olur.

T16

+

+VDD

T4

T6

T9

_

A1

+

-

CD

-VOS+

VO

T8A

T8

T10

VK2

-

+

A

VK1

T13

T17

T12

T6A

T5

-VSS

ùekil-3.23. MOS çıkıú katı kullanan di÷er bir CMOS iúlemsel kuvvetlendirici yapısı.

3.2.4. Yüksek hızlı-yüksek frekanslı iúlemsel kuvvetlendiriciler

Bu bölümde, hızı ve kazanç-band geniúli÷i çarpımı iyileútirilmiú

iúlemsel kuvvetlendirici yapıları ele alınarak incelenecektir. Burada hız

kelimesiyle, devrenin giriúine bir darbe uygulanması durumunda cevap

verebilmesi için gereken minimum süre kastedilmektedir. Bu úart, yüksek bir

yükselme e÷imi de÷eri ve yerleúme zamanını (settling time) minimize etmek için

iyi bir faz payı özelli÷ini gerekli kılar. Bu tür iúlemsel kuvvetlendiricilerin

yükselme e÷imleri 100V/Psn den fazla ve büyük de÷erli kapasitif ve rezistif

yükler için kazanç-band geniúli÷i çarpımı da 20MHz’den büyük olmalıdır. Böyle

bir yüksek performans özelli÷i sa÷layabilmek üzere, genellikle çıkıú gerilimi

dalgalanma aralı÷ından fedakarlık yapılır.

Yüksek performanslı bir iúlemsel kuvvetlendirici yapısı ùekil-3.24’de

verilmiútir. Bu yapıdaki çıkıú katı, iki taban (kuyu) npn tranzistoru ile

gerçekleútirilen ve Darlington çifti olarak çalıúan A sınıfı bir kuvvetlendiriciden

oluúmaktadır. Yapıda bu tür bir Darlington çiftinin kullanılmasının amacı,

3. 36

çıkıúta yer alan eúde÷er bipolar tranzistorun E akım kazancını arttırmak, böylece

çıkıú akımının yüksek de÷erli olmasını sa÷lamaktır. Bu devrenin çıkıúından

alınabilecek en büyük gerilim de÷eri VDD-2.VBE olur.

øúlemsel kuvvetlendiricinin çıkıú direncini bulmak üzere

ùekil-

3.25a’daki eúde÷er yapı kullanılabilir. Bu yapıya iliúkin eúde÷er devre de ùekil3.25b’de görülmektedir. Eúde÷er devre yardımıyla çıkıú direnci hesaplanırsa

RO

R

( g ds 6 G ).( gS 1 gS 2 g m2 ) gS 1 . gS 2 '

| ds 6

g ds 6 . G.( gS 1 gS 2 ' g m1 ) g ds 6 ( gS 2 ' g m2 ).( gS 1 g m2 ) g m2 . R

(3.37)

+VDD

T10

T11

T12

T13

T3

T6

T4

T1

T8

T9

T2

R2

R1

+V2

R3

+V1

REXT

C

T5

VO

T7

-VSS

+Vref di÷er iki kat için

ùekil-3.24. Bipolar tranzistorlu çıkıú katlı iúlemsel kuvvetlendirici yapısı.

R2

R1

T2

T1

rds6

R

rp1

VO

+

V1

-

rp2

V2

+

VO

gds6

gm1(V1-V2)

gm2(VO-V2)

-

ùekil-3.25. ùekil-3.24’deki yapının çıkıú direncinin hesaplanması için yararlanılan

devre ve bu devrenin eúde÷eri.

3. 37

elde edilir. Devrede görülen 3k’luk direnç, T1 tranzistorunun kutuplamasını

karalı hale getirmek üzere kullanılmıútır. Bu direnç nedeniyle çıkıú direnci, basit

Darlington çiftindekine göre daha büyük olur.

T6

T1

T2

T4

T5

T3

ùekil-3.26. Çıkıú direncinin küçültülmesi.

ùekil-3.26’da gösterilen yapının kullanılmasıyla, çıkıú direncini daha da

küçültmek mümkündür. Bu devrenin çıkıú direnci hesaplanırsa

RO

Ri1

( 1 E F 1 ).( 1 E F 2 )

(3.38)

elde edilir. Bu ba÷ıntıdaki Ri1 direnci, T1 tranzistorunun bazından içeriye do÷ru

bakıldı÷ında görülen dirençtir. Bu tür iúlemsel kuvvetlendirici yapılarıyla

100MHz’e kadar kazanç-band geniúli÷i çarpımı ve r300V/Psn ‘lik yükselme

e÷imi de÷erleri elde edilebilir. Devreyle CL = 100 pF mertebesinde yük

kapasitelerini sürmek mümkündür. Açık çevrim çıkıú direnci 100 Ohm ve faz

payı da 45o mertebesinde olur.

Yüksek hızlı iúlemsel kuvvetlendirici tasarımında kullanılabilecek di÷er

bir yaklaúım, çıkıú katında puú-pul kaynak izleyici kullanmaktır. ùekil-3.27’de

görülen yapı düúük bir çıkıú direnci elde edilmesini sa÷lamaktadır. Çıkıú katı

T17’den

T22’ye

kadar

numaralanmıú

olan

tranzistorlarla

kurulmuútur.

Tamponlanmamıú iúlemsel kuvvetlendiricinin giriú katı bir geçiú iletkenli÷i

kuvvetlendiricisi,

ikinci

katı

ise

bir

akım

kuvvetlendiricisi

olarak

oluúturulmuútur. Gerilim kazancı, T7, T12, T18 ve T19 tranzistorlarının birleúti÷i

3. 38

dü÷ümdeki

yüksek

direnç

de÷eri

ile

sa÷lanır.

Tamponlanmamıú

kuvvetlendiricinin frekans cevabı oldukça iyidir; çünkü yukarıda sözü edilen

dü÷üm dıúındaki tüm dü÷ümler düúük empedanslıdır. CL yük kapasitesi ek bir

kutup oluúturarak kuvvetlendiricinin kompanze edilmesini sa÷lar. Çıkıú katı,

düúük çıkıú direnci elde etmek üzere kullanılmaktadır. Devrenin küçük iúaret

çıkıú direnci

RO

1

g m21 g m22

(3.39)

úeklindedir. Çıkıú katındaki elemanların boyutlarına ve kutuplama akımına ba÷lı

olarak, çıkıú direnci için 1 kOHM’dan küçük de÷erler elde edilebilir.

+VDD

T8

T9

T5

T6

T17

T13

T14

T18

+VDD

T15

T7

T1

IK

CL

T2

VI

VO

T19

T16

T4

T12

T3

T21

T20

T10

T11

-VSS

ùekil-3.27. Düúük çıkıú dirençli bir CMOS iúlemsel kuvvetlendirici yapısı.

T17 ve T20 tranzistorları, T18 ve T19 tranzistorlarını kutuplarlar ve bunlar

T21 ve T22 tranzistorlarının eúlenik tranzistorlarıdır. ødealde T18 ve T22 ile T19 ve

T21 tranzistorlarının geçit gerilimleri birbirlerini kompanze ederler; dolayısıyla

sıfır giriú gerilimi için çıkıú gerilimi sıfır olur.

3. 39

3.2.5. Düúük gürültülü iúlemsel kuvvetlendiriciler

øúlemsel kuvvetlendiricilerin düúük gürültülü olması, birçok bakımdan

önem taúır. Analog CMOS yapı bloklarının uygulamalarının önemli bir kısmı,

iúaret-gürültü oranının büyük önem taúıdı÷ı haberleúme alanındadır. Gürültü ne

kadar düúük olursa, iúaret gürültü oranı da o kadar iyi olur.

Düúük gürültülü bir iúlemsel kuvvetlendirici elde etmek için

yararlanılabilecek iki yol bulunmaktadır.

Gürültü ile MOS elemanın boyutları ve proses karakteristikleri

arasındaki iliúkileri kullanmak,

Yapıyı kırpıcı ile stabilize etmek.

T7

T10

+VDD

T5

+

+VO

-

+VK

T11

T1

T2

T8

T9

CC

+VK

T6

T3

T4

-VDD

ùekil-3.28. Düúük gürültülü CMOS iúlemsel kuvvetlendirici.

ùekil-3.28. düúük gürültülü bir CMOS iúlemsel kuvvetlendirici yapısını

göstermektedir. kaskod ba÷lı T8 ve T9 tranzistorları, güç kayna÷ından ileri

gelebilecek gürültüyü (PSRR) azaltmak amacıyla kullanılmıúlardır. Giriúte

PMOS tranzistorların kullanılmasının nedeni, bu tranzistorların gürültü

performanslarının NMOS tranzistorlara göre daha iyi olmasıdır. ùekil-3.29 ,

ùekil-3.28’deki devrenin gürültü modelini göstermektedir. yapıdaki do÷ru akım

3. 40

kaynaklarının

üretti÷i

gürültü

ihmal

edilmiútir.

Bunun

nedeni,

MOS

tranzistorların geçitlerinin düúük empedanslı noktalara ba÷lı olmasıdır. T8 ve T9

tranzistorlarının kaynak uçlarından bakıldı÷ında görülen direncin büyük olması

nedeniyle, T8 ve T9’un geçitlerindeki gürültü kaynakları, T1 ve T2’nin

geçitlerindeki gürültü kaynakları yanında ihmal edilebilir. Böylece toplam çıkıú

gürültü gerilimi spektral yo÷unlu÷u

v no 2

>

@

g m6 2 R11 2 v n 6 2 R1 2 ( g m1 2 v n1 2 g m2 2 v n 2 2 g m3 2 v n 3 2 g m4 2 v n 4 2 )

(3.40)

úeklinde ifade edilebilir. Eúde÷er giriú gürültü gerilimi spektral yo÷unlu÷u ise

(3.40) ifadesini iúlemsel kuvvetlendiricinin fark iúaret kazancına bölünmesiyle

elde edilir:

v eq

2

vn6 2

2. v n1

g m1 2 R1 2

2

ª § g ·2 § v ·2 º

«1 ¨ m3 ¸ ¨ n 3 ¸ »

«¬ © g m1 ¹ © v n1 ¹ »¼

(3.41)

+VDD

I1

I2

vn2

vn1

T1

T2

vno

T6

T3

T4

vn3

vn4

vn6

-VSS

ùekil-3.29. Düúük gürültülü iúlemsel kuvvetlendirici yapısının gürültü modeli.

Bu eúitlikten de fark edilebilece÷i gibi, ikinci kattan ileri gelen gürültü, ilk kattan

ileri gelen gürültüye ifadeye katılabilir. Bu nedenle, bu gürültü ihmal

edilebilmektedir. úekil-3.28’deki devrenin gürültüsünü minimize etmek için,

3. 41

(3.41) ba÷ıntısının minimize edilmesi gerekti÷i açıktır. gm1>>gm3 úartının

sa÷lanmasıyla (3.41) ba÷ıntısı minimize edilebilir. Bu durumda, giriú

gürültüsünün baskın bileúeni giriú tranzistorları tarafından üretilen gürültü olur.

Daha

önce

de

belirtildi÷i

gibi,

giriúte

PMOS

tranzistorların

kullanılmasının nedeni, PMOS tranzistorların gürültü performanslarının daha iyi

olmasıdır. Gürültünün sıcaklı÷a ba÷lı bileúeninin azaltılması için, giriú

tranzistorunun geçiú iletkenli÷i arttırılabilir. Bunu sa÷lamak üzere de

tranzistorların savak akımları ve/veya W/L oranları arttırılabilir. Devrenin

giriúindeki elemanların üretti÷i 1/f yürültü bileúeninin azaltılması için de W veya

L de÷erleri arttırılabilir.

BJT’ler için köúe frekansı (1/f gürültüsü ile sıcaklı÷a ba÷lı gürültü daha

düúüktür. Dolayısıyla, düúük frekanslarda (1 kHz’den daha küçük frekasnlarda)

gürültüye önem veriliyorsa, MOS tranzistor yerine bipolar tranzistor

kullanılması ye÷lenebilir.

KAYNAKLAR

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

H. Kuntman, Analog tümdevre tasarımı, Sistem yayınları, østanbul, 1992.

H. Kuntman, Analog MOS tümdevre tasarımı (Endüstri Semineri Notu), øTÜ øleri

Elektronik Teknolojileri Araútırma Geliútirme Vakfı (ETA), Uygulamaya özgü

tümdevre teknolojileri yaz okulu notları, østanbul,1993.

H. Kuntman, øleri analog tümdevre tasarımı: Analog devreler, (Endüstri Semineri

Notu), øTÜ øleri Elektronik Teknolojileri Araútırma Geliútirme Vakfı (ETA),

østanbul,1994.

P.R. Gray, R.G. Meyer, Analysis and design of analog integrated circuits, John

Wiley, 1984.

R. Gregorian, G.C. Temes, Analog MOS integrated circuits for signal processing,

John Wiley, 1986.

A.B. Grebene, Bipolar and MOS analog integrated circuit design, John Wiley, 1984.

F. Riedel, MOS Analogtechnik, Oldenburg Verlag, Wien, 1988.

P.E. Allen and D.R. Holberg, CMOS analog circuit design, Holt, Rinehart and

Winston Inc., New York, 1987.