FIRAT ÜNİVERSİTESİ MÜHENDİSLİK FAKÜLTESİ

ELEKTRİK-ELEKTRONİK MÜHENDİSLİĞİ BÖLÜMÜ

MANTIK DEVRELERİ LABORATUVARI

DENEY NO:1

TEMEL KAPI DEVRELERİ

Deneyin Amacı

Mantık devrelerinin tasarımında kullanılan temel kapıların yapısı ve karakteristikleri hakkında bilgi

vermek. Tasarım sırasında dikkat edilmesi gereken hususlara dikkat çekmek.

Deneye Gelmeden Önce Yapılası Gereken Hazırlıklar

Transistör, diyot gibi temel analog elektronik devre elemanlarının çalışmasını, temel

özelliklerini araştırıp geliniz.

Transistörlerin çalışma bölgelerini araştırınız.

MOS ve CMOS kavramlarını araştırarak çalışma şekillerini inceleyeniz.

Deneyde kullanılacak olan kapıların bağlantılarını ve temel özelliklerini araştırınız.

Sadece diyot ile gerçekleştirilen kapı yapılarının avantaj ve dezavantajlarını araştırınız.

Sayısal devre tasarımında kullanılabilirliğini tartışınız.

TTL yapıların özelliklerini inceleyiniz.

RTL yapıların özelliklerini inceleyiniz. Sayısal devre tasarımında kullanılabilirliğini tartışınız.

RTL yapılar ile gerçekleştirilen AND, OR ve NOT yapılarını inceleyiniz

RTL yapılar ile gerçekleştirilen NAND ve NOR yapılarını inceleyiniz. Bir önceki araştırma

konu ile elde ettiğiniz bulguları karşılaştırınız.

Pozitif lojik, negatif lojik kavramlarını araştırınız.

1. VEYA (OR) Kapısı

1.1. Diyot ile Gerçekleştirilen VEYA Kapı Devresi Gerçeklemesi

Şekil 1.1’deki devrede her iki girişe de Lojik-0 uygulandığında D1 ve D2 diyotlarının her ikisi de

tıkama yönünde kutuplanmıştır. Çünkü bir diyodun iletime geçebilmesi için anod geriliminin katod

geriliminden daha pozitif olması gerekmektedir.

Diyotların her ikisi de tıkama yönünde

kutuplandığından F çıkışı toprak seviyesinde olup lojik 0 değerine sahiptir. Girişlerden en az bir tanesi

Lojik-1 seviyesine çekildiğinde ilgili diyot ileri yönde kutuplandırıldığından iletime geçecek ve çıkış

yaklaşık Lojik-1 seviyesinde olacaktır.

D1

A

F

D2

R1

B

270

LED1

Şekil 1.1. Diyot ile VEYA kapı devresi.

1.2.Direnç-Transistör ile VEYA Kapı Devresi Gerçeklemesi

Şekil 1.2’deki devrede girişlerden her ikisi de Lojik-0 seviyesinde olduğunda Q1 ve Q2 transistörleri

kesim durumunda olup devre çıkışı Lojik-0 seviyesindedir. Girişlerden en az birinin Lojik-1

seviyesine çekilmesi ile ilgili transistör iletime geçeceğinden devre çıkışı yaklaşık Lojik-1 seviyesinde

olacaktır.

+5V

Q1

A

R1

33k

Q2

R2

B

33k

F

LED1

R3

270

Şekil 1.2. Drenç-Transistör ile VEYA kapı devresi.

2. VE (AND) Kapısı

2.1.Diyot ile VE Kapı Devresi Gerçeklemesi

Şekil 1.3’deki devrede her iki girişte Lojik-0 seviyesinde olduğunda D1 ve D2 diyotlarının her ikisi de

ileri yönde kutuplanacağından dolayı çıkışta sadece 0.7 V görülecektir. (Neden 0.7 V?) Bu potansiyel

farkta Lojik-0 olarak değerlendirilecektir. Girişlerden bir tanesi Lojik-0, diğeri Lojik-1 seviyesine

çekildiğinde de durum değişmeyecektir. Çünkü bu durumda diyotlardan biri iletim, diğeri ise

kesimdedir. Bu devrede her iki giriş de Lojik-1 seviyesine çekildiğinde, diyotlar ters kutuplanmış

olacak ve besleme gerilimi doğrudan çıkışta görülecektir. Bu değer de Lojik-1 olarak

değerlendirilecektir.

+5V

R1

D1

270

A

F

D2

B

LED1

Şekil 1.3. Diyot ile VE kapı devresi.

2.2.Direnç-Transistör ile VE Kapı Devresi Gerçeklemesi

Şekil 1.4.’deki devrede girişlerden her ikisi de Lojik-0 seviyesinde olduğunda Q1 ve Q2 transistörleri

kesim durumunda olacaktır. Bunun sonucunda A noktasında besleme gerilimi görülecek ve bu gerilim

de çıkıştaki transistörü iletime geçirecektir. Sonuç olarak çıkışta Lojik-0 seviyesinde bir gerilim

görülecektir. Girişlerden her ikisi de Lojik-1 seviyesinde olduğunda Q1 ve Q2 transistörlerinin her ikisi

de iletim durumunda olup çıkıştaki transistörün bazında iletime geçirebilecek bir gerilim mevcut

olmadığından kesim durumunda olacak ve burada Lojik-1 seviyesinde bir gerilim görülecektir.

+5V

R4

1.0k

R3

R5

270

56k

A

F

R1

LED1

33k

B

R2

33k

Şekil 1.4. Direnç-Transistör ile VE kapı devresi.

3.DEĞİL (NOT) Kapısı

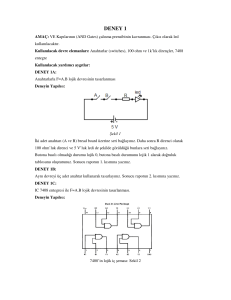

Girişine uygulanan Lojik-0 seviyesindeki işareti çıkışa Lojik-1 seviyesi, Lojik-1 seviyesindeki işareti

ise Lojik-0 seviyesi olarak aktaran devrelere DEĞİL (Evirici, Tersleyen) kapısı denir. Şekil 1.5’de

DEĞİL kapısının transistör ile gerçekleştirilmiş eşdeğer devresi görülmektedir. Bu devrede girişe

Lojik-0 seviyesinde bir işaret uygulandığında transistör kesimde ve çıkışta besleme gerilimi

görülmektedir. Bu ise Lojik-1 seviyesi olarak değerlendirilmektedir. Girişe Lojik-1 seviyesinde bir

işaret uygulandığında ise transistör iletime geçecek ve çıkışta Lojik-0 seviyesinde bir gerilim

görülecektir.

+5V

R2

270

F

A

R1

LED1

33k

Şekil 1.5. Transistörlü DEĞİL kapı devresi

Uygulama-1: Temel Kapıların Tanım İfadelerinin Elde Edilmesi

Gerekli Malzeme Listesi:

1 Adet 74HCT32 (OR)

1 Adet 74HCT00 (NAND)

1 Adet 74HC02 (NOR)

1 Adet 74LS08 (AND)

1 Adet 74HC04 (NOT)

3 Adet LED

3 Adet 150 direnç

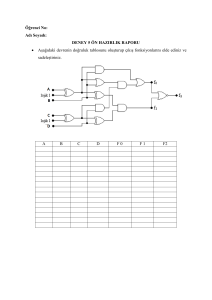

74HCT32 entegresini kullanarak aşağıdaki şekildeki uygulama devresini kurunuz. Kapı girişlerine

anahtarlar yardımıyla aşağıdaki tablolarda gösterildiği gibi değişik kombinasyonlar oluşturunuz ve

çıkışa bağlı olan LED’in durumunu gözlemleyerek tabloları doldurunuz.

Deneyi 74HCT00, 74HC02 ve 74LS08 entegreleri için de tekrarlayınız.

Entegre

Giriş 1

0

0

1

1

74HC32

Giriş 2

Çıkış

0

1

0

1

Entegre

Giriş 1

0

0

1

1

74HCT00

Giriş 2

Çıkış

0

1

0

1

Entegre

Giriş 1

0

0

1

1

74HC02

Giriş 2

Çıkış

0

1

0

1

Entegre

Giriş 1

0

0

1

1

74LS08

Giriş 2

Çıkış

0

1

0

1

74HC04 entegresini kullanarak şekildeki devreyi kurunuz. Kapı girişine anahtar yardımıyla değişik

değerler vererek çıkıştaki LED’in durumunu gözlemleyiniz. Doğruluk tablosunu doldurunuz.

Entegre

Giriş

0

1

74HC04

Çıkış

3. CMOS ve TTL Yapılar

CMOS ile TTL yapılar, “entegre” olarak adlandırılan yapılarda sıkça kullanılan sayısal devre

gerçekleme teknolojilerindendir. Entegreler, belirli bir amaca yönelik olarak çok sayıda direnç, diyot

ve transistörlerin bir araya getirilmesiyle oluşturulan tümleşik devre yapılarıdır. Entegreler,

tümleşiklik seviyelerine ve yapılarında kullanılan transistörlerin tipine göre sınıflandırılabilirler. Lojik

uygulamada seçilecek entegre devre ailesi, devrenin özelliklerine göre belirlenir. Günümüzde çok özel

devreler hariç genellikle devre gerçekleştirmede TTL ve CMOS yapılı entegre devreleri

kullanılmaktadır.

Tümleşiklik seviyelerine göre entegreler beş ana başlık altında incelenebilir:

• Küçük Ölçekte Tümleşiklik (SSI): 12’den az transistör içeren entegreler

• Orta Ölçekte Tümleşiklik (MSI): 12 ile 99 arası transistör içeren entegreler. (örneğin flip-floplar,

sayıcılar)

• Büyük Ölçekte Tümleşiklik (LSI): 100 ile 9.999 arası transistör içeren entegreler (örneğin hafıza

elemanları EPROM, ROM)

• Çok Büyük Ölçekte Tümleşiklik (VLSI): 10.000-99.999 arası transistör içeren entegreler (örneğin 8bit basit mikroişlemciler)

•Ultra Büyük Ölçekte Tümleşiklik (ULSI): 100.000- ve fazlası transistör içeren entegreler (örneğin

gelişmiş entegreler)

Yapılarında kullanılan transistör tiplerine göre:

TTL (Transistor-Transistor Logic) Entegreler: Yapılarında bipolar transistörler kullanılır. Besleme

gerilimleri 5V’tur. CMOS entegrelere göre güç kayıpları çok fazladır.

•Standard TTL (74XXX ailesi): En eski, yavaş ve güç kayıpları çok fazladır.

•Low Power TTL (74LXXX ailesi): Daha düşük güç kayıpları vardır

•Schottky TTL (74SXXX ailesi): Hızlı fakat güç kayıpları fazladır.

•Low Power Schottky TTL (74LSXXX ailesi): hızlı ve düşük güç kayıplarına sahip

•Advanced LS TTL (74ALSXXX): Hız-güç kayıpları oranı çok iyi

•FAST TTL (74FXXX): Hız ve güç kayıpları açısından en iyi TTL entegresi

CMOS (Complementary Metal-Oxide Silicon) Entegreler:

Yapıları FET türü transistörlerden oluşur. Besleme gerilimleri 3V ile 15V arasında olabilir. TTL’den

çok daha az güç kayıpları vardır. (Neden?)

•40XX ailesi: En eski CMOS, yavaş, güç kaybı çok az.

•74HCTXXX ailesi: TTL uyumlu (besleme gerilimi 5V), CMOS’un avantajları (çok düşük güç

kayıpları) ile TTL’in avantajlarını (çok hızlı) bir arada bulundurur. En popüler entegredir.

CMOS lojik ailesi, mantık fonksiyonlarını oluşturacak şekilde birbirine bağlı her iki tip (hem n-kanallı

hem p-kanallı) MOS elemanlarından oluşmaktadır. Temel devre aşağıdaki şekillerde gösterildiği gibi,

p-kanallı bir MOS ve n-kanallı ikinci bir MOS’tan oluşan bir tersleyicidir.

p-kanallı elemanın kaynak ucu VCC düzeyinde, n-kanallı elemanın kaynak ucu da toprak düzeyindedir.

VCC değeri +3V ila +18V arasında herhangi bir değerde olabilir. Gerilim seviyeleri; alçak seviye için

0V, yüksek seviye için de VCC’dir.

Şekil 1.6. CMOS devresi.

CMOS’un çalışması şöyle özetlenebilir.

1. n-kanallı MOS, kapıdan-kaynağa gerilimi pozitif olduğu zaman iletir.

2. p-kanallı MOS, kapıdan-kaynağa gerilimi negatif olduğu zaman iletir.

3. Kapıdan-kaynağa gerilimin sıfır olması durumunda her iki tip elemanda kapanır.

3.1 TTL ve CMOS KAPI KARAKTERİSTİKLERİ

Sayısal tümdevrelerin temel karakteristikleri, tümdevrelere ait olan giriş/çıkış-düşük/yüksek seviye

gerilim ve akım değerlerinin yanı sıra gürültü marjları, yayılma gecikme süreleri, güç tüketimleri, giriş

ve çıkış yelpaze sayısı olarak bilinir.

Gürültü marjı (NM), gürültünün kapı tarafından tolere edilebileceği en büyük genlik değeridir. Lojik

kapılarda gürültü, kapının girişindeki istenmeyen akım ve gerilim değişiklikleri olarak tanımlanır.

Gürültünün değeri çok büyük olursa, istenmeyen çıkışlara neden olabilir. Bununla beraber, sayısal

sistem girişindeki gürültü gerilim seviyesi, gürültü marjından düşük seviyede ise bu gürültü, analog

sistemlerde olduğu gibi birikerek çıkışa aktarılmaz. Şekil “1.7’de gürültü marjının grafiksel gösterimi

verilmiştir.

Şekil 1.7. Gürültü marjının grafiksel gösterimi.

VIL : Kapının düşük (LOW) olarak algılayabileceği en yüksek giriş gerilim seviyesi,

VIH : Kapının yüksek (HIGH) olarak algılayabileceği en düşük giriş gerilim seviyesi,

VOL : Kapının düşük (LOW) olarak verebileceği en büyük gerilim seviyesi,

VOH : Kapının yüksek (HIGH) olarak verebileceği en düşük gerilim seviyesi olarak tanımlanır.

Gürültü marjı, yüksek seviye için, NMH = VOH – VIH, düşük seviye için, NML = VIL – VOL, olarak

tanımlanır. Bir lojik kapının istenen çıkışı vermesi için kapının girişindeki gürültü geriliminin değeri,

Şekil 1.7’de gösterilen gri renkli bölgelerdeki gürültü marj değerlerine eşit veya küçük olmalıdır.

Siyah renkli bölge ise kapı çıkışının kararsız hale geldiği giriş gerilimi değer aralığını göstermektedir.

Gürültünün genliği, bu gürültü marjları dışına çıktığında kapı, istenmeyen çıkışlar verebilir veya

kararsız hale gelebilir. Sayısal devrelerde kapılar, birbirine kaskad olarak bağlandığı için düşük

seviyeli giriş gerilimi, VOL değerinden daha yüksek ve yüksek seviyeli giriş gerilimi, V OH değerinden

daha düşük olamaz.

Ayrıca, kapının normal şartlar altında yani girişleri besleme ya da toprak gerilimleri ile sürüldüğünde

çıkışının Lojik-1 olması sağlandığında, çıkışının gerilim seviyesi VH, Lojik-0 olması sağlandığında

çıkışının gerilim seviyesi VL olarak adlandırılır. VH, VOH’den daha yüksek, VL’de VOL’den daha düşük

seviyededir. Bir kapı çıkışı zorladıkça gerilim seviyeleri V H ve VL’den marj değerler olan VOH ve

VOL’ye doğru kayar. Kapı girişlerini süren bir önceki kapının zorlanması, aktarılan işaret üzerinde

gürültü bulunması ya da işaretin zayıflaması durumunda, kapı girişlerinde V H ve VL’den farklı gerilim

seviyeleri gözlenebilir. Önceki paragrafta da belirtildiği gibi, kapının işlevini yerine getirebilmesi için

girişindeki gerilim değerleri lojik 1 ise Vbesleme ile VIH aralığında, Lojik-0 ise VIL ile Vtoprak aralığında

kalmalıdır.

Yayılma gecikme süresi, tP, bir elemanın girişindeki seviye değişimi ile elemanın çıkışında oluşacak

seviye değişimi (yüksek seviyeden alçak seviyeye, H-L, alçak seviyeden yüksek seviyeye, L-H) için

geçen süredir. tPHL, giriş geriliminin VIH’ye veya VIL’ye göre %50 değiştiği andan itibaren çıkış

geriliminin VOH’den VOL’ye %50 değişene kadar geçen süredir. tPLH de benzer şekilde çıkışın VOL’den

VOH’ye geçişi için tanımlanır. tPLH ve tPHL genellikle birbirine eşit değildir ve kapının ortalama

gecikme süresi;

𝑡𝑃𝐿𝐻 + 𝑡𝑃𝐻𝐿

𝜏𝑜𝑟𝑡 =

2

şeklinde belirlenir. Yayılma gecikme süresi, kapının çalışabileceği en büyük frekans değeri ile

doğrudan ilgilidir. Genellikle sayısal devrenin çalışma frekansı, toplam en kötü gecikme süresi ile

belirlenir. Yükselme süresi (tr); giriş geriliminin VIL değerinin %10 fazlasından, VIL’nin %90 fazlasına

kadar artımı sırasında geçen süredir. Düşme süresi (tf) ise VIH değerinin %10 eksiğinden, VIH’nin %90

eksiğine kadar azalması sırasında geçen süre olarak tanımlanır. Yayılma gecikme, yükselme ve düşme

sürelerinin genlik-zaman diyagramı, Şekil 1.8’de verilmiştir.

Şekil 1.8. Yayılma gecikme süreleri, yükselme ve düşme süreleri.

Güç tüketimi, kapı elemanın çalışması sırasında harcadığı güç olarak tanımlanır ve P dis = VCC . ICC

ifadesiyle hesaplanır. ICC değeri, düşük ve yüksek seviyelerde harcanan akımların aynı olmamasından

dolayı bu iki değerin ortalaması, ICC = (ICCH + ICCL)/2, olarak ifade edilir. Tüm elektronik elemanlarda

olduğu gibi lojik kapılarda da bir miktar enerji ısıya dönüşür. Bu ısı, tümdevrede fiziksel hataların

oluşmasına ve tümdevrenin yıpranmasına neden olur. Bu yüzden tümdevre tasarımlarında, genellikle

güç tüketimi daha az olan ve aynı zamanda geniş ölçekli tasarımları destekleyen CMOS teknolojisi

kullanılır.

Bir kapının giriş yelpazesi, kapının destekleyebileceği giriş sayısı olarak tanımlanır. Kullanılan

tümdevrede her bir kapı için kaç giriş mevcutsa, giriş yelpazesi odur. Çıkış yelpazesi ise, kapının

normal çalışma sınırları dışına çıkmadan bu kapının çıkışına bağlanabilecek maksimum kapı sayısıdır.

Düşük seviye (lojik 0) çıkışa sahip bir kapının çıkış yelpazesi, yüksek seviye (Lojik-1) çıkışa sahip

aynı kapının çıkış yelpazesine, her bir seviyedeki maksimum çıkış akım değerleri ve giriş akım

değerleri farklı olduğu için eşit değildir. Buna göre her bir seviyedeki çıkış yelpaze sayısı,

Lojik 1 çıkışına sahip kapının çıkış yelpazesi: IOH(max)/IIH(max),

Lojik 0 çıkışına sahip kapının çıkış yelpazesi: IOL(max)/IIL(max) olarak ve

kapının çıkış yelpazesi min(IOH(max)/IIH(max), IOL(max)/IIL(max)) olarak

belirlenir.

Yayılma gecikme süresi, lojik kapının girişinde meydana gelen bir değişimin çıkışına etki etmesi için

gereken süre olarak tanımlanır. Örnek olarak bir NOT kapısı ele alındığında, bu kapının, girişindeki

lojik 1 değerini, çıkışta lojik 0 değerine dönüştürmesi için geçen süreye, yayılma gecikme süresi denir.

Çıkış yelpazesi (fan-out): lojik kapının çıkışına, belirlenen aralıklarda bulunan lojik işaretin gerilim

seviyeleri korunacak şekilde bağlanabilecek olan kapı sayısıdır.

Lojik kapıların çıkış karakteristikleri, üç gruba ayrılabilir:

Bipolar çıkışlar (TP: Totem Pole) : Lojik 0 ve lojik 1 değerlerini üreten TTL çıkışlardır.

Unipolar çıkışlar (OC: Open Collector) : Sadece lojik 0 değerini üretebilir, lojik 1 seviyesinde

transistör doyuma ulaşır ve gerekli olan gerilim seviyesi, besleme gerilimine direnç bağlanarak elde

edilir. Bu çıkışlar, birden fazla lojik çıkışın ortak bir yola bağlanması gerektiğinde kullanılır.

Üç-durumlu çıkışlar (TS: Tri State) : Bu kapılar lojik 0 ve lojik 1 durumlarına ek olarak kapıların veri

yollarına bağlanmalarını mümkün kılan, yüksek empedans olarak adlandırılan üçüncü bir duruma

sahiptir.

Sayısal tümdevreler, üretilirken uygulanan teknolojilere göre şu şekilde sınıflandırılırlar:

ECL : Emitör-kuplajlı lojik

TTL : Transistor-transistor lojik

I 2 L : Entegre enjeksiyonlu lojik

MOS : Metal-oksit yarı iletken

CMOS : Tümlemeli metal-oksit yarı iletken

TTL, geniş çaplı bir sayısal fonksiyonlar listesine sahiptir ve halen en popüler lojik ailesidir.

ECL, yüksek hızlı işlemler, MOS ve I 2 L , yüksek bileşen yoğunluğu, CMOS ise düşük güç tüketimi

gerektiren sistemlerde kullanılmaktadır.

TTL ve CMOS lojik ailesine mensup tümdevrelerin kendilerine has özellikleri şu şekilde verilebilir:

TTL-teknolojisi (74xx) : Lojik devrelerde en sık kullanılan teknolojidir ve iki temel öğe ile tanımlanır.

Kapı başına gecikme süresi yaklaşık olarak 20ns ve güç tüketimi 15mA/lojik kapı.

TTL-teknolojisi (54xx) : Temel olarak TTL tümdevreler ile aynı özelliklere sahip olmasının yanında

askeri amaçlı uygulamalar için üretildiklerinden bu uygulamalara ait özellikleri taşır.

TTL-L (74Lxx) : TTL tümdevrelerden daha az güç harcarken, daha düşük hızlara sahiptir.

TTL-LS (Low Schottky: 74LSxx) : TTL tümdevrelerden daha az güç tüketirken TTL tümdevreler ile

aynı işlem süresine sahiptir.

TTL-ALS (Advanced LS: 74ALSxx) : TTL LS tümdevrelerden daha yüksek hıza ve çıkış akımına

sahiptir.

TTL-F (Fast I/O: 74F) : TTL tümdevrelerden daha yüksek hıza sahiptir ve bunun için çok fazla güç

harcar.

TTL-OC : TTL tümdevreler ile benzer özelliklere sahiptir fakat TTL tümdevreler ile

karşılaştırıldığında daha fazla yayılma gecikme süresine sahiptir.

CMOS-teknolojisi (4xxx) : Düşük güç tüketimine sahiptir.

CMOS-AC (74ACxx) : CMOS tümdevrelerden daha yüksek hıza sahip ve TTL uyumludur. CMOSHC (74HCxx) : CMOS tümdevrelerden daha yüksek hızlara sahiptir.

CMOS-H (High Speed CMOS: 74HCTxx) : CMOS tümdevrelerden daha düşük güç tüketimi

sağlarken sayısal tümdevrelerde daha yüksek frekanslarda çalışma olanağı sağlar.

Tablo 1.1’de bazı lojik ailelerin birbirleriyle çıkış yelpaze sayısı, güç tüketimi, gürültü marjı, yayılma

gecikme süresi ve çalışma frekansı açılarından karşılaştırması verilmiştir.

Tablo 1.1. Bazı lojik ailelerinin birbirleriyle karşılaştırılması (VG: Çok iyi, G: İyi, P: Zayıf)

Aile

TTL

TTL-H

TTL-L

TTL-LS

TTL-S

TTL-AS

TTL-ALS

ECL 10K

ECL100K

MOS

74C

74HC

74HCT

74AC

74ACT

Lojik Kapı

NAND

NAND

NAND

NAND

NAND

NAND

NAND

OR-NOR

OR-NOR

NAND

NOR/NAND

NOR/NAND

NOR/NAND

NOR/NAND

NOR/NAND

Çıkış Güç Tüketimi Gürültü

Yelpazesi (mW/kapı)

Marjı

10

10

VG

10

22

VG

20

1

VG

20

2

VG

10

19

VG

40

10

VG

20

1

VG

25

40-55

P

25

40-55

P

20

0.2-10

G

50

0.01/1

VG

20

0.0025/0.6

VG

20

0.0025/0.6

VG

50

0.005/0.75

VG

50

0.005/0.75

VG

Yayılma

Gecikmesi

(ns/kapı)

10

6

33

9,5

3

1,5

4

2

0.75

300

70

18

18

5,25

4,75

Çalışma

Frekansı(MHz)

35

50

3

45

125

175

50

>60

600

2

10

60

60

100

100

Uygulama-2: TTL NOR Kapısının Statik (Boşta Çalışma) Karakteristiğinin Bulunması

Gerekli Malzeme Listesi:

1 Adet 74HC02

Güç kaynağı

Osiloskop

Fonksiyon jeneratörü

Boşta çalışma karakteristiği, kapı çıkışı yüksüz iken V o=f(Vi) bağıntısıdır. Aşağıdaki uygulama

devresinde verilen düzeneği kurarak boşta çalışma karakteristiğini, uygun değerler alarak bir tablo

halinde elde ediniz. Fonksiyon jeneratörünü 20Hz 0-5 V arasında değişen bir üçgen dalga şeklinde

ayarlayınız.

Boşta çalışma karakteristiğinin çıkartılması için kurulacak devre

Vgiriş

Vçıkış

Uygulama-3: CMOS NOR Kapısının Statik (Boşta Çalışma) Karakteristiğinin Bulunması

Gerekli Malzeme Listesi:

1 Adet CD4001

Güç kaynağı

Osiloskop

Fonksiyon jeneratörü

Aşağıdaki uygulama devresinde verilen düzeneği kurarak boşta çalışma karakteristiğini, uygun

değerler alarak bir tablo halinde elde ediniz.

Boşta çalışma karakteristiğinin çıkartılması için kurulacak devre

Vgiriş

Vçıkış

Uygulama-4: TTL Kapılarının Dinamik Karakteristiğinin Bulunması

Gerekli Malzeme Listesi:

1 Adet 74HC02

Osiloskop

Bir lojik kapının gecikmesinin daha önce gösterildiği gibi, tPLH ve tPHL olmak üzere iki bileşeni vardır.

Bir kapının toplam gecikmesi, tek sayıda NOR kapısının oluşturduğu osilatör devresinin (ring

osilatörü) ürettiği işaretin periyodunun ölçülmesiyle bulunabilir. Deneyde ise yine tek sayıda NOR

kapısının aşağıdaki gibi gecikme zinciri oluşturacak şekilde bağlanması ile gecikme süreleri tespit

edilecektir. Devreyi deney setine kurarak hem darbe üreteci çıkışını hem de gecikme zincirinin çıkışını

osiloskopla izleyiniz ve darbe üreteci çıkışının yükselen ve düşen kenarlarda ne kadar geciktiğini

tespit ediniz. Buradan bir NOR kapısı için olan tPLH ve tPHL değerlerini belirleyiniz.

Setin üzerindeki dahili fonksiyon jeneratörünü kullanınız ve fonksiyon jeneratörünü yaklaşık

10kHz’lik bir frekans değerine ayarlayınız.

Gecikme zinciri.

Gecikmenin gözlenemeyecek kadar küçük olması halinde kurduğunuz devreyi ring osilatör yapısına

dönüştürüp osilasyon periyodundan, bir NOR kapısı için ortalama gecikme süresini belirleyiniz.

tPLH

tPHL

Uygulama-5: CMOS Kapıların Dinamik Karakteristiklerinin Bulunması

1 Adet CD4001

Osiloskop

TTL NOR kapısı için daha önce yapılanları, CMOS NOR kapısı için tekrar ediniz.

Gecikme zinciri.

tPLH

tPHL

Uygulama-6: TTL Kapıları Üzerinde Harcanan Gücün Ölçümü

Gerekli Malzeme Listesi:

1 Adet 74HC02

1 Adet sinyal Generatörü

Ampermetre

Aşağıdaki devrenin girişine tepeden tepeye 5V’luk kare dalga uygulayınız. Giriş işaretinin frekansını 0

Hz’den 5MHz’e kadar değiştirerek çeşitli frekanslar için beslemeden çekilen akımı ölçünüz.

𝑃𝑑 = 𝑉𝐶𝐶 𝐼𝐶𝐶

Bağıntısından kapı üzerinde harcanan gücün frekansla değişimini tablo halinde veriniz.

TTL kapıları üzerinde harcanan gücün bulunması için kurulacak devre

Frekans

Icc

Pd

Uygulama-7: CMOS Kapıları Üzerindeki Harcanan Gücün Ölçümü

Gerekli Malzeme Listesi:

1 Adet CD4001

1 Adet sinyal Generatörü

Ampermetre

Bir önceki deneyde TTL NOR kapısı için yapılanları, CMOS NOR kapısı için tekrar ediniz.

MOS kapıları üzerinde harcanan gücün bulunması için kurulacak devre

Frekans

Icc

Pd