LOJİK DEVRE LABORATUARI DENEY 1 TEMEL KAPI DEVRELERİ DENEYİ

ÖN

ÇALIŞMA RAPORU

AMAÇ:

*Temel kapı devrelerinin işlemlerinin incelenmesi

*Temel kapı devrelerinin işlemlerini gerçekleştiren kapı devrelerinin incelenmesi ve bu

devrelerin uygulanması

GİRİŞ:

Dijital elektronik sistemler temel mantık kurallarına göre çalışırılar. Bu tür sistemlerde

gerek giriş, gerek çıkış iki farklı duruma sahip olabilir. Yani bütün mantık devrelerinde ikili

sayı sistemi kullanılır.

Temel olarak üç lojik temel kapı devresi mevcuttur. Deneyimizde temel lojik kapı

devreleri diyot ve transistorlerle kurulan çeşitli devreler kuracağız.

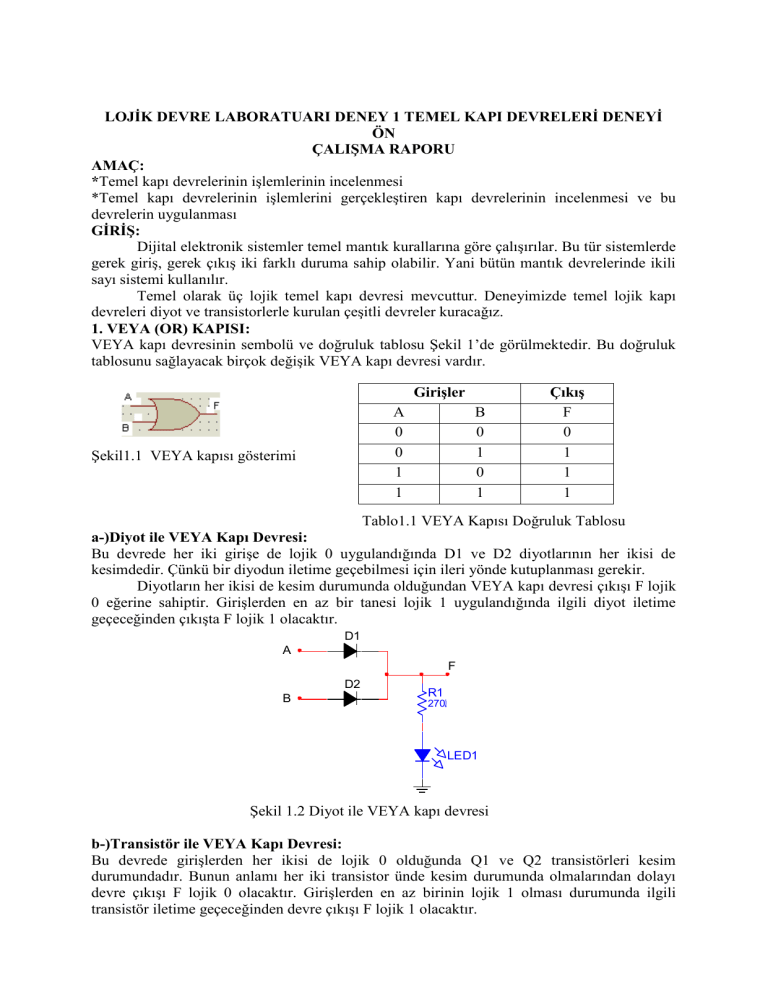

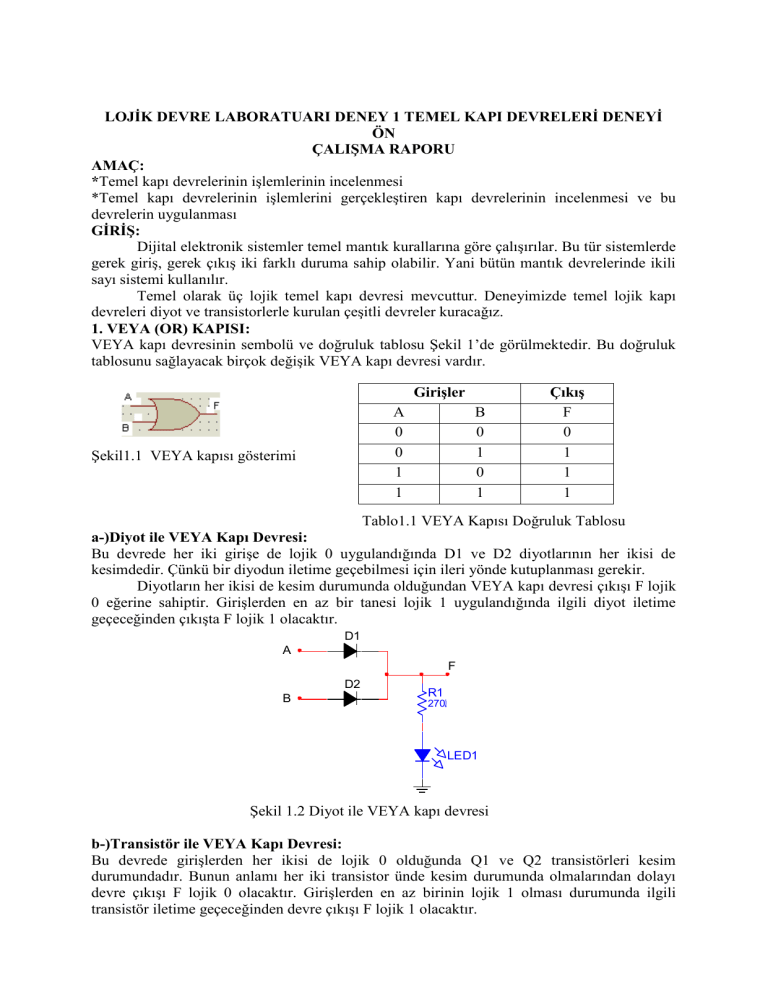

1. VEYA (OR) KAPISI:

VEYA kapı devresinin sembolü ve doğruluk tablosu Şekil 1’de görülmektedir. Bu doğruluk

tablosunu sağlayacak birçok değişik VEYA kapı devresi vardır.

Girişler

A

0

0

1

1

Şekil1.1 VEYA kapısı gösterimi

B

0

1

0

1

Çıkış

F

0

1

1

1

Tablo1.1 VEYA Kapısı Doğruluk Tablosu

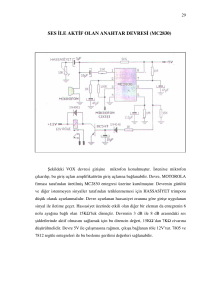

a-)Diyot ile VEYA Kapı Devresi:

Bu devrede her iki girişe de lojik 0 uygulandığında D1 ve D2 diyotlarının her ikisi de

kesimdedir. Çünkü bir diyodun iletime geçebilmesi için ileri yönde kutuplanması gerekir.

Diyotların her ikisi de kesim durumunda olduğundan VEYA kapı devresi çıkışı F lojik

0 eğerine sahiptir. Girişlerden en az bir tanesi lojik 1 uygulandığında ilgili diyot iletime

geçeceğinden çıkışta F lojik 1 olacaktır.

D1

A

F

D2

B

R1

270

LED1

Şekil 1.2 Diyot ile VEYA kapı devresi

b-)Transistör ile VEYA Kapı Devresi:

Bu devrede girişlerden her ikisi de lojik 0 olduğunda Q1 ve Q2 transistörleri kesim

durumundadır. Bunun anlamı her iki transistor ünde kesim durumunda olmalarından dolayı

devre çıkışı F lojik 0 olacaktır. Girişlerden en az birinin lojik 1 olması durumunda ilgili

transistör iletime geçeceğinden devre çıkışı F lojik 1 olacaktır.

+5V

Q1

A

R1

33k

Q2

R2

B

33k

F

LED1

R3

270

Şekil1.3 Transistörlü VEYA Kapı Devresi

2. VE (AND) KAPISI:

Girişler

A

0

0

1

1

Şekil 1.4 VE kapısı gösterimi

B

0

1

0

1

Çıkış

F

0

0

0

1

Tablo1.2 VE Kapısı Doğruluk Tablosu

a-)Diyot ile VE Kapı Devresi:

Bu devrede her iki girişte lojik 0 olduğunda D1 ve D2 diyotlarının her ikisi de ileri yönde

kutuplanacağından dolayı F çıkışında sadece 0.6 V görülecektir. Bu potansiyel farkta lojik 0

olarak değerlendirilecektir. Girişlerden bir tanesi lojik 0 , diğeri lojik 1 olduğunda da durum

değişmeyecektir. Çünkü bu durumda diyotlardan biri iletim, diğeri ise kesimdedir. Bu devrede

her iki giriş lojik 1 olduğunda, diyotlar ters kutuplanmış olacak ve besleme voltajı direkt F

çıkışında görülecektir. Bu çıkış ta lojik 1 olarak değerlendirilecektir.

+5V

D1

R1

270

A

D2

F

B

LED1

Şekil1.5 Diyot ile VE Kapı Devresi

b-)Transistör ile VE Kapı Devresi:

Bu devrede girişlerden her ikiside lojik 0 olduğunda Q1 ve Q2 transistörleri kesim durumunda

olacaktır. Bunun sonucunda A noktasında Vcc gerilimi görülecek ve bu gerilim ise çkıştaki

transistor ü iletime geçecektir. Sonuç olarak çıkıştaki F lojik 0 olacaktır. Girişlerden her ikisi

de lojik 1 olduğunda Q1 ve Q2 transistörlerinin her ikisi de iletim durumundadır ve a nktası

şaseye seri bağlanmış olacaktır. Bu durumda ise çıkıştaki transisistör kesim durumuna

geçecek ve çıkıştaki F lojik 1 olacaktır.

+5V

R4

R5

1.0k

270

R3

F

56k

R1

A

LED1

33k

R2

B

33k

Şekil1.6 Transistör ile VE Kapı Devresi

3.DEĞİL (NOT) KAPISI:

Şekil1.7 DEĞİL Kapı gösteimi

GİRİŞ

ÇIKIŞ

0

1

1

0

Tablo1.3 DEĞİL Kapısı Doğruluk Tablosu

Girişine uygulanan lojik 0 işaretini çıkışa lojik 1, lojik 1 işaretini ise ljik 0 olarak çıkışa

aktaran devrelere DEĞİL kapısı denir.Şekil1.8’de DEĞİL kapısının transistor ile

gerçekleştirilmiş devresi görülmektedir. Bu devrede girişe lojik 0 uygulandığında transistor

kesimde ve F çıkışında Vcc görülmektedir. Bu ise lojik 1 olarak değerlendirilmektedir. Girişe

lojik 1 verildiğinde ise transistor iletime geçerek F çıkış noktası şaseye bağlanmş olup ve F

çıkışında lojik 0 olarak görülmektedir.

+5V

R2

270

F

A

R1

LED1

33k

Şekil1.8 Transistörlü DEĞİL Kapı Devresi

DENEYİN YAPLIŞI:

*Şekil1.2 ve Şekil1.3’teki VEYA kapı develerinin kurduk ve doğruluk tablolarını oluşturduk.

*Şekil1.5 v3 Şeil1.6’taki VE kapı devrelerini kurduk ve doğruluk tablosunu oluşturuk

*Şekil1.8’eki devrei kurduk ve doğruluk tablosunu oluşturduk.

SONUÇ:

Devreleri kurduk ve VEYA kapı devreleri sonucunu Tablo1.12e kaydettik. VE kapı devreleri

sonucunu Tablo1.2’ye kaydettik. DEĞİL kapı devresi sonucunu da Tablo1.3’e

kaydettik.Böylece doğruluk tablolarını elde etmiş olduk.

KAYNAKLAR:

*Lojik Devre Laboratuarı Deney Kılavuzu