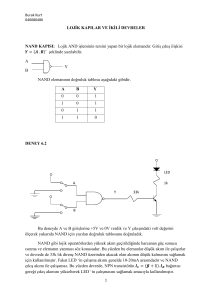

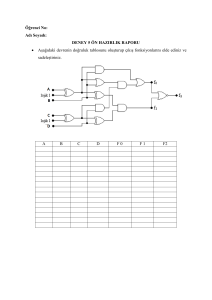

T.C. NİĞDE ÖMER HALİSDEMİR ÜNİVERSİTESİ MÜHENDİSLİK - MİMARLIK FAKÜLTESİ ELEKTRİK - ELEKTRONİK MÜHENDİSLİĞİ BÖLÜMÜ LOJİK DEVRELER LABORATUARI DENEY FÖYÜ İÇİNDEKİLER 1. Deney-1 Temel Kapı Devreleri 1.1. Ön Çalışma 1.2. Deneyin Amacı 1.3. Ön Bilgiler 1.4. VEYA kapısı 1 1 1 1 1 1.4.1.Diyot ile VEYA kapı devresi 1.4.2.Transistör ile VEYA kapı devresi 1.5. VE kapısı 1.5.1.Diyot ile VE kapı devresi 1.5.2.Transistör ile VE kapı devresi 1.6. Değil Kapısı 1.7. Deneyde Kullanılacak Cihazlar ve Devre Elemanları 1.8. Deney Çalışması 1.9. Deney ile İlgili Sorular 2. Deney-2 Temel Kapı Devreleri Kullanılarak Lojik Fonksiyonların Gerçekleştirilmesi 2.1. Ön Çalışma 2.2. Deneyin Amacı 2.3. Ön Bilgiler 2.3.1. Boolean fonksiyonlarının basitleştirilmesi 2.3.1.1. İki değişkenli karnough diyagramı 2.3.1.2. Üç değişkenli karnough diyagramı 2.3.1.3. Dört değişkenli karnough diyagramı 2.3.1.4. İsteğe bağlı durumlar 2.4. Deneyde Kullanılacak Cihazlar ve Devre Elemanları 2.5. Deney Çalışması 2.6. Deney ile İlgili sorular 2.7. Katalog Bilgileri 3. Deney-3 Kombinasyonel Lojik Devreler -I 3.1. Ön Çalışma 3.2. Deneyin Amacı 3.3. Ön Bilgiler 3.3.1.Toplayıcılar 3.3.2.Çıkarıcılar 3.4. Deneyde Kullanılacak Cihazlar ve Devre Elemanları 3.5. Deney Çalışması 3.6. Deney ile İlgili Sorular 3.7. Katalog Bilgileri 4. Deney-4 Kombinasyonel Lojik Devreler-II 4.1. Ön Çalışma 4.2. Deneyin Amacı 4.3. Ön Bilgiler 4.3.1.Kod Çözücü (decoders) 4.3.2.Kodlayıcılar (encoders) 4.4. Deneyde Kullanılacak Cihazlar ve Devre Elemanları 2 2 3 4 4 5 6 6 6 7 7 7 7 7 8 8 8 9 9 10 10 10 12 12 12 12 12 14 17 17 17 17 18 18 18 18 18 21 23 4.5. Deney Çalışması 4.6. Deney ile İlgili Sorular 4.7. Katalog Bilgileri 5. Deney-5 Kombinasyonel Lojik Devreler-III 5.1. Ön Çalışma 5.2. Deneyin Amacı 5.3. Ön Bilgiler 5.3.1.Çoğullayıcılar (multiplexers) 5.3.2.Seçiciler (demultiplexers) 5.4. Deneyde Kullanılacak Cihazlar ve Devre Elemanları 5.5. Deney Çalışması 5.6. Deney ile İlgili Sorular 5.7. Katalog Bilgileri 6. Deney-6 Ardışık Lojik Devreler-I 6.1. Ön Çalışma 6.2. Deneyin Amacı 6.3. Ön Bilgiler 6.3.1. RS flip-flop 6.3.2.D flip-flop 6.3.3.JK flip-flop 6.4. Deneyde Kullanılacak Cihazlar ve Devre Elemanları 6.5. Deney Çalışması 6.6. Deney ile İlgili Sorular 6.7. Katalog Bilgileri 7. Deney-7 Ardışık Lojik Devreler-II 7.1. Ön Çalışma 7.2. Deneyin Amacı 7.3. Ön Çalışma 7.3.1.Register 7.3.2.Shift Register 7.4. Deneyde Kullanılacak Cihazlar ve Devre Elemanları 7.5. Deney Çalışması 7.6. Deney ile İlgili Sorular 7.7. Katalog Bilgileri 8. Deney-8 Asenkron Sayıcılar 8.1. Ön Çalışma 8.2. Deneyin Amacı 8.3. Ön Bilgiler 8.3.1.Ripple Sayıcılar 8.3.2.Display Etme 8.4. Deneyde Kullanılacak Cihazlar ve Devre Elemanları 8.5. Deney Çalışması 8.6. Deney ile İlgili Sorular 8.7. Katalog Bilgileri 9. Deney-9 Senkron Sayıcılar 9.1. Ön Çalışma 9.2. Deneyin Amacı 9.3. Ön Bilgiler 9.3.1.Senkron Sayıcı 9.3.2.Ring Sayıcı 9.4. Deneyde Kullanılacak Cihazlar ve Devre Elemanları 9.5. Deney Çalışması 23 23 24 25 25 25 25 25 27 28 28 28 28 30 30 30 30 32 34 35 35 35 36 37 37 37 37 37 39 40 41 41 41 42 42 42 42 43 44 45 46 46 46 48 48 48 48 48 48 49 50 9.6. Deney ile İlgili Sorular 9.7. Katalog Bilgileri 50 50 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-1 TEMEL KAPI DEVRELERİ 1.1 Ön Çalışma Deney çalışmasında yapılacak uygulamaların benzetimlerini yaparak, sonuçlarını ön çalışma raporu olarak hazırlayınız. 1.2 Deneyin Amacı Temel kapı işlemlerinin ve bu işlemleri gerçekleştiren kapı devrelerinin incelenmesi ve gerçekleştirilmesi. 1.3 Ön Bilgiler Bilindiği gibi sayısal (dijital) elektronik sistemler temel mantık kurallarına uygun çalışan sistemlerdir. Bu tür sistemlerde gerek giriş, gerekse çıkış iki farklı duruma sahip olabilir (0 veya 1) ve bu tür sayı sistemlerine ikili (binary) sayı sistemi denir. En basitinden en karmaşığına kadar bütün mantık devrelerinde bu sayı sistemi kullanılır. Temel olarak üç lojik kapı mevcuttur. Bunlar VEYA (OR), VE (AND), DEĞİL (NOT, INVERTER) kapılarıdır. Bu temel kapıların kombinasyonlarından diğer kapı türevleri elde edilebilir. Bunlar; NOT-AND NAND (VE-DEĞİL kapısı) NOT-OR NOR (VEYA-DEĞİL kapısı) EX-OR (Exlusive OR kapısı) EX-NOR (Exlusive NOR kapısı) Bu deney çalışmasında yukarıda belirtilen temel lojik kapılar diyot ve transistörlerle kurulan çeşitli devrelerle oluşturulacaktır. Bilindiği gibi, transistörler yükselteç (amplifier) olarak geniş bir uygulama alanına sahiptir. Genel olarak bir transistör üç tür çalışma durumuna sahiptir. Kesim durumu (Cut-off) Aktif durumu Doyum durumu (Saturation) Transistörlerin kullanıldığı diğer önemli bir alan ise sayısal elektroniktir. Bu tür uygulamalarda transistörün kesim ve doyum çalışma durumlarından yararlanılır. Bir transistörün baz (base) akımı sıfır olduğunda, o transistör doyum durumuna geçer. Kesimde olan bir transistörde kolektör-emiter arası açık devre, doyumda olan bir transistörde ise kısa devre gibi davranır. Bu çalışma durumuna transistörün anahtarlama (switching) çalışma durumu denir. 1.4 VEYA kapısı VEYA (OR) kapı devresinin sembolü ve doğruluk tablosu (truth table) Şekil 1.1 ve Tablo 1.1’de görülmektedir. Bu doğruluk tablosunu sağlayacak birçok değişik VEYA kapı devresi oluşturulabilir. Bu deneyde bunlara iki farklı örnek verilecek ve incelenecektir. 1 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-1 TEMEL KAPI DEVRELERİ Tablo 1.1 Veya kapısı doğruluk tablosu GİRİŞLER A B 0 0 0 1 1 0 1 1 ÇIKIŞ F 0 1 1 1 Şekil 1.1 Veya kapısı sembolü 1.4.1 Diyot ile VEYA kapı devresi Şekil 1.2’de diyotlarla gerçekleştirilen iki girişli bir VEYA kapısı görülmektedir. Bu devrede her iki girişe de lojik 0 uygulandığında (pozitif lojiğe göre 0 volt) D A ve DB diyotlarının her ikisi de kesim durumundadır. Çünkü diyotun iletime geçebilmesi için doğru yönde polarlanması gerekir. Bu durum ise Şekil 2.3’de görüldüğü gibi diyotun anot ile katot arasındaki potansiyel farkın (VAK) anot katottan daha pozitif olmak şartı ile, silikon diyot için 0.6 V’dan germanyum diyot için 0.2 V’dan büyük olması gerekir. Girişlerin her ikisine de ‘0’ V uygulandığında, diyotların her ikisi de kesim durumunda olduğundan VEYA kapı devresi çıkışı F lojik 0 değerine sahiptir. Girişlerin en az bir tanesine lojik 1 uygulandığında (+5V) ilgili diyot doğru yönde polarlanarak girişteki lojik 1 seviyesi F çıkış noktasına aktarılır. Bu arada iletimdeki diyot üzerinde 0.6 V gerilim düşümü (silikon için) olacaktır. Sonuç olarak girişlerin hepsi lojik 0 olduğunda F çıkışı lojik 0, girişlerden herhangi biri veya her ikisi de lojik 1 olduğunda F çıkışı lojik 1 durumuna geçmektedir. Şekil 1.2 Diyot ile VEYA kapı devresi Şekil 1.3 VAK 1.4.2 Transistör ile VEYA kapı devresi Şekil 1.4’te transistörlerden oluşan iki girişe sahip bir VEYA kapı devresi görülmektedir. Bu devrede girişlerden her ikisi de lojik 0 olduğunda TA ve TB transistörleri kesim durumundadır. 2 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-1 TEMEL KAPI DEVRELERİ Bunun anlamı, her iki transistörün de kesim durumunda olmalarından dolayı R direnci üzerinden herhangi bir akım geçmeyecek ve F çıkışı lojik 0 durumunda kalacaktır. Girişlerden en az bir tanesi lojik 1 olduğunda ilgili transistör iletime (transistörün doyum durumu) geçer. Bu durumda I akımı R direnci üzerinden devresini tamamlayarak F çıkışı üzerinde bir gerilim düşümüne neden olur. Bu F çıkışı lojik 1 değerinde olduğu anlamına gelir. Şekil 1.4 Transistörlü VEYA kapısı 1.5 VE Kapısı VE (AND) kapı devresinin sembolü ve doğruluk tablosu Şekil 1.5 ve Tablo 1.2’de görülmektedir. Bu kapının çıkışı, her iki girişinin de ‘1’olduğu durumda ‘1’, diğer durumlarda ‘0’dır. VEYA kapısında olduğu gibi VE kapısının yapımı için de iki örnek verilecektir. Tablo 1.2 VE kapısı doğruluk tablosu GİRİŞLER A B 0 0 0 1 1 0 1 1 Şekil 1.5 VE kapısı 3 ÇIKIŞ F 0 0 0 1 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-1 TEMEL KAPI DEVRELERİ 1.5.1 Diyot ile VE kapı devresi Diyotlu VE kapısı Şekil 1.6’da görülmektedir. Bu devrede her iki girişte lojik 0 olduğunda DA ve DB diyotlarının her ikisi de doğru yönde polarlanacağından dolayı F çıkışında sadece 0.6V görülecektir. Bu potansiyel farkı diyot üzerinde düşen VAK gerilimidir ve lojik 0 olarak değerlendirilir. Girişlerden bir tanesi lojik 0, diğeri lojik 1 seviyesinde olduğunda durum değişmeyecektir. Çünkü bu durumda diyotlardan biri iletimde, diğer ise kesimdedir. İletim durumundaki diyotun girişi lojik 0 olduğundan dolayı F çıkışı bu diyot seviyesinde şaseye bağlandığı için lojik 0 seviyede olacaktır. Bu devrede her iki giriş lojik 1 seviyesinde olduğunda, diyotlar ters yönde polarlanmış olacak ve besleme gerilimi (+VCC) F çıkışı üzerinde görülecektir. Bu çıkış ise lojik 1 olarak değerlendirilmektedir. Şekil 1.6 Diyotlu VE kapısı 1.5.2 Transistör ile VE kapı devresi Şekil 1.7’deki devrede ise transistörle gerçekleştirilen bir VE kapı devresi görülmektedir. Bu devrede girişlerden her ikisi de lojik 0 olduğunda TA ve TB transistörleri kesim durumunda olacaktır. Bunun sonucunda C1 noktasında VCC gerilimi görülecek ve bu gerilim TF transistörünü iletime geçirecektir. Sonuç olarak F çıkışı lojik 0 durumuna gelecektir. Girişlerin her ikisi de lojik 1 seviyesinde olduğunda, TA ve TB transistörlerinin her ikisi de iletim durumunda olacak ve C1 noktası şaseye bağlanmış olacaktır. Bu durumda ise TF transistörü kesim durumuna geçecek ve F çıkışı lojik 1 seviyesine gelecektir. 4 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-1 TEMEL KAPI DEVRELERİ Şekil 1.7 Transistörlü VE kapısı 1.6 Değil Kapısı Değil (NOT) kapısının sembolü ve doğruluk tablosu Şekil 1.8 ve Tablo 1.3’de görülmektedir. Bu kapı ile uygulanan lojik sinyal terslenmektedir. Tablo 1.3 Değil kapısı doğruluk tablosu GİRİŞ A 0 1 ÇIKIŞ F 1 0 Şekil 1.8 Değil kapısı Girişine uygulanan lojik 0 işaretini çıkışa lojik 1, lojik 1 işaretini ise lojik 0 olarak çıkışa aktarmaktadır. Şekil 1.9’da ise DEĞİL kapısının transistörle gerçekleştirilmiş devresi görülmektedir. Bu devrede girişe lojik 0 uygulandığında transistör kesimde ve F çıkışında VCC 5 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-1 TEMEL KAPI DEVRELERİ gerilimi görülecektir. Bu ise lojik 1 olarak değerlendirilir. Girişe lojik 1 verildiğinde ise transistör iletime geçerek F çıkış noktası şaseye bağlanmış olur ve F çıkışında lojik 0 seviyesi görülür. Şekil 1.9 Transistörlü Değil kapısı 1.7Deneyde Kullanılacak Cihazlar ve Devre Elemanları Cadet Masterlab deney seti 1 adet AVO metre 2 adet 1N400X Diyot 4 adet LED Diyot 3 adet BC237 Transistör 2 adet 33K ohm Direnç 1 adet 270 ohm Direnç 4 adet 1K ohm Direnç 3 adet 10K ohm Direnç 1 adet 56K ohm Direnç 1 adet 100K ohm Direnç Bağlantı Kabloları 1.8 Deney Çalışması 1. Şekil 1.2 ve 1.4’deki VEYA kapı devrelerini kurarak, doğruluk tablolarını çıkartınız. 2. Şekil 1.6 ve 1.7’deki VE kapı devrelerini kurarak, doğruluk tablolarını çıkartınız. 3. Şekil 1.9’daki DEĞİL kapı devresini kurarak, doğruluk tablosunu çıkarınız. 1.9 Deney İle İlgili Sorular 1. Temel kapı devreleri ve doğruluk tablolarını kullanarak NAND, NOR, EXOR ve EXNOR kapı devrelerini çiziniz, doğruluk tablolarını çıkararak çalışmalarını anlatınız. 2. Entegre devre teknolojileri hakkında bilgi veriniz. 3. Elektronikte kullanılan pasif ve aktif elemanlar hakkında bilgi veriniz. 6 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-2 TEMEL KAPI DEVRELERİ KULLANILARAK LOJİK FONKSİYONLARIN GERÇEKLEŞTİRİLMESİ 2.1 Ön Çalışma Deney çalışmasında yapılacak uygulamaların benzetimlerini yaparak, sonuçlarını ön çalışma raporu olarak hazırlayınız. 2.2 Deneyin Amacı Tümleşik devre olarak üretilmiş kapı devreleri kullanarak; gerçekleştirilmesi. indirgenmiş fonksiyonların 2.3 Ön Bilgiler Bu deneyde lojik ifadelerin, lojik kapı entegre devreleri kullanılarak gerçekleştirilmesi incelenecektir. Bunun için ilk olarak verilen lojik ifadenin sadeleşmesi gerekmektedir. İkinci olarak, sadeleştirilen lojik ifade, entegre kapı devreleri kullanılarak gerçekleştirilecektir. Son olarak da girişlere, lojik 0 ve lojik 1 uygulanarak gerçekleştirilen devrenin lojik fonksiyonu sağlayıp sağlamadığı test edilecektir. Örnek olarak; aşağıdaki ifadeler üzerinde gerekli sadeleştirmeleri yaparak sonuç ifadeleri elde ediniz. a) F = A(A + B) b) F = B(A + A) c) F = AC + AC + C) d) F = A + B + C + D e) F = (A + B)C Not: A + A = 1 olduğundan F = (A + A)B = B olur. 2.3.1 Boolean fonksiyonlarının basitleştirilmesi Boolean fonksiyonları, cebirsel yer değiştirmelerle basitleştirildiğinde özel kurallar gerektirdiği için çeşitli güçlüklerle karşılaşılmaktadır. Diyagram yöntemi, bu güçlükleri ortadan kaldırmıştır. Diyagram yöntemi önce Veitch (1952) tarafından öne sürülmüştür. Daha sonra Karnough tarafından geliştirilmiştir. Bu sebeple bu yönteme “Karnough Diyagramı Yöntemi” denilmektedir. Bu yöntem en fazla dört değişkenli fonksiyonlar için kullanışlı olmaktadır. Beş ve daha fazla değişkenli fonksiyonlar için tablo yöntemi kullanılmaktadır. 7 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-2 TEMEL KAPI DEVRELERİ KULLANILARAK LOJİK FONKSİYONLARIN GERÇEKLEŞTİRİLMESİ 2.3.1.1 İki değişkenli karnough diyagramı Dört tane minterm’i vardır, X ve Y gibi iki giriş değişkenine sahiptir. Tablo 2.1 İki değişkenli karnough diyagramı 2.3.1.2 Üç değişkenli karnough diyagramı Bu sistemde sekiz minterm vardır. Dolayısı ile diyagram karelidir. Buradaki satır ve sütun sıralaması ikili sayı sıralaması gibi olmayıp, Gray Kod’u biçimindedir. Tablo 2.2 Üç değişkenli karnoguh diyagramı 2.3.1.3 Dört değişkenli karnough diyagramı Dört değişkenli karnough diyagramı aşağıdaki şekilde görülmektedir. Dört adet ikili (binary) değişken için on altı minterm vardır. Buradaki satır ve sütun sırlaması ikili sayı sıralaması gibi olmayıp, Gray Kodu biçimindedir. 8 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-2 TEMEL KAPI DEVRELERİ KULLANILARAK LOJİK FONKSİYONLARIN GERÇEKLEŞTİRİLMESİ Tablo 2.3 Dört değişkenli karnough diyagramı 2.3.1.4 İsteğe bağlı durumlar İsteğe bağlı durumlar tümüyle tamamlanmamış fonksiyonlara ilişkin olup, sıfır (0) veya bir (1) olarak alınabilen şartlardır. Aşağıda bu duruma ilişkin bir örnek verilmiştir. F = ∑(1,3,7) = xyz + xyz+ xy Boolean fonksiyonu aşağıdaki isteğe bağlı şartlar altında basitleştiriniz. d = ∑(0,2,5) = xyz + xyz + xyz Tablo 2.4 İsteğe bağlı durumlar için örnek karnough haritası Burada isteğe bağlı durumlardan bir tanesi 1 ve iki tanesi 0 olarak alınmıştır. F için basitleştirilmiş ifade F=z olarak elde edilmiştir. 2.4 Deneyde Kullanılacak Cihazlar ve Devre Elemanları Cadet Masterlab deney seti 1 adet avometre 1 adet 74LS00 1 adet 74LS02 1 adet 74LS04 1 adet 74LS08 1 adet 74LS32 1 adet 270 ohm direnç Bağlantı kabloları 9 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-2 TEMEL KAPI DEVRELERİ KULLANILARAK LOJİK FONKSİYONLARIN GERÇEKLEŞTİRİLMESİ 2.5 Deney Çalışması 1. Aşağıdaki Boolean fonksiyonları için çarpımların toplamı biçimindeki basitleştirilmiş ifadeleri elde ediniz ve elde ettiğimiz ifadeyi gerekli elemanları kullanarak gerçekleştiriniz. a) F(x, y, z) = ∑(1,2,3,6,7) b) F(w, x, y, z) = ∑(2,3,12,13,14,15) 2. F = A(B + CD) + BC fonksiyonunu NAND kapılarıyla gerçekleştiriniz. 3. F = A(B + CD) + BC fonksiyonunu NOR kapılarıyla gerçekleştiriniz. 2.6 Deney İle İlgili Sorular 1. F ABC D AC fonksiyonunu sadece NAND kapıları kullanarak gerçekleştiriniz. 2. F ABC D AC fonksiyonunu sadece NOR kapıları kullanarak gerçekleştiriniz. 3. F AD AC fonksiyonunu Boolean cebri fonksiyonları yardımıyla çarpım ifadeleri olarak elde ediniz. Elde edilen fonksiyonu sadece NAND kapı devreleri kullanarak gerçekleştiriniz. 4. F = ABCD + ABCD + ABCD fonksiyonunu Karnough kullanarak indirgeyiniz ve elde edilen fonksiyonu sadece NAND kapı devreleriyle gerçekleştiriniz. 2.7 Katalog Bilgileri 1. 74LS00 Katalog bilgisi 2. 74LS02 Katalog bilgisi 10 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-2 TEMEL KAPI DEVRELERİ KULLANILARAK LOJİK FONKSİYONLARIN GERÇEKLEŞTİRİLMESİ 3. 74LS04 Katalog bilgisi 4. 74LS08 Katalog bilgisi 5. 74LS32 Katalog bilgisi 11 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-3 KOMBİNASYONEL LOJİK DEVRELER-I 3.1 Ön Çalışma Deney çalışmasında yapılacak uygulamaların benzetimlerini yaparak, sonuçlarını ön çalışma raporu olarak hazırlayınız. 3.2 Deneyin Amacı MSI lojik elemanları yardımıyla kombinasyonel lojik devrelerden ÇIKARICI devrelerin gerçekleştirilerek çalışmasının incelenmesi. TOPLAYICI ve 3.3 Ön Bilgiler 3.3.1 Toplayıcılar Sayısal bilgisayarların gerçekleştirebildikleri birçok bilgi işleme şekillerinden birisi de aritmetik işlemlerdir. En temel aritmetik işlem, tek bitlik iki binary sayının toplanmasıdır. Bu basit toplama işlemi dört farklı işlemden oluşur. 0+0=0, 0+1=1, 1+0=1, 1+1=10 İlk üç işlemde toplamın boyutu bir bit olmasına rağmen, dördüncü işlemde toplayan ve toplanan binary bilgiler her ikisinin de 1 olması durumunda işlem sonucunda elde edilen toplamın boyutu iki bittir. Bu durumda elde edilen sonucun en ağırlıklı biti ‘elde’ (carry) olarak adlandırılır. İki bit bilginin toplamını gerçekleştiren kombinasyonel devrelere yarı toplayıcı (half adder, Şekil 3.1) , üç bit bilginin (en ağırlıklı iki bit ve bir önceki devreden gelen elde toplamını gerçekleştiren devreye de tam toplayıcı ( full adder), Şekil 3.2 ) denir. Tablo 3.1 Yarım toplayıcı doğruluk tablosu GİRİŞLER A B 0 0 0 1 1 0 1 1 ÇIKIŞLAR TOPLAM ELDE 0 0 1 0 1 0 1 1 Şekil 3.1 Yarım toplayıcı devresi Şekil 3.2’den de görüldüğü gibi bir tam toplayıcı, iki yarım toplayıcı ve bir OR kapısından oluşmaktadır. Tablo 3.2’de tam toplayıcı iki adet bir bitlik bilginin toplanmasını gerçekleştirmektedir. Eğer toplanacak bilgiler bir bitten büyük olursa, bit sayısı kadar tam toplayıcı paralel olarak kullanılacaktır. Şekil 2.3’den de görüldüğü gibi her tam toplayıcının elde çıkışı kendinden sonra gelen tam toplayıcının (kendinden daha ağırlıklı olan iki tam toplayıcı) elde girişine uygulanır. Şekil 3.3’de 4 bitlik bir paralel toplayıcı şematik olarak gösterilmiştir. 12 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-3 KOMBİNASYONEL LOJİK DEVRELER-I Şekil 3.2 Tam toplayıcı devresi Tablo 3.2 Tam toplayıcı devresi doğruluk tablosu GİRİŞLER A B Cin 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 0 1 1 1 0 1 1 1 1 ÇIKIŞLAR TOPLAM ELDE 0 0 1 0 1 0 0 1 1 0 0 1 0 1 1 1 Şekil 3.3 Dört bitlik paralel toplayıcı şeması 13 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-3 KOMBİNASYONEL LOJİK DEVRELER-I 3.3.2 Çıkarıcılar Toplam işleminde olduğu gibi çıkarma işleminde de dört temel işlem bulunmaktadır. Bu işlemleri gerçekleştiren kombinasyonel devrelere yarım çıkarıcı (half subtracter) denir. 0-0=0, 0-1=1, (Borç=1), 1-0=1, 1-1=0 Şekil 3.4 Yarım çıkarıcı devresi Tablo 3.3 Yarım çıkarıcı doğruluk tablosu GİRİŞLER A B 0 0 0 1 1 0 1 1 ÇIKIŞLAR FARK BORÇ 0 0 1 1 1 0 0 0 Çıkartma devreleri toplama devresine benzer. Toplayıcı devredeki, toplam çıkışı, fark çıkışına ve elde çıkışı ise borç çıkışına benzemektedir. İkili sayıları çıkarırken uygulanacak kurallar yukarıdaki tabloda açıklanmıştır. Yarım toplayıcıda elde çıkışı yerine yarım çıkarıcı devrede borç çıkışı vardır. Yukarıdaki işlemlerden ikincisine bakıldığında 0’dan 1’in çıkmayacağı görülmektedir. O halde bir sonraki bitten 1 borç alınır ve 10 ikili bilgisinden 1 çıkartılır. Şekil 3.4 ve Tablo 3.3’de bir yarım çıkarıcı devresi ve doğruluk tablosu verilmiştir. Bir tam çıkarıcı devresi ise iki yarım çıkarıcı ve bir OR kapısından oluşmaktadır. Bu devre ile doğruluk tablosu Şekil 3.5 ve Tablo 3.4’de görülmektedir. Şekil 3.6’da 4 bitlik tam toplayıcı/çıkarıcı, Şekil 3.7’de ise toplam sonucunu BCD’ye çevirebilen 4 bitlik toplayıcı devresi görülmektedir. 14 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-3 KOMBİNASYONEL LOJİK DEVRELER-I Şekil 3.5 Tam çıkarıcı devresi Tablo 3.4 Tam çıkarıcı doğruluk tablosu GİRİŞLER ÇIKIŞLAR A B Cin FARK BORÇ 0 0 0 0 0 0 1 0 1 1 1 0 0 1 0 1 1 0 0 0 0 0 1 1 1 0 1 1 0 1 1 0 1 0 0 1 1 1 1 1 15 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-3 KOMBİNASYONEL LOJİK DEVRELER-I Şekil 3.6 Dört bitlik tam toplayıcı/çıkarıcı devre Şekil 3.7 BCD çevrimli dört bit tam toplayıcı 16 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-3 KOMBİNASYONEL LOJİK DEVRELER-I 3.4 Deneyde Kullanılacak Cihazlar ve Devre Elemanları Cadet Masterlab deney seti 1 adet avometre 1 adet 74LS08 1 adet 74LS32 5. 1 adet 74LS86 1 adet 74LS83 2 adet 270 ohm direnç Bağlantı kabloları 3.5 Deney Çalışması 1. Şekil 3.3’teki 4 bitlik paralel toplayıcıyı 74LS83 paketi yardımıyla gerçekleştiriniz ve 4 bitlik toplama örnekleri yapınız. 2. Şekil 3.6’daki devreyi kurunuz ve çalışmasını inceleyiniz. 3. İki bitlik A ve B sayılarının çarpma işlemini toplayıcılar yardımı ile gerçekleştiriniz. 3.6 Deney İle İlgili Sorular 1. Şekil 3.3’deki 4 bitlik paralel toplayıcıda tam toplayıcı yerine neden yarım toplayıcı kullanılmaz. 2. Şekil 3.6’daki devrenin çalışma prensibini izah ediniz. 3. Binary çarpma ve bölme işlemleri hakkında teorik bilgi veriniz. 4. Quad Full-Adder ve NAND devre paketleri kullanarak 4 bit x 3bit çarpma devresi tasarlayınız. 3.7 Katalog Bilgileri 1. 74LS86 Katalog bilgisi 2. 74LS83 Katalog bilgisi 17 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-4 KOMBİNASYONEL LOJİK DEVRELER-II 4.1 Ön Çalışması Deney çalışmasında yapılacak uygulamaların benzetimlerini yaparak, sonuçlarını ön çalışma raporu olarak hazırlayınız. 4.2 Deneyin Amacı MSI lojik elemanları yardımıyla kombinasyonel lojik devrelerden ENCODER ve DECODER devrelerin gerçekleştirilerek çalışmalarının incelenmesi. 4.3 Ön Bilgiler Bilindiği gibi dijital sistemlerde devreler, kombinasyonel (combinational) ya da ardışık (sequential) devreler şeklinde kurulmuş olabilirler. Kombinasyonel devreler lojik kapılardan oluşurlar ve herhangi bir andaki çıkışları o andaki girişlerinin durumlarına bağlıdır. Bir kombinasyonel devrenin çıkışı, girişin bir önceki durumunu etkilemez. Kombinasyonel devre, Boolean fonksiyonları yardımıyla mantıksal olarak tanımlanmış sadece bir özel işlemi yerine getiren devredir. Ardışık devreler ise lojik kapıların yanı sıra depolama elemanlarını (flip-flop) da kapsarlar. Buna bağlı olarak ardışık devrenin çıkışları, depolama elemanlarının durumuna ve harici girişlerine bağlıdır. Bir kombinasyonel devre, girişler ve bu girişlere bağlı çıkışlardan oluşur. Kombinasyonel devrenin çıkışlarında, girişlerine herhangi bir anda uygulanacak bilgiye göre o anda devrenin kuruluş amacına uygun şekilde bilgiler elde edilecektir. Bu deney çalışmasında kombinasyonel lojik devrelerden decoder ve encoder devreleri incelenecektir. 4.3.1 Kod çözücü (decoders) Decoder, N giriş hattından oluşan binary giriş bilgisini 2N çıkış hattına çevirebilen kombinasyonel devredir. Decoderlar Şekil 4.1’de görüldüğü gibi, yapı olarak N binary giriş hattını M çıkış hattına çevirdiklerinden dolayı NxM ya da N-M decoder olarak adlandırılırlar. Burada M=2N ilişkisi söz konusudur. Şekil 4.1 NxM Decoder’ın genel görünüşü 18 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-4 KOMBİNASYONEL LOJİK DEVRELER-II Genel olarak decoderlar IC paketler içerisinde 2x4, 3x8, 4x10, 4x16 şeklinde düzenlenmiş olarak bulunurlar. Şekil 4.2 ve Tablo 4.1’de 2x4 decoder devresi ve doğruluk tablosu görülmektedir. Şekil 4.2’de görüldüğü gibi decoder devre A ve B girişlerine ve bu girişlerin kombinasyonuna bağlı olarak dört çıkışa sahiptir. Şekil 4.2 2x4 Decoder devresi Tablo 4.1 2x4 Decoder doğruluk tablosu GİRİŞLER E A B 0 X X 1 0 0 1 0 1 1 1 0 1 1 1 D0 0 1 0 0 0 ÇIKIŞLAR D1 D2 0 0 0 0 1 0 0 1 0 0 D3 0 0 0 0 1 Girişe uygulanacak bilginin her kombinasyonunda çıkışlardan sadece birinde lojik 1 seviye görülecek, diğer çıkışlar ise lojik 0 seviyeye sahip olacaklardır. Şekil 4.1’de görüldüğü gibi, NxM decoder devresi giriş ve çıkış hatlarından başka bir de ENABLE girişine sahiptir. Eğer NxM decoder devresi gerekli olan ENABLE sinyaline sahip değilse (ENABLE=0) decoder devre yapması gereken işlemi yerine getiremez ve devre pasif durumdadır. Uygun ENABLE sinyali uygulandığında (ENABLE=1) decoder devre aktif durumdadır ve normal çalışma işlemlerini yerine getirir. Ayrıca ENABLE girişi birden çok decoder devrelerinin bulunduğu dijital devrelerde, uygun bir seçici lojik devre yardımıyla istenilen decoderli devrenin seçilmesinde kullanılabilir. Şekil 4.3’de ENABLE girişli 3x8 decoder devresi ve doğruluk tablosu görülmektedir. Değişik kapasitelerde decoder devreleri IC paketlerinde mevcut olduğu gibi (2x4, 3x8, 4x10, 4x16) birkaç decoder yardımıyla daha büyük kapasitelerde decoder devreler oluşturulabilir. Örnek olarak 4x16 decoder devre elde edebilmek için 3x8 decoderlardan faydalanılabilir. Şekil 4.4’de görüldüğü gibi 4 bitlik bir binary kodun A0, A1 ve A2 hatları her iki decoder’ın x, y ve z girişlerine uygulanır. A3, hattı ise birinci decoder’ın ENABLE girişine direk olarak bağlanır. 4 bitlik binary kod 16 değişik kombinasyona sahiptir. A3=0 olduğu sürece birinci decoder aktif durumda olacak, ikinci decoder uygun ENABLE sinyaline sahip olmadığından dolayı pasif durumda olacaktır. A3=1 olduğunda ise ikinci decoder aktif duruma geçecektir. 19 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-4 KOMBİNASYONEL LOJİK DEVRELER-II Şekil 4.3 3x8 Decoder devresi Tablo 4.2 3x8 Decoder devresi doğruluk tablosu GİRİŞLER E X Y Z 0 X X X 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 D0 D1 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 20 D2 0 0 0 1 0 0 0 0 0 ÇIKIŞLAR D3 D4 D5 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 0 0 D6 0 0 0 0 0 0 0 1 0 D7 0 0 0 0 0 0 0 0 1 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-4 KOMBİNASYONEL LOJİK DEVRELER-II Şekil 4.4 3x8 Decoder yardımıyla 4x16 decoder devrenin kurulması 4.3.2 Kodlayıcılar (encoders) Encoder bir decoderin tersi işlem yapan kombinasyonel bir lojik devredir. Bir encoder devre 2 N giriş hattına ve N çıkış hattına sahiptir. Çıkış hatlarından 2N değişken giriş için binary kodlar üretir. Girişler M ve çıkışlar N olarak adlandırıldığında MxN ya da M-N encoder olarak tanımlanabilir. Şekil 4.5 MxN Encoder’in genel görünüşü 21 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-4 KOMBİNASYONEL LOJİK DEVRELER-II Şekil 4.6 ve Tablo 3.3’den da görüleceği gibi encoder devresi 8 girişe ve bu girişlere karşılık binary olarak üretilecek kodların elde edileceği üç çıkışa sahiptir. Girişe 28=256 mümkün olabilecek durum uygulanabilmesine karşılık bunların sadece doğruluk tablosunda görüldüğü gibi 8 giriş değişkeni giriş olarak kabul edilecek ve bu girişlere karşılık binary kodlar üretecektir. Bu işlem bir anlamda decimal girişin binary forma dönüştürülmesi olarak da adlandırabilir (decoder devrede ise binary giriş büyüklüğünün decimal forma dönüştürülmesi söz konusudur). Şekil 4.6’da görülen encoder devresi IC paketler halinde mevcut değildir. IC paketler halinde elde edilebilecek bir encoder devresi öncelikli çevrim yapan encoder (priority encoder) olarak adlandırılır. Bunun anlamı şudur; encoder’a giriş olarak uygulanan her hattın bir öncelik sırası vardır. Buna göre girişlerden biri en yüksek öncelikli giriş (D7) ve bir diğeri en düşük öncelikli giriştir (D0). Örnek olarak bu girişlerden en yüksek öncelikli girişe karşılık bir binary kod üretecektir. Burada D5 girişi D2’ye göre daha öncelikli giriştir ve çıkışta 101 binary kodu üretilecektir. 74148 böyle bir encoder’a örnektir. Şekil 4.6 Encoder devresi 22 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-4 KOMBİNASYONEL LOJİK DEVRELER-II Tablo 4.3 Encoder devresi doğruluk tablosu D0 1 0 0 0 0 0 0 0 D1 0 1 0 0 0 0 0 0 D2 0 0 1 0 0 0 0 0 GİRİŞLER D3 D4 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 D5 0 0 0 0 0 1 0 0 D6 0 0 0 0 0 0 1 0 D7 0 0 0 0 0 0 0 1 ÇIKIŞLAR X Y Z 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 4.4 Deneyde Kullanılacak Cihazlar ve Devre Elemanları CADET Masterlab deney seti 1 adet AVO Metre 1 adet 74138 1 adet 74139 1 adet 74148 1 adet 270 ohm direnç Bağlantı kabloları 4.5 Deney Çalışması 1. 74139 IC paketi içerisinde bulunan iki adet 2x4 decoder yardımı ile 3x8 decoder devresini gerçekleştiriniz. 2. 74148 IC paketi ile 8x3 encoder devresini kurup çalıştırınız. 3. Enable girişi olan 2x4 decoder’i NOR kapıları ile gerçekleştiriniz. 4. 2x4 decoder paketleri yardımıyla 4x16 decoder devresini gerçekleştiriniz. 4.6 Deney İle İlgili Sorular 1. 3x8 decoder paketleri yardımıyla 5x32 decoder devresini gerçekleştiriniz. 2. 74148 IC paketi 8x3 öncelikli çevrim yapan bir encoder’dır. 74148 ve lojik kapılar yardımı ile 10x4 encoder devresini gerçekleştiriniz. 23 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-4 KOMBİNASYONEL LOJİK DEVRELER-II 4.7 Katalog Bilgileri 1. 74LS138 Katalog bilgisi 2. 74LS139 Katalog bilgisi 3. 74LS148 Katalog bilgisi 24 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-5 KOMBİNASYONEL LOJİK DEVRELER-III 5.1 Ön Çalışma Deney çalışmasında yapılacak uygulamaların benzetimlerini yaparak, sonuçlarını ön çalışma raporu olarak hazırlayınız. 5.2 Deneyin Amacı MSI lojik elemanları yardımıyla kombinasyonel lojik devrelerden MULTIPLEXER ve DEMULTIPLEXER devrelerin kurulması ve incelenmesi. 5.3 Ön Bilgiler Bu deney çalışmasında dördüncü deneye ilave olarak kombinasyonel lojik devrelerden multiplexer ve demultiplexer devrelerin çalışmaları incelenecektir. 5.3.1 Çoğullayıcılar (multiplexers) Çoğullama (multiplexing) işlemi, birden fazla bilgi biriminin daha az kanal ya da hattan ileletilmesi anlamına gelir. Bir dijital çoğullayıcı (multiplexer) giriş hatlarına uygulanan binary bilgilerden sadece bir tanesini seçerek tek bir çıkışa veren kombinasyonel bir devredir. Girişteki hatlardan herhangi birinin seçilme işlemi ise seçme hatları (select line) yardımı ile kontrol edilir. Şekil 5.1’de görüldüğü gibi bir multiplexer 2N girişe, N seçme (select) ucuna ve bir çıkış ucuna sahiptir. Bu multiplexer devresi 2N girişe ve 1 çıkışa sahip olduğundan Nx1 multiplexer olarak adlandırılır. Genel olarak 2x1, 4x1, 8x1, 16x1 multiplexer devreleri oluşturulabilir. Şekil 5.1 Multiplexer devresinin genel görünümü Şekil 5.2 ve Tablo 5.1’de 4x1 multiplexer devresi ve doğruluk tablosu görülmektedir. Şekilde de görüldüğü gibi 4 binary bilgi girişi ve bu girişlerden istenilen birini seçmek için 2 seçme (select) hattı mevcuttur. Seçme ucuna uygulanacak seçme bilgisine göre istenilen bilgi seçilmiş ve çıkışa aktarılmış olur. multiplexer devre ayrıca bilgi seçici (data selector) olarak da adlandırılır. Çoğullanacak bilginin 1 bitlik değil de daha fazla olması durumunda aynı mantıktan hareket ederek gerekli multiplexer devresi kurulabilir. Örnek olarak A4 A3 A2 A1 ve B4 B3 B2 B1 bilgi bloklarının çoğullanmasını ele alırsak böyle bir işlemi yapacak multiplexer Şekil 5.3’de 25 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-5 KOMBİNASYONEL LOJİK DEVRELER-III görüldüğü gibidir. Şekilde görüldüğü gibi S=0 olduğunda A bilgi bloğu, S=1 olduğunda B bilgi bloğu seçilerek çıkışa aktarılır. Böyle bir multiplexer dörtlü 2x1 multiplexer olarak adlandırılır. Tablo 5.1 4x1 Multiplexer doğruluk tablosu S1 0 0 1 1 Şekil 5.2 4x1 Multiplexer devresi Şekil 5.3 Dörtlü 2x1 multiplexer 26 S0 0 1 0 1 Y I0 I1 I2 I3 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-5 KOMBİNASYONEL LOJİK DEVRELER-III 5.3.2 Seçiciler (demultiplexers) Demultiplexer devre multiplexer devrenin tersi işlem yapan kombinasyonel bir devredir. Bir demultiplexer devre tek bir giriş hattından aldığı bilgiyi N seçme (select) hattına ile uygulanan seçme bilgisine göre 2N hattan birine iletir. Şekil 5.4’de görüldüğü gibi 1 girişe, 2 N çıkışa ve N seçme ucuna sahiptir. Şekil 5.4 Demultiplexer devresinin genel görünüşü Genel olarak demultiplexer devreleri 1x2, 1x4, 1x8, 1x16… olarak gerçekleştirilir. Şekil 5.5 ve Tablo 5.2’de 1x4 demultiplexer devresi ve doğruluk tablosu görülmektedir. Bu devre aynı zamanda 2x4 decoder devresidir. Aralarında uygulama farkı şudur; Decoder devrede girişin uygulandığı hatlar demultiplexer devrede seçici uç olarak kullanılır. Decoder devredeki ENABLE ucu ise demultiplexer devrede bilgi girişi olarak kullanılır. Şekil 5.5 1x4 Demultiplexer devresi Tablo 5.2 1x4 Demultiplexer doğruluk tablosu GİRİŞLER E A B 1 X X 0 0 0 0 0 1 0 1 0 0 1 1 D0 0 1 0 0 0 27 ÇIKIŞLAR D1 D2 0 0 0 0 1 0 0 1 0 0 D3 0 0 0 0 1 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-5 KOMBİNASYONEL LOJİK DEVRELER-III 5.4 Deneyde Kullanılacak Cihaz ve Devre Elemanları CADET Masterlab deney seti 1 adet 74LS151 1 adet 74LS153 1 adet 74LS155 1 adet 74LS157 1 adet 74LS04 10 adet LED 1 adet 270 ohm Direnç Bağlantı Kabloları 5.5 Deney Çalışması 1. 74LS153 ve 74LS157 IC paketleri ile 8x1 multiplexer devresini kurup çalışmasını inceleyiniz. 2. 74155 IC paketi ile 1x4 demultiplexer devresini kurup çalışmasını inceleyiniz. 3. İki tane 2 bitlik A ve B sayısını karşılaştıran ve A ≥ B olduğu durumda çıkışta lojik 1 ifadesini veren devreyi 4x1 multiplexer ile gerçekleştiriniz. 4. İki tane 2 bitlik A ve B sayısını karşılaştıran ve A ≥ B olduğu durumda çıkışta lojik 1 ifadesini veren devreyi 8x1 multiplexer ile gerçekleştiriniz. 5.6 Deney İle İlgili Sorular 1. 2x1 MUX’lar yardımı ile 16x1 MUX devresini gerçekleştiriniz. 2. 4x1 MUX’lar yardımı ile 16x1 MUX devresini gerçekleştiriniz. 3. 4x1 DEMUX’lar yardımı ile 4’er bitlik grupları seçebilen DEMUX devresi gerçekleyiniz. 5.7 Katalog Bilgileri 1. 74LS151 Katalog bilgisi 2. 74LS153 Katalog bilgisi 28 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-5 KOMBİNASYONEL LOJİK DEVRELER-III 3. 74LS155 Katalog bilgisi 4. 74LS157 Katalog bilgisi 29 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-6 ARDIŞIK LOJİK DEVRELER-I 6.1 Ön Çalışma Deney çalışmasında yapılacak uygulamaların benzetimlerini yaparak, sonuçlarını ön çalışma raporu olarak hazırlayınız. 6.2 Deneyin Amacı Ardışık devrelerin temeli olan FLIP-FLOP (FF) devrelerinin çalışma esaslarının incelenmesi ve gerçekleştirilmesi. 6.3 Ön Bilgiler Önceki deneylerde kombinasyonel lojik devre elemanlarından DECODER, ENCODER, MULTIPLEXER ve DEMULTİPLEXER devreleri incelenmişti. MSI Lojik devre elemanlarının diğer grubu ise ardışık (Sequential) lojik devre elemanlarıdır. Bir ardışık devre; bir flip-flop grubundan ve kapı devrelerini kapsayan bir kombinasyonel devreden oluşur. Bir ardışık devrede temel eleman flip-flop’lardır. Çünkü böyle bir devreden flip-flop çıkarıldığında geriye kalan devre sadece bir kombinasyonel devredir. O halde; kombinasyonel bir devreyi de ardışık devre olarak adlandırabiliriz. Bu deney çalışmasında ardışık lojik devrelerin temelini teşkil eden FLIP-FLOP’lar incelenecektir. Bilindiği gibi flip-floplar temel depolama birimleridir. Her flip-flop bir bitlik dijital bilgiyi (0 veya 1) üzerinde depolayabilir. Temel olarak dört flip-flop tipi vardır. Bunlar; RS Flip-Flop D Flip-Flop JK Flip-Flop T Flip-Flop 6.3.1 RS flip-flop Şekil 6.1’de görüldüğü gibi RS FF’un S(set) ve R(reset) olmak üzere iki girişi ve olmak üzere iki çıkışı bulunmaktadır. Q çıkışı RS FF’un o andaki durumunu gösterir. Eğer Q=1 ise FF “Set” edilmiş, Q=0 ise FF “Reset” edilmiş demektir. Tablo 6.1 RS flip–flop doğruluk tablosu Şekil 6.1 RS flip–flop 30 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-6 ARDIŞIK LOJİK DEVRELER-I RS-FF’u NAND ve NOR kapıları yardımıyla iki ayrı şekilde gerçekleştirilmesi mümkündür. Şekil 6.2, Tablo 6.2, Şekil 6.3 ve Tablo 6.3’te bu flip-flop gerçekleştirmeleri ve doğruluk tabloları görülmektedir. Doğruluk tablolarından da görüleceği gibi NAND ve NOR kapıları ile yapılan RS-FF’lar arasında küçük bir fark vardır. S ve R girişlerinin aynı olduğu durumlarda, (S, R=1 ve S, R=0) NOR kapıları ile yapılan FF’un çıkışları ile NAND kapıları ile yapılan FF’un çıkışlarının değişik durumlara sahip olduğuna dikkat ediniz. Burada sözü edilen RS-FF’lar asenkron bir çalışma göstermektedir. Bunun anlamı şudur; FF’un S ve R girişlerine uygulanan lojik değerler değiştiğince çıkışlar girişlere bağlı olarak direkt etkilenecektir. RS FF bazı ilavelerle eş zamanlı (senkron) çalışır duruma getirilebilir. Yani FF’un girişlerindeki herhangi bir değişiklik çıkışa hemen aktarılamaz. Aktarma işlemi için bir kontrol devresine ihtiyaç vardır. Bu durum ise RS FF’a bir CLK (clock) girişi eklemekle sağlanabilir. Şekil 6.4’de senkron olarak çalışan CLK girişli bir RS FF devresi görülmektedir. Burada CLK=0 olduğunda FF’un S ve R girişlerine ne değer verilirse verilsin ve çıkışları girişlerden etkilenmeyecektir. CLK=1 olduğunda FF normal çalışmasını gösterecektir. Sonuç olarak; FF’un çalışması CLK girişine bağımlıdır. Şekil 6.2 NOR Kapılarıyla gerçekleştirilmiş RS flip–flop Tablo 6.2 NOR Kapılarıyla gerçekleştirilmiş RS flip–flop doğruluk tablosu Şekil 6.3 NAND Kapılarıyla gerçekleştirilmiş RS flip–flop 31 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-6 ARDIŞIK LOJİK DEVRELER-I Tablo 6.3 NAND Kapılarıyla gerçekleştirilmiş RS flip–flop doğruluk tablosu Şekil 6.4 NAND Kapılarıyla gerçekleştirilmiş clk girişli RS flip–flop 6.3.2 D flip-flop D tipi FF tek girişli bir depolama birimidir. Bu giriş D (data) girişi olarak adlandırılır. D girişine uygulanan bilgi (0 veya 1) çıkışa CLK girişine uygulanan bir işaret yardımı ile aktarılır. Şekil 6.5 ve Tablo 6.4’te D tipi FF’un sembolik gösterilimi ve doğruluk tablosu görülmektedir. D tipi FF, RS FF’a bazı değişiklikler yapılarak elde edilir. Bu değişiklik sadece RS FF’un girişleri arasına bir INVERTER eklenerek sağlanır. Şekil 6.6’da CLK girişli bir RS FF yardımıyla elde edilen D tipi FF görülmektedir. Tablo 6.4 D flip–flop doğruluk tablosu Şekil 6.5 D flip–flop Birbirlerinden farklı özelliklere sahip çeşitli D tipi FF’lar mevcuttur. Bu tipler FF’un CLK girişine uygulanan zamanlama (clock) işaretinin algılanmasına göre; kenar tetiklenmeli (edgesensitive) ve seviye tetikleme (level-sensitive) flip-floplar olmak üzere iki gruba ayrılırlar. Seviye tetiklemeli FF’lar genellikle LATCH olarak adlandırılırlar. Bu iki grup FF’u birbirinden ayırt etmek için kenar tetiklemeli FF’un CLK girişine (>) işareti konur (Şekil 6.7). 32 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-6 ARDIŞIK LOJİK DEVRELER-I Şekil 6.6 RS-FF yardımıyla gerçekleştirilmiş D–FF Kenar tetiklemeli D tipi FF’un çalışması şöyledir. Şekil 6.8’de görüldüğü gibi CLK işareti gelinceye kadar Q çıkışı değerini korur. Yeni gelen CLK işareti ile D deki bilgi yeniden Q çıkışına aktarılır. Şekil 6.7 a) Kenar tetiklemeli D-FF b) Seviye tetiklemeli D–FF Seviye tetiklemeli D tipi FF’un (LATCH) çalışması ise şöyledir. Şekil 6.9’da görüldüğü gibi CLK işaretinin lojik 1 seviyesine geçtikten ve lojik 1 seviyesinde kaldığı sürece D girişindeki bilgi olduğu gibi Q çıkışına aktarılır. CLK işareti lojik 1 seviyesinden lojik 0 seviyesine geçtiği anda D girişindeki en son bilgi Q çıkışına LATCH (kilitlenmiş) olacaktır. Dolayısıyla CLK işaretinin yeniden lojik 1 olmasına kadar değişmeyecektir. Şekil 6.8 Kenar tetiklemeli D-FF’un çalışması 33 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-6 ARDIŞIK LOJİK DEVRELER-I Şekil 6.9 Seviye tetiklemeli D-FF (LATCH)’un çalışması D tipi FF’larda ayrıca PRESET ve CLEAR olmak üzere iki ayrı giriş mevcuttur. Bu iki giriş D tipi FF’un girişlerinden bağımsız olarak FF’un durumunu asenkron olarak etkiler. PRESET=0 iken Q daima set durumunda (Q=1) ve PRESET=1 iken FF normal çalışma özelliklerini gösterir. CLEAR=0 iken Q daima reset durumundadır. (Q=0) ve CLEAR=1 iken FF normal çalışma özelliğini devam ettirir. Yani FF’un normal çalışabilmesi için bu iki girişinde lojik 1 seviyesinde olması gerekir. Bu iki giriş kesinlikle aynı anda kullanılmamalıdır. Boşta çalışmada her ikisi de lojik 1, aktif hale getirmede biri lojik 1 iken diğeri lojik 0; PRESET=CLEAR=0 durumu tanım gereği kesinlikle uygulanmamalıdır. 6.3.3 JK flip–flop Tablo 6.5 JK flip–flop doğruluk tablosu Şekil 6.10 JK flip–flop Bir JK FF, beş girişe (J, K, CLOCK, PRESET, CLEAR) iki çıkışa (Q ve Q’) sahiptir. Şekil 6.10 ve Tablo 6.5’te JK FF’un sembolik şeklini ve doğruluk tablosunu göstermektedir. PRESET ve CLEAR girişleri D tipi FF’daki gibidir. Doğruluk tablosundan da görüleceği gibi JK FF, RS FF’a oldukça benzer. Aralarındaki fark şudur; RS FF’un her iki girişinin lojik 1 olması durumunda sonuç belirsizdi. JK FF’da ise her iki girişinde lojik 1 olması durumunda ve CLK girişi 34 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-6 ARDIŞIK LOJİK DEVRELER-I uyarıldığında Q çıkışı bulunduğu son durumun tersi duruma sahip olur. Bu çalışma durumunda CLK uçlarına uygulanan clock darbesinin frekansı ikiye bölünür. Bu özelliğinden dolayı sayıcı dizaynlarında en çok kullanılan FF tipidir. 6.4 Deneyde Kullanılacak Cihazlar ve Devre Elemanları CADET Masterlab deney seti Osiloskop Frekans Jeneratörü 1 adet 74LS00 1 adet 74LS02 1 adet 74LS04 1 adet 74LS74 1 adet 74LS75 1 adet 74LS76 Bağlantı Kabloları 6.5 Deney Çalışması 1. Şekil 6.7 a) ve b)’deki D tipi FF’ların çalışmalarını 7474 ve 7475 IC paketleri yardımıyla inceleyiniz ve aralarındaki farkı gözlemleyiniz. 2. Şekil 6.10’daki JK FF doğruluk tablosunu 7476 IC paketi yardımıyla çıkarınız ve çalışmalarını inceleyiniz. 3. JK FF’un J ve K girişleri lojik 1 seviyesinde iken CLK girişine 1 KHz’lik kare dalga uygulayıp Q çıkışında elde edilen dalga formunu gözleyiniz ve yorumlayınız. 4. D FF’tan JK FF’a dönüşüm devresini tasarlayınız. 5. S, R, CLK, PRESET ve CLEAR grişlerine sahip RS-FF devresini sadece NAND kapıları kullanarak tasarlayınız. 6.6 Deney İle İlgili Sorular 1. Şekil 6.7 a) ve b)’deki FF’ların CLK girişlerine INVERTER ilave edildiği durumda çalışmalarını şekil çizerek açıklayınız. 2. Şekil 6.10’daki JK FF’un Q çıkışını aynı özelliklere sahip diğer bir JK FF’un CLK girişi bağlandığında en son FF’un Q çıkışında elde edilen dalga şeklini çizerek anlatınız. 3. T tipi FF hakkında bilgi veriniz. Doğruluk tablosunu çıkararak hangi FF’u kullanarak T tipi FF elde edebileceğimiz konusunda fikir yürütünüz. 35 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-6 ARDIŞIK LOJİK DEVRELER-I 6.7 Katalog Bilgileri 1. 74LS74 Katalog bilgisi 2. 74LS75 Katalog bilgisi 3. 74LS76 Katalog bilgisi 36 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre LaboratuarI DENEY-7 ARDIŞIK LOJİK DEVRELER-II 7.1 Ön Çalışma Deney çalışmasında yapılacak uygulamaların benzetimlerini yaparak, sonuçlarını ön çalışma raporu olarak hazırlayınız. 7.2 Deneyin Amacı Ardışık lojik devrelerden olan REGISTER (Kaydedici) devrelerinin ve SHIFT REGISTER (kaydırmalı kaydedici) devrelerinin kurulması ve çalışma esaslarının incelenmesi. 7.3 Ön Çalışma 7.3.1 Register Ardışık devrelerin bir üyesi olan register; bir binary bilgiyi tutmak için kullanılan binary depolama hücreleri (flip-flop) grubundan oluşan bir devre olarak tanımlanabilir. N-bitlik bir register, N adet flip-floptan oluşur ve N-bit binary bilgiyi depolar. Bu register devresi flip-floplar haricinde kapılardan oluşan bir kombinasyonel devreyi de bünyelerinde bulundurabilirler. Böyle bir devrede flip-floplar binary bilgiyi depolama görevini, kapı devrelerinden oluşan kombinasyonel devre ise binary bilginin registerın ne zaman ve nasıl depolanacağını kontrol eder. MSI devre olarak elde edilebilecek birçok değişik register tipi mevcuttur. En basit register ise yardımcı kapı devreleri kullanılmaksızın sadece D tipi flip-floplardan oluşan registerdir. Şekil 7.1, D tipi flip-floptan oluşan 4 bitlik basit bir registera örnektir. Şekil 7.1 4-Bit register Clock sinyal girişi (CP) dört girişte bulunan bilgilerin (I4-I1) registera depolanmasını sağlar. Clock sinyalinin uygulanması ile 4-bitlik binary bilgi 4-bit registera kaydedilmiş olur ve depolanmış bilgiler registerın çıkışından (A4-A1) gözlenebilir. Bir register dizaynında en önemli nokta, kullanılacak flip-flopların tetikleme tipine (clock girişi) karar vermektir. Eğer flip-floplar D tipi latch’lerden seçilmiş ise, D girişlerindeki bilgiler CP=1 iken Q çıkışlarına transfer edilecektir ve CP=1 olduğu sürece D girişlerindeki bilgiler sürekli Q çıkışına aktarılacaktır. CP=0 olduğu anda ise D girişindeki bilgiler Q çıkışında tutulmuş olacak, CP=1 oluncaya kadar böyle kalacaktır. Bir başka deyişle CP=0 olduktan sonra D girişlerine uygulanacak bilgiler Q çıkışlarına aktarılamayacaktır. Burada sözü edilen flip-flop grubu clock palsının süresine duyarlıdır (seviye tetikleme) ve LATCH olarak anılır. CP girişi ise G şeklinde isim değiştirir. 37 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre LaboratuarI DENEY-7 ARDIŞIK LOJİK DEVRELER-II Önemli bir not olarak bilinmelidir ki Clock palslarının süresine duyarlı flip–floplar register düzenlemelerinde kullanılmamalıdır. Diğer bir deyişle; ardışık devrelerde clock palsının geçiş zamanına duyarlı flip-floplar (kenar tetiklemeli) tercih edilmelidir. Bunun nedeni ise şudur; clock darbe süresine duyarlı flip-floplar grubuna bir bilgiyi kaydetmek için (saklı tutma) clock darbe süresinin pozitif (düşme) veya negatif (yükselme) darbe süresinin değişim gösterdiği anı beklemek gerekir (Şekil 6.9’daki seviye tetiklemeli D flip-flopların çalışmasına bakınız). Bu süre ise bilginin kayıt edilmesinde bir zaman gecikmesi meydana getirir. Bu durum kullanımda ise bazı zorluklara yol açabilir. Buna karşılık, clock darbesinin sadece geçiş anına bağımlı olarak çalışan flip-floplar (kenar tetiklemeli) üzerinde depolanacak bilgi, clock palsının bir seviyeden diğer seviyeye geçtiği anda (seviye değişme anı) flip-floplar üzerinde depolanacağından herhangi bir zaman gecikmesi söz konusu olmayacaktır. Bu durumda daha güvenilir bir depolama işlemi getirilmiş olacaktır. Şekil 7.2 Clock işaretlerinin özellikleri Sonuç olarak; clock palsının geçiş zamanına duyarlı flip-floplar grubu REGISTER, buna karşılık clock palsının süresine duyarlı flip-floplar grubu ise LATCH olarak anılır.Bir registere yeni bilgiler transfer etme işlemi, registerı yükleme (loading) olarak adlandırılır. Eğer registera bütün bilgiler aynı anda tek bir clock palsı ile yükleniyorsa, register paralel olarak yüklenmiş denir. Şekil 7.1’deki register devresinde girişlerdeki bütün bilgiler paralel olarak CP girişine uygulanan tek bir clock palsı ile yüklenmektedir. Diğer bir deyişle, CP registera yeni bilgilerin depolanmasını kontrol eden bir ENABLE sinyali olarak tanımlanabilir. Şekil 7.3’deki devrede ise RS flip-floplardan oluşan ve yükleme kontrol girişine (Load Control Input) sahip 4-bitlik register görülmektedir. Bu devre Şekil 7.1’den farklı yapıdadır. Depolanmak istenen bilgiler LOAD kontrol girişi ile AND’lenerek RS flip-flop girişlerine uygulanmaktadır. Bunun anlamı ise depolama işleminin LOAD kontrol girişine bağımlı olmasıdır. Clock darbelerinin sürekli şekilde flip–floplara uygulanmasına karşılık LOAD kontrol girişi, registerın işlemlerini kontrol eden giriş durumundadır. Şekil 7.3’den görüldüğü gibi iki AND kapısı, bir INVERTER ve I girişi yardımıyla flip-flop’un R ve S girişlerine uygulanacak bilgi tayin edilmiş olacaktır. Eğer LOAD=o ise R ve S her ikisi de lojik 0 değerine sahip olacaktır ve flip-flop durumunu değiştirmeyecektir. Yani I girişindeki bilgi flip-flop girişine uygulanmamış olacaktır. LOAD=1 olduğunda I girişine uygulanan bilgi; iki AND kapısı ve bir INVERTER’den oluşan kombinasyonel devre yardımıyla da flip-flop’a depolanmış olacaktır. 38 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre LaboratuarI DENEY-7 ARDIŞIK LOJİK DEVRELER-II Şekil 7.3 4 Bit register (paralel yüklemeli) Clear girişi ise registerın üzerinde depolanmış olan bilgilerin silinmesini sağlar. CLEAR=0 olduğunda depolanmış bilgiler silinir ve CLEAR=1 olduğunda register etkilenmeden normal çalışma özelliklerini sürdürür. 7.3.2 Shift register Üzerindeki bilgiyi sağ ya da sol doğrultuda kaydırabilen registera SHIFT REGISTER denir. Bir shift registerın yapısı arka arkaya kaskad olarak bağlanmış flip-floplar zincirinden oluşur. Bu yapıda her flip-flop’un çıkışı bir sonraki flip-flop’un girişine bağlanmaktadır ve bütün flipflopların clock girişleri paralel olarak bağlanmıştır. En basit shift register Şekil 7.4’de görüldüğü gibi sadece flip-floplardan oluşur. Her clock darbesi sonunda registerlardaki bilgiler bir sağa kaydırılmış olur. Kaydırma işlemi (shift operation) esnasında shift registerda kaydırılacak bilgiler seri girişten uygulanır. 39 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-7 ARDIŞIK LOJİK DEVRELER-II Şekil 7.4 En Basit Shift Register Shift registerın seri çıkışından her kaydırma işlemi sonunda çıkışına aktarılacak bilgiler elde edilmiş olur. Ayrıca her flip-flop’un Q çıkışları, beraberce paralel çıkış olarak da kullanılabilir. Genel olarak shift registerlar paralel dijital bilgiyi seri dijital bilgiye, ya da seri dijital bilgiyi paralel dijital bilgiye dönüştürebilir. Ayrıca bu çevrimler esnasında çevrimin yönü de seçilebilir (74164 ve 74165 entegrelerine bakınız). Örnek olarak seri bilginin paralele çevrilmesini inceleyelim. Dört bitlik shift registerda ilk olarak 0111 dijital bilgisi depolu olduğu kabul edilirse, shift registere uygulanacak her clock darbesinde bir bit sağa kayacak ve 4 clock darbesi sonunda ise daha önce depolanmış bulunan bilginin tamamı seri çıkıştan dışarıya atılmış olacaktır. Bu olaylar sırasında seri girişten uygulanacak bilgiler shift registera depolanmış olacaktır (Şekil 7.5). Bu esnada shift registerdaki kaydırma işleminin sağa doğru olduğuna dikkat ediniz. Şekil 7.5 Shift registerda kaydırma işleminde adımlar 7.4 Deneyde Kullanılacak Cihazlar ve Devre Elemanları CADET Masterlab deney seti 1 adet 74LS164 1 adet 74LS165 1 adet 74LS174 1 adet 74LS194 1 adet 270 ohm direnç Bağlantı kabloları 40 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-7 ARDIŞIK LOJİK DEVRELER-II 7.5 Deney Çalışması 1. 74LS174 IC paketi yardımı ile 6 bitlik register kurunuz. Girişlerine rastgele bilgiler vererek bu bilgileri kayıt etmeye çalışınız. 2. 74LS164 IC paketi yardımı ile 10101010 ve 11110000 seri bilgilerini paralel bilgiye dönüştürünüz. 3. 74Ls165 IC paketi yardımı ile 10101010 ve 11110000 paralel bilgilerini seri bilgiye dönüştürünüz. 4. 4 bitlik shift register devresini JK-FF’lar kullanarak tasarlayınız. 5. 4 bitlik paralel register devresini JK-FF’lar kullanarak tasarlayınız. 7.6 Deney İle İlgili Sorular 1. Şekil 7.3’deki register devresini D tipi flip–floplarla gerçekleştiriniz. 2. 4-bitlik bir shift registerda yüklü bulunan bilgiyi seri olarak başka bir 4-bitlik shift registera aktarılmak istenmektedir. Gerekli devreyi blok şema olarak dönüştürünüz ve transfer işlemlerini adım adım tablo halinde gösteriniz. 7.7 Katalog Bilgisi 1. 74LS164 Katalog bilgileri 2. 74LS165 Katalog bilgisi 3. 74LS174 Katalog bilgisi 4. 74LS194 Katalog bilgisi 41 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-8 ASENKRON SAYICILAR 8.1 Ön Çalışma Deney çalışmasında yapılacak uygulamaların benzetimlerini yaparak, sonuçlarını ön çalışma raporu olarak hazırlayınız. 8.2 Deneyin Amacı Ardışık devrelerden olan sayıcı devrelerin kurulması ve çalışma esaslarının incelenmesi. 8.3 Ön Bilgiler Girişine clock palslarının uygulanması ile durumunu, önceden belirlenen bir sıra dâhilinde değiştiren ardışık devrelere sayıcı (counter) denir. Sayma palsları (count pulses) olarak da bilinen giriş palsları bir clock palsı üretecinden sağlanabildiği gibi, harici başka bir kaynaktan belirli zaman aralıklarında ya da rastgele (random) de sağlanabilir. Sayıcılar dijital lojik devreleri kapsayan hemen hemen her sistemde yaygın olarak görülen devrelerdir. Genel olarak; belirli bir olayın kaç kere oluştuğunun sayılmasında ve dijital sistemlerde işlemlerin kontrol edilmesi için gerekli olan zamanlamanın elde edilmesinde kullanılır. Binary bir sırayı takip eden bir sayıcı; olarak adlandırılır ve N bitlik bir binary sayıcı N adet flipflop’tan oluşur. N bitlik bir binary sayıcı, binary form da 0 (sıfır)’dan 2N-1’e kadar sayar. 3 bitlik bir sayıcının durum diyagramı Şekil 8.1’de görülmektedir. Şekil 8.1 Üç bitlik binary sayıcı için durum diyagramı Şekilden de görüldüğü gibi, daireler sayıcının alabileceği her durumu göstermektedir. Her clock palsı uygulandığında sayıcı şekilde görüldüğü gibi bir sonraki durumu alacaktır. Sayıcı 111 durumunda iken maksimum sayma değerine ulaşmış olacak ve yeni uygulanan clock palsı yardımı ile tekrar 000 durumuna, yani başlangıç sayma durumuna geçmiş olacaktır. MSI (Medium Scale Integration) sayıcılar genel olarak iki grupta ele alınabilirler. Bunlar; RIPPLE sayıcılar SENKRON sayıcılardır. 42 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-8 ASENKRON SAYICILAR 8.3.1 Ripple sayıcılar Bir binary ripple sayıcı T ya da JK flip-flop’ların seri olarak birbirlerine bağlanmasıyla gerçekleştirilir. Şekil 8.2’den de görüldüğü gibi her flip-flop’un en az ağırlıklı (LSB) bit için kullanıldığına dikkat ediniz. Şekil 8.2’de 4-bitlik bir binary ripple sayıcı görülmektedir. Her flipflop’un J ve K girişleri sürekli olarak lojik 1 durumundadır. En az ağırlıklı bit (LSB) için kullanılan ilk flip-flop’a clock palsları uygulanmaktadır. Diğer flip-floplar ise bir önceki flipflop’un Q çıkışı CP olarak kullanılmaktadır. Şekil 8.2 4 Bitlik binary ripple sayıcı Sayma işlemi; clock palslarının alçalan kenarlarıyla ya da clock palslarının 1’den 0’a geçiş anında meydana gelmektedir. Şekil 8.2’de görülen ve asenkron sayıcı olarak da adlandırılabilen ripple sayıcı 0000’dan 1111’e kadar sayan bir yukarı sayıcıdır (Up Counter). Eğer sayıcının çıkışları her FF’un Q çıkışları yerine Q’çıkışlarından alınmış olsaydı, bu sayıcı 1111’den başlayıp 0000’a doğru sayan bir aşağı sayıcı (Down Counter) olacaktı. Aşağı doğru sayan bir sayıcıyı pozitif kenar tetiklemeli FF’larla da gerçekleştirebilirdik. Bu durumda aşağı sayıcının çıkışlarını Q yerine her FF’un Q’ çıkışlarından almamız gerekecekti. Şekil 8.3 BCD ripple sayıcı Sayıcılar 2, 3, 4, 5,… bitlik olabilecekleri gibi istenilen değerlere kadar sayabilecek şekilde de yapılabilir. Örnek olarak Şekil 8.3 bir BCD sayıcıyı göstermektedir. BCD sayıcı 0000’dan 1001’e kadar (0-9) sayan özel bir sayıcıdır. Bu sayıcı 1001 değerine ulaştıktan sonra tekrar 0000 durumuna döner. 43 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-8 ASENKRON SAYICILAR Şekil 8.4 Sayıcının istenilen değere kadar saydırılması Pratik olarak, istenilen n değere kadar sayan ve tekrar 0000 durumuna dönen bir sayıcı şöyle kurulabilir. Şekil 8.4’de görüldüğü gibi istenilen sayma değerine gelindiğinde lojik devre, sayıcının tekrar 0000 durumuna dönmesini sağlayan RESET sinyalini üretecektir. Bu sinyalin üretilmesi ile ve bu sinyalin sayıcıdaki her FF’un CLEAR uçlarına ulaşmasıyla her FF’un çıkışı lojik 0 durumuna gelecek ve başlangıç sayma durumuna geçilmiş olacaktır. 1010’a kadar sayan bir sayıcı için gerekli lojik devre Şekil 8.4’de görülmektedir. 8.3.2 Display etme Herhangi bir binary bilginin anlamlı bir şekilde gözlenebilmesi için 7-parçalı display (Seven segment display) olarak yedi tane LED’in Şekil 8.5’de görüldüğü gibi oluşturulması sonucunda elde edilirler. Ortak anot (Common anode) ve ortak katot (Common cathode) olmak üzere iki ayrı tipi vardır. Bir bilgiyi anlamlı şekilde gösterebilmek için bu bilginin özel bir decoder yardımı ile display’e uygulanması gerekir (Şekil 8.6). Bu decoder; bir binary bilginin display’e nasıl uygulanacağını göstermektedir. Display etme işlemi için Cadet Masterlab üzerinde kod çözücü entegre ve display bağlantısı hazır bulunmaktadır. Bu nedenle deneyler esnasında kod çözücü entegre kullanılmamaktadır. 44 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-8 ASENKRON SAYICILAR Şekil 8.5 7-Segmentli display yapısı Şekil 8.6 Bir binary bilginin display edilmesi 8.4 Deneyde Kullanılacak Cihazlar ve Devre Elemanları CADET Masterlab deney seti 1 adet 74LS20 1 adet 74LS21 2 adet 74LS73 1 adet 74LS90 1 adet 74LS93 Bağlantı Kabloları 45 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-8 ASENKRON SAYICILAR 8.5 Deney Çalışması 1. 74LS73 IC paketleri yardımıyla ripple sayıcıyı kurunuz. Çıkışlarına LED bağlayarak çalışmasını gözleyiniz. 2. 74LS73 IC paketleri yardımıyla kurduğunuz ripple sayıcı desimal on dört (14) değerine kadar sayan ve duran ripple sayıcı olarak düzenleyiniz. Çıkışlarına LED ve DISPLAY bağlayarak çalışmasını gözleyiniz. 3. 74LS90 IC paketi yardımı ile BCD ripple sayıcıyı kurunuz. Çıkışlarına LED bağlayarak çalışmasını gözleyiniz. 4. Yukarıdaki çalışmayı sayıcının çıkışlarını DISPLAY bağlayarak tekrar ediniz. 5. 74LS93 IC paketi yardımıyla 4 bitlik ripple sayıcıyı kurunuz. Çıkışlarına LED, daha sonra DISPLAY bağlayarak çalışmasını inceleyiniz. 6. 74LS93 IC paketi yardımı ile kurduğunuz devreyi 0110’a kadar sayan sayıcı olarak düzenleyiniz. Çalışmasını gözleyiniz. 8.6 Deney İle İlgili Sorular 1. 3 adet BCD ripple sayıcı yardımıyla 0’dan 999’a kadar sayan ve display eden devreyi gerçekleştiriniz. 2. Şekil 8.2’deki ripple sayıcıdaki negatif kenar tetiklemeli FF yerine pozitif kenar tetiklemeli FF kullanılırsa ne olur? Bu durumu inceleyiniz. 3. İleriye ve geriye doğru sayabilen bir sayıcı dizayn ediniz. 4. Ripple sayıcı yardımıyla 21’e kadar sayan bir sayıcı dizayn ediniz. 8.7 Katalog Bilgileri 1.74LS20 Katalog bilgisi 2. 74LS21 Katalog bilgisi 46 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-8 ASENKRON SAYICILAR 3. 74LS73 Katalog bilgisi 4. 74LS90 Katalog bilgisi 5. 74LS93 Katalog bilgisi 47 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-9 SENKRON SAYICILAR 9.1 Ön Çalışma Deney çalışmasında yapılacak uygulamaların benzetimlerini yaparak, sonuçlarını ön çalışma raporu olarak hazırlayınız. 9.2 Deneyin Amacı Sayıcı tiplerinin incelenmesi ve senkron yapıdaki sayıcı devrelerin kurulması. 9.3 Ön Bilgiler 9.3.1 Senkron sayıcı Senkron sayıcıları ripple sayıcılardan ayıran en önemli özellik; Clock palsının senkron sayıcıdaki her flip-flop’a aynı anda uygulanmasıdır. Şekil 9.1’den de görüldüğü gibi senkron sayıcıda her flip-flop’un J ve K girişleri sürekli lojik 1 durumunda değildir. Herhangi bir flip–flop’un J ve K girişlerinin lojik 1 durumuna ne zaman erişeceğini sayacının sayma düzenine göre bir önceki flip-flop’un Q çıkışı tayin etmektedir. Şekil 9.1 4-bitlik senkron sayıcı 9.3.2 Ring sayıcı Ring sayıcılar özel bir sayma tekniğine sahip sayıcılardır. En büyük özellikleri belirli bir değere kadar sayma işleminden sonra tekrar kendiliğinden başa dönmesidir. Temel bir RİNG SAYICI devresi Şekil 9.2’de görülmektedir. 48 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-9 SENKRON SAYICILAR Şekil 9.2 Temel ring sayıcı yapısı Pratikte çok geniş uygulama alanlarına sahip olan bu sayıcı yapısında en ağırlıklı değere sahip olan FF’nun çıkışı en az ağırlıklı değere sahip FF’nun girişine bağlanarak gerçekleştirilir. İstenilen bir değere kadar sayan ve başa dönen bir RİNG SAYICI devresi ise Şekil 9.3’de görülmektedir. Bu yapıda en azından bir FF başlangıçta lojik 1 değerine set edilmiş olmalıdır. Şekil 9.3 Ring sayıcı ile lojik kontrol 9.4 Deneyde Kullanılacak Cihazlar ve Devre Elemanları CADET Masterlab deney seti 2 Adet 74LS74 2 Adet 74LS76 1 Adet 74LS47 1 Adet74LS04 Bağlantı Kabloları 49 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-9 SENKRON SAYICILAR 9.5 Deney Çalışması 1. 74LS76 TC paketleri yardımı ile kurduğumuz devreyi 0110’a kadar sayan sayıcı olarak düzenleyiniz. Çalışmasını gözleyiniz. 2. 74LS74 TC Paketleri yardımıyla 4-bitlik ring sayıcı devresi kurunuz. Çıkışlarına LED bağlayarak çalışmasını gözleyiniz. 3. 5-7-2-4-5-…şeklinde sıralı bir şekilde sayan 3 bitlik bir sayıcıyı JK FF’lar ve gerekli görülürse kapılar kullanarak tasarlayınız. 4. İki bitlik bir sayıcı x girişi ile control edilmektedir. Eğer x = 0 ise sayıcı artan saymaktadır. Eğer x = 1 ise sayıcı azalan saymaktadır. Bu şartları sağlayan devreyi minimum sayıda D FF ve lojik kapılar kullanarak tasarlayınız. 9.6 Deney İle İlgili Sorular 1. Senkron sayıcı kullanarak 1010’a kadar sayan ve sayma işlemini 1010’da durduran bir sayıcı devreyi gerçekleştiriniz. 2. Senkron sayıcı kullanarak 1100’a kadar sayan ve sayma işlemi sonunda tekrar başa dönen bir sayıcı devreyi gerçekleştiriniz. 3. Senkron sayıcı kullanarak desimal on iki (12), yirmi dört (24), altmış (60) değerlerine kadar sayan sayıcı devrelerini dizayn ediniz. 4. 0 ile 24 Saatleri arasını gösterebilecek bir saat devresi dizayn ediniz. 5. 1 KHz’lik bir frekans jeneratöründen 1 Hz’lik bir frekans elde edebilecek devreyi tasarlayınız. 9.7 Katalog Bilgileri 1. 74LS47 Katalog bilgisi 50 Elektrik Elektronik Mühendisliği Bölümü Lojik Devre Laboratuarı DENEY-9 SENKRON SAYICILAR 51