Sayısal Elektronik Devreleri Ödev 1

CMOS Evirici Tasarımı ve LTSpice Yardımı ile Simülasyonu

Orhun Aras Uzun 040080332

1 Giriş

Bu ödevdeki amaç CMOS yapısında bir eviricinin tasarlanmasıdır. Bu eviricinin tasarımı

sırasında dikkat edilmesi gereken hususlar göz önüne alınacak ve böyle bir kapıda optimize

edilmeye çalışılan değerler incelenecektir. Bu incelemenin önemli yanı; evirici kapılarının basit

yapıda olması sayesinde kapıların analizinde kullanılacak metodların incelenmesinde öncü bir yapı

olması ve dikkat edilmesi gereken tasarım kriterlerini barındırmasıdır.

2 Özet

CMOS yapısı diğer MOS'lu ve BJT'li yapılara göre 2 çok önemli avantaja sahiptir bu yüzden

genelde sayısal devreler gerçeklenirken tercih edilirler. İlki; sabit durumda iken neredeyse hiç enerji

harcamamalarıdır. CMOS evirici yapısındaki iki transistör birer ideal olmayan switch olarak

çalışmakta ve gelen girişe göre çıkışı ufak bir direnç üzerinden Vdd'ye veya toprağa kısa devre

etmektedirler. Kısa devre olmuş MOS'un eşleniği açık devre olacağından yukarıdan aşağıya doğru

akım akmaz, bu da CMOS'un durum değiştirmezken enerji harcamamasını sağlar. İkinci avantajı ise

diğer yapılara göre daha ideal bir DC transfer eğrisine sahip olmasıdır. Uygulamalarda sayısal

sistemlerin kullanım amacından ötürü çok ideal bir transfer eğrisi ile gürültüye bağışıklı olmaları

istenir, ayrıca sistem karmaşıklığı arttıkça harcanan güç yoğunluğunun düşürülmesi büyük sıkıntı

olmaktadır.

3 Analiz

CMOS evirici devresinde iki MOS'u da aynı giriş gerilimi sürmektedir. Bu durumda

bunların GS gerilimleri ve DS gerilimleri şu şekilde oluşmaktadır:

Vgsn = Vgiriş

Vdsn = Vçıkış

(1)

Vgsp = Vgiriş – Vdd

Vdsp = Vçıkış – Vdd

Bunlara bakılarak ilk olarak Vgs'lerin belli değerleri için MOS'ların kesim bölgelerinin

incelemesini yapmak kolay olacaktır. Vgiriş, Vt geriliminden küçük olduğu durumlarda nMOS

kesim bölgesinde çalışacaktır. Bu yüzden evirici için yazılan:

Iyukarıdan akan = Iaşağıya giren = 0 (2)

olacaktır. Bu durum oluşmuşken pMOS için bakılırsa Vgsp'nin negatif olduğunu ve Vds'den giriş

gerilimi yükselmedikçe triyot şartının sağlandığı görülür. Bu durumda çıkışta:

Vçıkış = Vdd

(3)

görülür. Bu görülen Vdd değeri aynı zamanda bir devrenin verebileceği maksimum gerilimi de

tanımlar ki bir tasarım kriteri olarak bunun ismi de Voh'dir.

Aynı durumun tersinde yani yüksek giriş gerilimi için nMOS triyot bölgesinde çalışır ve

pMOS kesime girer. Bu durumda da

Vçıkış = 0

(4)

elde edilir. Bu da bu kapının verebileceği minimum gerilim seviyesidir ve Vol olarak gösterilir.

Bir eviriciyi karakterize etmek için gerekli diğer noktaların analizi ise:

Vil: Transfer eğrisinin eğiminin -1 olduğu ayrıca Vgiriş < Vth olan noktadır. Bu noktanın

anlamı girişin lojik 0 olarak algılandığı son nokta olmasıdır. Bu noktadaki çıkış değeri de

beklenildiği gibi yüksek anlamında verilebilecek en düşük gerilimdir, Vohmin.

Bu gerilim değerinin hesaplanması sırasında ilk önce transistörlerin çalışma bölgeleri

dikkate alınmalıdır. Bu bölgede nMOS saturasyon bölgesinde pMOS ise lineer bölgede

çalışmaktadır. 2. denklemde yazdığımız ifadeyi uygun MOS akım bağıntılarını yerine koyarak

yazarsak:

(kn/2) . (Vgsn – Vtn)^2 = (kp/2) . (2*Vds*(Vgsp – Vtp) - Vds^2 ))

(5)

olarak elde edilir. Burada Vgsn = Vil, Vgsp = (Vil – Vdd), Vdsp = (Vdd – Vçıkış) olarak yerine

yazılıp ve dVçıkış / dVgiriş = -1 denklemiyle birlikte çözülürse:

Vil = (2.Vçıkış + Vtp – Vdd + kr . Vtn) / (1 + kr)

(6)

olarak elde edilir. Burada kr = kn/kp 'dir.

Vih: Transfer eğrisinin eğiminin -1 olduğu ve Vgiriş > Vth olan noktadır. Bu noktanın

anlamı ise girişin lojik 1 olarak algılandığı en düşük nokta olmasıdır. Yine aynı şekilde bu noktadaki

çıkış değeri de Volmax olur. Vil hesaplanırken kullanılan denklemleri pMOS saturasyonda ve

nMOS lineer bölgede için çözülürse Vih'nin denklemi elde edilir.

Vih = (Vdd + Vtp + kr.(2*Vçıkış + Vtn)) / (1 + kr)

(7)

Burada yine kr = kn/kp 'dir. Bu 6. ve 7. denklemler ile ilgili dikkat edilmesi gereken nokta ikisinin

de aslında iki bilinmeyen içermesidir. Bu denklemlerin çözülebilmesi için 5. denklem ile birlikte

çözülmeleri gerekmektedir.

Vth: Eviricide bir başka önemli nokta da giriş ile çıkışın eşit olduğu yani ideal eviricinin

geçiş noktasıdır. Eviricinin bu noktadaki karakteri ideal eviriciyle göreceli olarak ne kadar iyi

çalıştığının bir göstergesidir. Bu bölgede iki transistör de saturasyon bölgesinde çalışacaklarından

ötürü ve Vçıkış = Vgiriş de düşünülerek:

(kn/2) . (Vgiriş – Vtn)^2 = (kp/2) . (Vgiriş – Vdd – Vtp)^2

(8)

Olarak yazılabilir denklem. Bu denklemin Vgiriş için çözümünden Vth gerilimi elde edilebilir.

4 Dizayn

Boyut Sınırlamaları:

Bu eviricinin dizaynı sırasında parametreleri önceden verilmiş 0.18um teknolojisi

kullanıldığı için kn ve kp içindeki, 'un', 'up' ve 'Cox' büyüklüklerine müdahele etmek mümkün değil.

Fakat kn ve kp ile oynayarak kritik gerilim değerleri üzerinde değişiklikler yapılabilmekte. Bu

yüzden kp ve kn'yi değiştirmek için W ve L üzerinde oynama yapmak gerekmektedir. Bu değerlerin

getirilmek istendiği nokta ideal eviricinin bulunduğu noktadır ve şöyle tanımlanmıştır:

Vth = Vdd/2

(9)

Bu şart kr denkleminde yerine konulursa; kr'nin 1 olması gerektiği görülür. Bu değerin 1 olması için

p ve n MOS'ların boyutları birbirinden farklı olmalıdır çünkü delik ve elektronların yarıiletken

içindeki mobiliteleri aynı değildir. Bu yüzden eviricide, deliklerin mobilitesi düşük olduğu için,

pMOS'un W'si 2um iken nMOS'un W'si 1um olarak alındı. Bu oranı 1 olan eviriciye simetrik evirici

de denir. Bu durumda eğer kr değeri Vil ve Vih değerlerinde yerine konulup gürültü marjları

hesaplanırsa bunun da simetrik olduğu görülür. Bu da istenen bir özelliktir.

Vdd Seçimi:

Vdd değerinin büyük seçilmesi durumunda gürültüye bağışıklık artacaktır fakat devrede

geçiş bölgelerinde harcanan güç doğrudan Vdd değerine bağlı olduğu için bu durum güç

harcamasını çok yükseltecektir. O yüzden eldeki uygulama için makul değer 1.8V. Düşürülebilecek

en küçük değer ise nMOS ile pMOS'un çalışma bölgelerinin ayrılmaya başlayabileceği değer olan:

Vddmin = Vtn + |Vtp|

değeridir. Bu değerin altında kesim bölgeleri birbirinden ayrılamaz.

Cl Kapasitesi:

MOS yapısı gereği büyük kapasiteler barındırdığı ve geçidinden akım akıtmadığı için

çıkışındaki yükleme etkisi bir kapasite ile betimlenebilir. Tasarlanacak evirici kapasite büyük olsa

dahi yüksek frekanslarda durum değiştirebilmelidir. Bu tasarım sırasında değiştirilebilecek bir

büyüklük değildir, hazırlanan devreden ötürü gelen bir büyüklüktür. Fakat bu ödev dahilinde

yapılan analizde yani transfer eğrisinin çıkarılmasında çok büyük bir rolü yoktur bu kapasitenin. Bu

kapasitenin kaynağı çıkıştan içeri doğru bakıldığında MOS'ların oluşturduğu kapasite, kapıların

birbirine bağlandığı hat üzerindeki kapasite ve bir sonraki kattaki MOS'ların girişinde oluşan

kapasite denebilir.

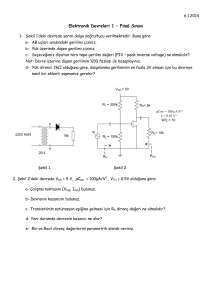

5 Devre Simülasyonu

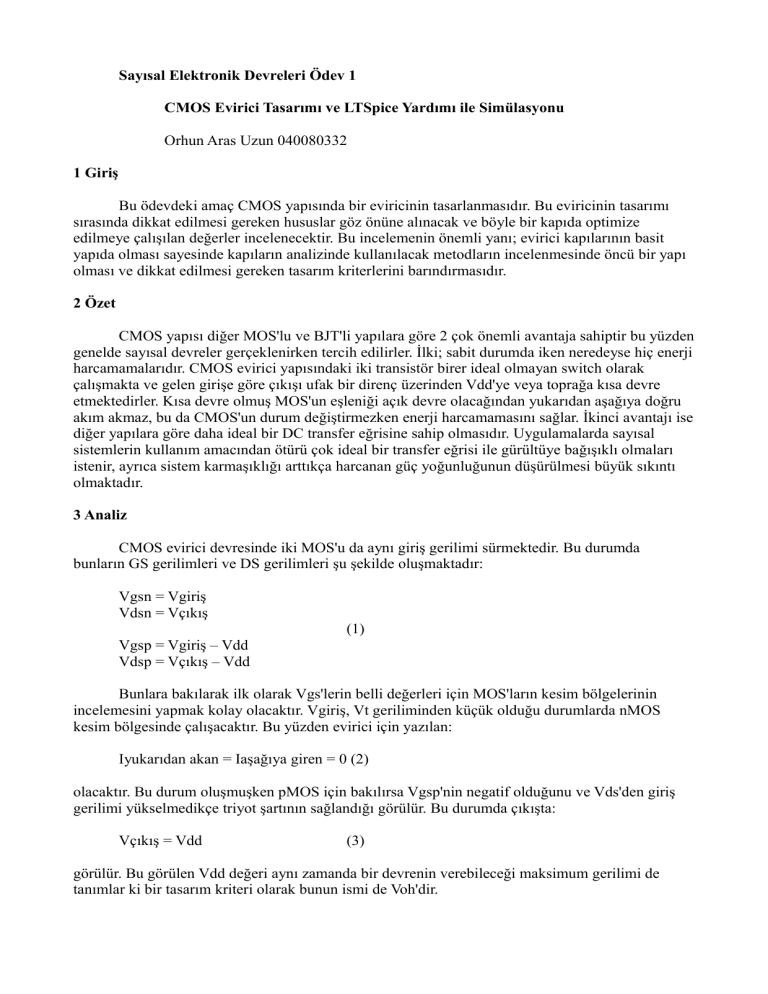

Tasarlanılan eviricinin özelliklerinin incelenmesi için Ltspice simülasyonu yapıldı. Bu işlem

sırasında 0.18um üretim teknolojisi için parametreler kullanıldı. Devrenin son hali şu şekildedir:

Burada sürücü gerilim V2 gerilimidir ve değeri 0V'tan 1.8V'a kadar 0.0001V artışlar ile çıkış

gerilimi gözlendi, transfer eğrisi bulunması için.

Sonuç olarak elde edilen transfer eğrisi ise şu şekildedir:

Burada yeşil eğri ile mavi eğrinin kesişim noktası Vth gerilimidir. Bu gerilimin 826mV olduğu

görülebilir. Bu Vth değeri eviriciyi simetrik kabul etmek için makuldür. Kullanılan yapı CMOS

yapısı olduğu için ve yapılan analiz de DC sweep olduğu için Vol ve Voh değerlerinin Vdd ve 0

olduğu görülebilir.

Ölçümlerden eğimin -1 olduğu noktalardan ilki Vil değerinin 740mV olduğu görülür. Bu durumdaki

çıkış değeri ise yani Vohmin = 1.6V 'dur. Vih değeri ise 880mV olarak bulunur. Volmax ise 180mV

olur.

Bu yapı için gürültü marjı hesabında Voh = Vdd ve Vol = 0 alınabilir. Bu durumda

NML = Vil = 740mV

NMH = Vdd – Vih = 1.8V – 0.88V = 920mV

olarak bulunur. Bu da gösteriyor ki tam anlamıyla simetrik değil imiş.

Sonuç

Bu tasarım sonucunda CMOS eviricinin diğer türlere göre daha ideal bir eğri sağlamasına

rağmen yine de idealden uzak olduğu anlaşıldı ve transfer eğrisinin nasıl bir şekil olduğu, bu eğri

üzerindeki önemli noktaların anlamları öğrenildi.

Referanslar

Steve Kang, Yusuf Leblebici; CMOS Digital Integrated Circuits