bölüm - 4 - DocShare.tips

advertisement

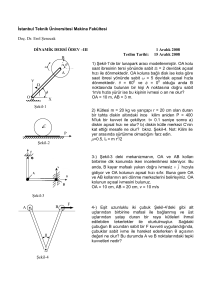

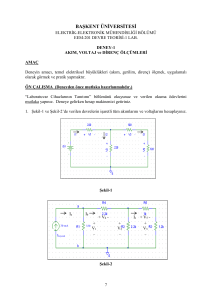

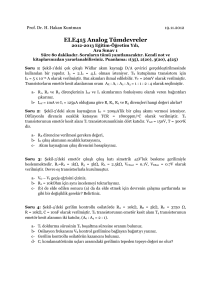

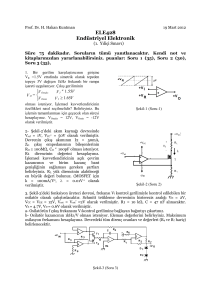

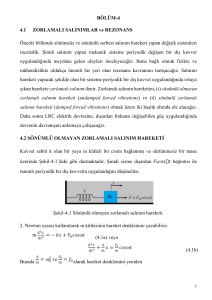

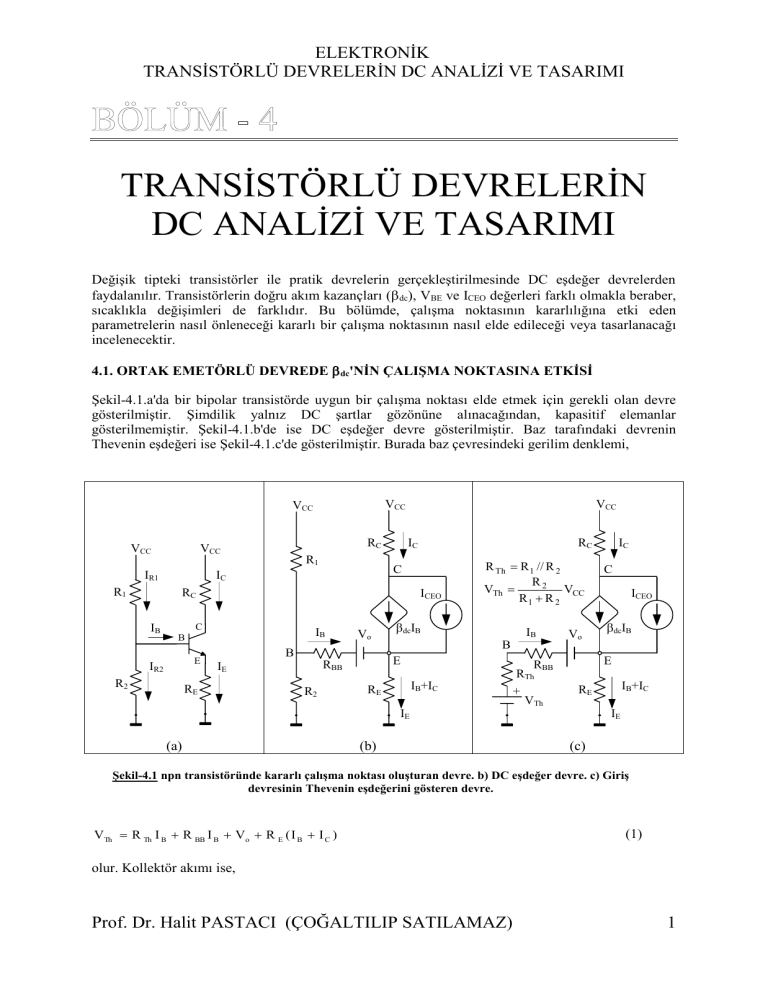

ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI Değişik tipteki transistörler ile pratik devrelerin gerçekleştirilmesinde DC eşdeğer devrelerden faydalanılır. Transistörlerin doğru akım kazançları ( dc), VBE ve ICEO değerleri farklı olmakla beraber, sıcaklıkla değişimleri de farklıdır. Bu bölümde, çalışma noktasının kararlılığına etki eden parametrelerin nasıl önleneceği kararlı bir çalışma noktasının nasıl elde edileceği veya tasarlanacağı incelenecektir. 4.1. ORTAK EMETÖRLÜ DEVREDE dc'NİN ÇALIŞMA NOKTASINA ETKİSİ Şekil-4.1.a'da bir bipolar transistörde uygun bir çalışma noktası elde etmek için gerekli olan devre gösterilmiştir. Şimdilik yalnız DC şartlar gözönüne alınacağından, kapasitif elemanlar gösterilmemiştir. Şekil-4.1.b'de ise DC eşdeğer devre gösterilmiştir. Baz tarafındaki devrenin Thevenin eşdeğeri ise Şekil-4.1.c'de gösterilmiştir. Burada baz çevresindeki gerilim denklemi, VCC VCC VCC R1 IR1 R1 IC RC VCC VCC C IC RC IB ICEO C IB B E IR2 R2 Vo B RE R2 R Th R 1 // R 2 R2 VTh VCC R1 R 2 dcIB IB B E RBB IE IB+IC RE RBB RTh + VTh Vo (b) C ICEO dcIB E IB+IC RE IE (a) IC RC IE (c) Şekil-4.1 npn transistöründe kararlı çalışma noktası oluşturan devre. b) DC eşdeğer devre. c) Giriş devresinin Thevenin eşdeğerini gösteren devre. VTh R Th I B R BB I B Vo R E ( I B I C ) (1) olur. Kollektör akımı ise, Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 1 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI I C dc I B I CEO veya, IB 1 dc IC 1 dc (2) I CEO olur. (2) eşitliğini (1)'de yerleştirirsek, V Th ( R Th R E )( 1 IC dc 1 dc I CEO ) R E I C V o elde edilir. Burada, R Th R BB R Th 'dir. Bu denklemden IC çözülürse, IC dc ( VTh Vo ) ( R Th R E ) I CEO R Th ( dc 1) R E (3) bulunur. dc 'nin etkisini görebilmek için küçük değerli olan ICEO'u ihmal edelim. IC dc ( V Th V o ) R Th ( dc 1) R E , ( I CEO 0 ) (4) Eğer RE, ( dc 1) R E R Th olacak şekilde seçilecek ise, IC dc V Th V o dc 1 RE dc V Th V o RE (5 olur. dc dc dc 1 olduğundan, IC akımı dc′ye pek bağlı değildir. dc, 1/3 oranında değişse dahi dc 'deki değişme %1'den küçük olur. Çalışma noktasının belirlenmesi için IC, VCE, IB ve VBE değerlerinin herhangi ikisinin belirlenmesi yeterlidir. Genellikle (IC, VCE) çifti çalışma noktası için kullanılır. Şekil-4.1.a'da kollektör-emetör çevresi için gerilim denklemi yazılırsa, VCE VCC R C I C R E I E (6) olur. Burada IC akımı sabit ve IE ≈ IC olduğundan, VCE'de sabit olur. Yani, çalışma noktasının sabit olması için IC'nin sabit kalması gerekir. Sabit bir çalışma noktası için (5) ve (6) eşitlikleri kullanılabilir. Gerektiği hallerde (3) ve (6) numaralı gerçek formüller kullanılacaktır. Şekil-4.1.a'daki devrenin gerçekleşmesi için dört direnç ile kaynak geriliminin belirlenmesi gerekir. Şimdilik çalıma noktasının (IC ve VCE) verildiğini kabul edelim. İlk tasarım için aşağıdaki kabuller yapılabilir. 1. VCC 'nin değeri VCE 'nin 3 veya 5 katı, 2. RE uçlarındaki gerilim VCE ''ye eşit veya biraz küçük, Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 2 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI 3. R1'deki akım IB akımının 10 ile 100 katı arasında. Bu kabulleri 25˚C 'deki çalışma noktası, IC=1mA ve VCE=5V olan 2N5377 transistörü için uygulayalım. Bu transistöre ait bir katalog sayfası Şekil-4.2'de gösterilmiştir. Görüldüğü gibi bu transistör npn tipi silisyum transistörüdür. IC=1mA için dc'nin değeri hFE ile gösterilmiştir. hFE 'nin değeri 100 ile 500 arasındadır. Ayrıca, ICBO(max)=10nA olduğu ve ICEO, 101 ile 501 defa büyük olacağı anlaşılmaktadır. ICEO 'nun değeri 1 ile 5 mA mertebesindedir. Bu değer, IE veya IC'nin yanında çok küçük olduğundan ihmal edilebilir. Buradaki önemli problem dc 'nin çok geniş aralıkta değişmesidir. Bu değişimi önlemek için IC'nin sabit tutulması gerekir. Yukarıda açıklanmış olan üç kurala göre devre elemanlarını seçelim: VCC, VCE 'nin 5 katı olsun. VCC = 5V CE = 25V RE'deki gerilim VCE 'ye eşit olsun. VRE=VCE =5V. R1'deki akım, IB'nin 50 katı olsun. En kötü transistör için dc=100 ise IB=10-3/100=10µA olur. Buradan, I R 1 50 (10 x10 6 ) 500 A bulunur. Kollektör tarafındaki gerilim denkleminden, V R C V CC V R E 25 5 5 15 V VR C RC IC R E1 15 15 k 1 VR E VR E IE IC 5 5k (7) 1 değerleri bulunur. R2 direnci üzerinden IR1-IB=500-10=490µA'lik akım akar. Gerilim düşümü ise VBE+VRE=Vo+RBBIB+VRE'dir. 2N5377 transistörünün baz doyma gerilimi VBE(sat)=0.65 ile 0.8V arasındadır. Akan baz akımı 10µA gibi küçük bir değer oluduğundan Vo=VBE(sat)=0.65V seçilebilir. RBB direnci ihmal edilirse, VR2=0.65+5=5.65V olur. R2 R1 V R E Vo IR1 IB V CC V R 2 IR1 5 . 65 V 0 . 49 mA 11 . 5 k 25 5 . 65 0 .5 38 . 7 k Burada, arzu edilen çözüm tamamlanmıştır. dc=500 alınarak sonuçların kontrol edilmesi gerekir. Vo=0.65V ve RBB=0 kabulu ile Şekil-4.1c'deki devreyi gözönüne alalım. Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 3 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI R Th VTh R 1R 2 R1 R 2 R2 R1 R 2 38 . 7 x11 . 5 38 . 7 11 . 5 VCC 8 . 88 k 11 . 5 38 . 7 11 . 5 x 25 5 . 74 k (3) numaralı eşitlikten, IC IC dc ( VTh Vo ) ( R Th R E ) I CEO R Th ( dc 1) R E 500 x ( 5 . 74 0 . 65 ) ( 8 . 88 5 ) x 501 x 10 88 . 8 ( 501 ) x 5 5 2545 0 . 07 1 . 012 mA 2514 Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 4 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI Şekil gelecek Şekil-4.2 2N5377 transistörüne ait katalog sayfası gösterilmiştir. IC=1mA ve VCE=5V olup dc=hFE ,100 ile 500 arasında değişmektedir. bulunur. Bu değer daha önce seçtiğimiz 1mA'lik değere çok yakındır. Kollektör - emetör gerilimi ise, VCE VCE R C I C R E ( I C I B ) 25 15 x (1 . 012 ) 5 x (1 . 012 0 . 002 ) 25 15 x 18 5 . 07 4 . 75 V olup, çalışma noktası aktif bölgede kalmaktadır. Eğer dc=100 için benzer işlemler yapılırsa, IC=0.990mA ve VCE=5.14V değerleri bulunur. Görüldüğü gibi bütün sonuçlar seçilen (1mA, 5V) 'luk çalışma noktasına çok yakındır. Yani dc'nin geniş bir aralıkta değişmesine rağmen çalışma noktası yaklaşık sabit kalmaktadır. Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 5 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI dc'nin geniş bir değişim aralığında çalışma noktasının sabit kalması, negatif bir geribeslemenin var olduğunu gösterir. Şekil-4.1.a'daki devrede R1'deki akımın IB baz akımından çok büyük olduğu düşünülürse, VR2 gerilimi IB 'den bağımsız olur. IC akımındaki herhangi bir artma VRE'nin artmasına neden olur. Neticede, (VR2- VRE) farkı azalarak IB'nin azalmasına ve IC= dcIB'nin de azalmasına neden olur. Yani, devre IC 'nin değişimine ters bir etki oluşturur. IC 'nin azalması durumunda da VRE küçülür, (VR2- VRE) farkı büyür, IB ve IC= dcIB artarak IC 'nin orijinal değerine düşmesi sağlanır. Burada, geribeslemeyi oluşturan RE direnci olup, bunun değeri arttıkça geribesleme miktarı da artar. RE büyüdükçe kararlılık artması rağmen kazanç azalır. Kazancın azalmasına önlemek için RE direncine paralel bir köprüleme kapasitesi konur. Eğer, VCC=9V için IC=10µA ve VCE=5V olarak seçilmiş ise Şekil-4.2'deki verilerden, dc(min)=40 olur. VBE=0.6V ise, IB 6 10 x10 0 . 25 A 40 ve I E 10 . 25 A olur. VCE=5V ve VCC=9V olduğundan, RC ve RE dirençleri üzerindeki toplam gerilim düşümü 4V olur. Herbirinde 2V'luk gerilim düşümü varsa, RE RC 2 10 . 25 x 10 2 10 x 10 6 195 . 1k 200 k 6 olur. IR1=200IB seçilirse, IR1=200x0.25x10-6=50µA olur. IR2=IR1-IB=49.75µA olur. Vo=VBE(min)=0.6V ile, VR 2 VRE Vo 2 . 6 V R2 2 .6 49 . 75 x 10 6 52 . 3 k VR 1 9 2 .6 6 .4 V R1 6 .4 50 x 10 6 128 k değerleri bulunur. Thevenin gerilim ve direnci ise VTh=2.61V, RTh=37.1kΩ olur. dc(min=40 ve dc(max)=200 için sonuçlar karşılaştırılırsa, dc(min=40 dc(max)=200 C=(40+1)10x10-9=410µA C=2.01µA Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 6 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI IC=10.02µA IC=10.25µA IB=(IC-IB)/ dc=0.24µA IB=0.0412µA IE=-10.26µA IE=-10.29µA VCE=4.99V VCE=4.94V olur. Görüldüğü gibi çalışma noktası her iki halde de aktif bölgede kalmakta ve birbirine çok yakın olmaktadır. Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 7 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI 4.2. ORTAK EMETÖRLÜ DEVREDE SICAKLIĞIN ÇALIŞMA NOKTASINA ETKİSİ Önceki kısımda dc'nin çalışma noktasına etkisi incelendi. Burada ise sıcaklığın etkisi incelenecektir. Elektronik devre elemanları -55˚C ile 125˚C arasındaki sıcaklıklarda çalışmaları sözkonusu olabilir. Sıcaklığın diyot ve transistör üzerindeki etkisi çok fazladır. VBE gerilimi her 1˚C sıcaklık artışında 1.8 ile 2.5mV azalır. Ortalama olarak 2.3mV/˚C alınabilir. ICEO akımı da her 10˚C'de yaklaşık iki kat artar. Matematiksel olarak bu bağımlılık, I CEO KT e 3 E G / kT ( dc 1) şeklindedir. Burada; K - bir sabit, EG=1.12eV (1eV=1 elektron volt=1.6022x10-19J), k - Boltzman sabiti ve T - Kelvin sıcaklığıdır. dc katsayısı da sıcaklıkla nonlineer olarak artar. Bir silisyum transistöründe sıcaklığın en çok etki ettiği büyüklükler; VBE ve dc'dir. ICEO tıkama akımı, IC yanında çok küçük olduğundan bunun sıcaklıkla değişimi ihmal edilebilir. Fakat, bazı entegre devrelerde ICEO etkilidir. Belirtilen bu etkilere karşı çalışma noktasını sabit tutabilmek için burada da emetör akımının sabit kalmasına çalışılacaktır. Emetör direnci üzerinden oluşacak olan negatif geribesleme, dc ve VBE 'deki değişimleri önleyecektir. VBE 'nin kararlılığı Şekil-4.1.c'deki eşdeğer devrede gösterilmiş olan VTh 'nin büyük olması ile artar. (4) Eşitliğini tekrar gözönüne alalım. IC dc ( V Th V o ) R Th (1 dc ) R E I CEO 0 ) Burada, Vo gerilimi seçilen modeldeki VBE gerilimine eşittir. Görüldüğü gibi IC'deki değişim, (VThVo) gerilim farkı ile orantılıdır. VTh 'i büyük seçerek VBE= Vo 'daki değişim minimum yapılabilir. ICEO 'daki değişimin etkisi (3) eşitliğinde açıkça gözükmektedir. Bunu aşağıdaki gibi düzenleyelim. IC IC dc ( V Th V o ) R Th (1 dc ) R E ( R Th R E ) I CEO R Th (1 dc ) R E (8) ICEO 'ya göre türev alınırsa, IC I CEO dI C dI CEO ( R Th R E ) R Th (1 dc ) R E olur. (9) Bu oranın küçülmesi için dc R E ( R Th R E ) yapılmalıdır. Hatırlanacağı üzere RBB direnci RTh 'e göre çok küçük olup, bunun içinde olduğu kabul edilmişti. Devre tasarımı yapılırken en kötü durum gözönüne alınmalıdır. Mesela (4) eşitliğinde IC akımının minimum olması için Vo 'ın maksimum ve dc 'nin minimum olması gerekir. Bu durum sıcaklığın minimum olması ile sağlanabilir. Bunu aşağıdaki gibi yazabiliriz. Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 8 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI I C (min) dc (min) ( VTh Vo (max) ) (10) R Th (1 dc (min) ) R E Maksimum kollektör akımı I(max) ise maksimum sıcaklıkta ortaya çıkmaktadır. Bu durumda Vo minimum ve dc maksimumdur. Böylece, I C (max) dc (max) ( VTh Vo (min) ) elde edilir. R Th (1 dc (max) ) R E (11) Uygulama için kısım 4.1 'deki örneği tekrar gözönüne alalım. Bu örnekte, 2N5377 transistörü için (VCE=5V, IC=1mA) çalışma noktası gözönüne alınmıştı. Burada bu çalışma noktasının -55 ile +125˚C 'ler arasında IC 'de ±%10 'luk bir değişme olacak şekilde devre tasarımı yapılacaktır. dc 'nin -55˚C 'deki değeri 25˚C 'dekinin 0.8 ve 125˚C 'de 1.4 katı kadar olduğunu kabul edeceğiz. dc (min) 0 . 8 (100 ) 80 (minimum değer) dc (min) 1 . 4 ( 500 ) 700 (maksimum değer) Vo 'ın minimum ve maksimum değerlerini bulmak için Vo (25˚C)=0.65V ve her 1˚C 'ta 2.3mV azaldığı kabul edilerek hesaplanır. Vo Vo ( 215 C ) 2 . 3 x 10 o 3 ( T C 25 C ) o o V o (min) 0 . 65 2 . 3 x 10 3 (125 25 ) 0 . 42 V V o (max) 0 . 65 2 . 3 x 10 3 ( 55 25 ) 0 . 834 V Burada da benzer tasarım işlemleri yapılabilir. Mesela, V RE 5 V , I R 50 I B R 1 38 . 7 k , R 2 11 . 53 k , R E 5 k , R C 15 k R Th 8 . 88 k , V Th 5 . 74 V olur. Bundan sonra en kötü iki durumun kontrol edilmesi gerekir. IC(min) ve IC(max) değerleri, I C (min) I C (max) 80 ( 5 . 74 0 . 834 ) 8 . 88 ( 81 ) x 5 0 . 948 mA 700 ( 5 . 74 0 . 420 ) 8 . 88 ( 701 ) x 5 1 . 060 mA olur. ±%10 sınırları içinde kalındığından başarılı bir tasarım yapılmıştır. Eğer ±%10 sınırları içinde kalınmaz ise RTh azaltılıp RE arttırılır. RTh veya R1 ile R2 'nin ne kadar büyük olacağı konusu bir sonraki kısımda incelenecektir. Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 9 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI 4.3. ÇEVRE VE JONKSİYON SICAKLIĞI Diyot ve transistör üzerinde oluşabilecek maksimum güç kaybı, jonksiyon tarafından belirlenir. Jonksiyon sıcaklığı yarıiletken malzemenin tipine ve imalat tekniğine bağlıdır. Germanyum transistör veya diyotundaki maksimum jonksiyon sıcaklığı 90˚C ile 110˚C arasında iken, silisyum transistör veya diyotunda ise 135˚C ile 200˚C arasındadır. 2N5377 transistöründe maksimum jonksiyon sıcaklığı 150˚C iken, Şekil-4.3 'teki 2N5088 transistöründe 135˚C 'dir. Şekil gelecek Şekil-4.3. 2N5088 transistörüne ait bazı katalog bilgileri Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 10 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI Transistörde harcanacak ısı miktarı, ısının etrafa yayılma hızını belirten ısıl dirence bağlıdır. Eğer iki nokta arasındaki sıcaklık farkı ∆T, bu ortamın ısıl direnci ve burada harcanan güç PD ise bunlar arasında, T PD (13) bağıntısı yazılabilir. Bu bağıntı ohm kanununa (V=RI) benzer. 'nın küçük olması, ısı yayılımının daha hızlı olacağını gösterir. Isıl direnci küçültmek ve transistör üzerindeki ısıyı etrafa yaymak gayesi ile geniş yüzeyli soğutucular kullanılır. Yarıiletken jonksiyonu ile dış ortam arasındaki ısıl devreyi Şekil-4.4 'teki gibi modelleyebiliriz. Buradaki indisler sırası ile; J- jonksiyonu, C-yarıiletken elemanın kılıfını (metal veya plastik), S-soğutucuyu ve A-atmosferi göstermektedir. Buradaki ısıl çevre denklemi ise aşağıdaki gibi olur. TC TJ JC TS CS SA PD TA TA Şekil-4.4 Yarıiletken jonksiyonu ile dış ortam arasındaki termal devre lineer direnç devresinin analoğudur. TJ TA ( JC CS SA ) PD (14) Soğutucunun bulunmaması durumunda, TJ TA ( JC CA ) PD olur. (15) Örnek olarak ortam sıcaklığının 75˚C olması halinde 2N5088 transistöründe harcanabilecek maksimum gücü bulalım. Katalogtan; 25˚C'de harcanabilecek maksimum güç 310mW, jonksiyon ile dış ortam arasındaki ısıl direnç JA=0.357˚C/mW (357˚C/W) ve maksimum jonksiyon sıcaklığı 135˚C 'dir. T=TJ-TA=135-75=60˚C olup, (13) eşitliğinden, PD T JA 60 0 . 357 168 mW olur. Görüldüğü gibi ortam sıcaklığı arttıkça, harcanabilecek maksimum güç azalmaktadır. Başka bir örnek olarak, ortam sıcaklığı 25˚C ve çalışma noktası (IC=2mA, VCE=20V) olan 2N5088 transistöründeki jonksiyon sıcaklığını bulmaya çalışalım: Burada sözü edilen jonksiyon kollektör - baz jonksiyonudur. Dolayısı ile kollektör - baz gerilimini bulmak gerekir. VBE=0.7V olduğuna göre, VCB 20 0 . 7 19 . 3 V ve PD I C VCB 2 x19 . 3 38 . 6 mW olur. VCB gerilimi yerine VCE gerilimi kullanılırsa, küçük bir fark olur. Yani PD=ICVCE=2x20=40mW 'tır. Isıl eşdeğer devreden, Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 11 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI T JA PD 0 . 357 x 38 . 6 13 . 8 C o elde edilir. Ortam sıcaklığı TA=38.8˚C olur. Bu değer, 135˚C 'lik üst limite göre oldukça iyi bir değerdir. PD PDmax 0 TJmax TCo Jonksiyon sıcaklığı Şekil-4.5 Bir yarıiletken elemanın güç eğrisi, güç kaybı ile sıcaklık arasındaki değişimi gösterir. Bunun çizimi için maksimum güç kaybı, ortam veya kılıf sıcaklığı ve maksimum jonksiyon sıcaklığının belli olması gerekir. Yarıiletken ısıl büyüklüklerin hesaplanmasında Şekil-4.5 'te gösterilen güç eğrisinden de faydalanılır. Bu eğri maksimum güç kaybı, maksimum jonksiyon sıcaklığı ve bir referans sıcaklığından faydalanarak çizilir. Mesela 2N5088 'in kataloğundan, PD(max)=310mW köşe noktasına ait referans sıcaklık TCo=25˚C ve TJ(max)=135˚C 'dir. Ortam sıcaklığının 25≤TA≤135˚C arasındaki değerleri için, 135 C TA PD o 135 25 310 0 0 . 355 PD JA PD elde edilir. Bir defa daha görüleceği üzere PD 'nin katsayısı yani, eğimi 0.355˚C/mW olup, katalogtaki 0.357˚C/mW 'a çok yakındır. Şekil-4.6'da RCA 2N2015 npn tipi güç transistörü için bir güç eğrisi çizilmiştir. Bu eğriden; T C≤25˚C sıcaklıklarda transistör üzerinde 150W 'lık güç kaybı oluşur. Eğer atmosfer sıcaklığı yerine kılıf sıcaklığı verilirse eğri eğimi JA1 'ye eşit olur. Kılıf sıcaklığı, transistör veya diyotun soğutulması için kullanılan soğutucunun sıcaklığı ile aynı olur. Eğer ortam sıcaklığı 25˚C ve ortam ile kılıf arasındaki ısıl direnç (yani soğutucunun ısıl direnci) 0.5˚C/W ve güç kaybı P=150W ise, TC TA 0 . 5 x 150 75 C bağıntısından TC 75 C olur. o o Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 12 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI PD PDmax 150W TC(ºC) 0 TJmax Jonksiyon 200ºC sıcaklığı TCo 25ºC Şekil-4.6 2N2015 güç transistörünün TC=25˚C 'lik kılıf sıcaklığına bağlı olarak güç eğrisi. Burada JC=175/150=1.17˚C/W 'tır. Güç eğrisinin direnci JC 7 / 6 o C / W olduğundan, TJ TC ( 7 / 6 ) x150 175 C bağıntısından TJ 275 C olur. o o Bu sıcaklık müsaade edilen jonksiyon sıcaklığından [TJ(max)] fazla olduğundan transistör bozulur. 4.4. ORTAK KOLLEKTÖRLÜ VE ORTAK BAZLI DEVRELER Daha önceki kısımlarda ortak emetörlü devreler incelendi ve çalışma noktasının kararlılığı için emetör akımının sabit kalması gerektiği sonucuna varıldı. Ortak emetörlü devre için çizilen devreler ile oldukça kararlı çalışma noktaları elde edilmektedir. Benzer devreler, az kullanılan ortak kollektör ve ortak bazlı için de kullanılır (Şekil-4.7, 4.8). R1 IR1 IC + C IB Giriş VCC B E R2 IR2 RE Çıkış IE Şekil-4.7 npn tipi bir transistörün ortak kollektörlü devresi. Bu devre ortak emetörlü devrede R C=0 yapılarak elde edilir. Ortak bazlı devre ise Şekil-4.8 'de gösterilmiştir. Bu devre Şekil-4.1.a 'daki ortak emetörlü devrenin aynısıdır. R2 direncine paralel bağlanan büyük değerli bir kapasite ile baz ucu değişken işaretler için kısa devre edilmiş olur. Buna köprüleme (by-pass) kapasitesi denir. Ortak emetörlü devrede köprüleme kapasitesi RE 'ye paraleldir. Ortak kollektörlü devrede değişken işaretler için kollektör ucu giriş ve çıkışta ortaktır. Şekil-4.7 'de gösterildiği gibi kollektör ucu VCC kaynağına bağlıdır. Yani, kollektör ile toprak arasında herhangi bir Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 13 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI değişken işaret sözkonusu değildir. Bu devre, Şekil-4.1.a 'daki ortak emetörlü devrede RC=0 yapılarak elde edilir. Tasarım ve analiz işlemleri birbirinin aynıdır. E Giriş IE IB C B Çıkış IC R1 RE RC + IR1 R2 VCC IR2 Şekil-4.8 Orkak bazlı bir devre. Şekil-4.1a'daki devrenin benzeridir. Bu devrenin tasarım ve analizi ortak emetörlü devredeki gibi olur. 4.5. ENTEGRE DEVRELERDEKİ ÇALIŞMA NOKTASI Entegre devrelerdeki transistörlerin çalışma noktaları ayrık transistörlerdeki çalışma noktalarından çok farklı bir teknik ile gerçekleştirilir. Bunun temel nedeni; entegre devre dirençlerinin çok fazla yer kaplamaları ve buna bağlı olarak maliyetin yüksek olmasıdır. Bundan dolayı entegre devrelerde direnç olarak diyot ve transistör gibi aktif yükler kullanılır. Zorunlu olarak kullanılacak olan dirençlerin değerleri küçük seçilir. Entegre devrelerde benzer elemanların aynı anda yapılması büyük bir üstünlüktür. Ayrıca, elemanlar çok küçük hacimlere (mm'den küçük) yerleştirildiği için hepsi aynı çevre şartları altındadır. Bundan dolayı farklı devrelerdeki RBB, dc, VBE ve ICEO büyüklükleri birbirine çok yakındır. Entegre devrelerde (IC) emetör akımını veya çalışma noktasının kararlılığı genel olarak ayrık elemanlarda olduğu gibi olur. Yalnız burada emetör akımının sabit tutulma metodu biraz farklıdır. Bunu açıklamak gayesi ile Şekil-4.9.a 'daki entegre devre diyotunu göz önüne alalım. Bir entegre devre diyotu, bipolar bir transistörün kollektörü ile bazının kısa devre edilmesinden meydana gelir. VCB=0 olduğundan çalışma bölgesi, aktif ve doyma bölgelerinin sınırlıdır. Bundan dolayı Şekil-4.9.b 'deki aktif bölge eşdeğerini göz önüne alabiliriz. Buna göre ID diyot akımı, I D I B dc I B (1 dc ) I B olur, (16) Bu akım emetör akımına eşittir (ID=IE). Diyot gerilimi ise, VD I B R BB Vo Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 14 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI ID ID + ID dcIB IB E - - VD + VD VBE=VD Ro + C B + C VD + - E RBB VBE=VD (a) + Vo Vo B ID R BB (1 β dc ) - - ID (c) (b) Şekil-4.9 a) Bir yongadaki transistörün kollektör ve bazının kısa devre edilmesi ile bir entegre diyot oluşur. b) VBE=VD≥0 için lineer eşdeğer devresi. c) Basit eşdeğer devre. VD I D R BB (1 dc ) Vo olur. Bu son eşitlikten Şekil-4.9.c 'deki devre çizilebilir. Buradaki Ro direnci aşağıdaki gibi yazılabilir: Ro R BB (17) (1 dc ) Görüldüğü gibi bir transistörün kollektörü ile bazı kısa devre edilirse bir diyot oluşur. Bu diyotun akımı, transistörün emetör akımına eşittir. Şekil-4.10 'da entegre yardımı ile bir transistördeki çalışma noktasının nasıl gerçeklendiği gösterilmiştir. VCC VCC IC RC I1 R1 + VCC dcIB VCC IB R1 I1 VD Vo - RC IC VD RBB ID + Ro E R BB (1 β dc ) - ID + Vo - (a) Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) (b) 15 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI Şekil-4.10 a) Soldaki transistör bir entegre diyot gibi bağlanarak sağdaki transistörde belirli bir I C akımının akmasını sağlamaktadır. b) Her iki transistörün aktif bölgedeki eşdeğer devreleri gösterilmiştir. Şekil-4.10.b 'de ise toplam devrenin DC eşdeğeri çizilmiştir. Sağdaki transistörün aktif bölgede olduğu kabul edilmiştir. Eşdeğer devreden, I D 1 I D I B 2 olur. (16) eşitliği de kullanılarak ID akımı yok edilirse, I1 I B1 (1 dc ) I B 2 olur. Her iki transistörün baz-emetör gerilimleri eşit olduğundan, baz akımları da eşittir (IB1=IB2). Böylece, IB I1 2 dc olur. Sabit kalmasını istediğimiz kollektör akımı ise I C dc I B 2 dc I B olup, IC dc 2 dc I1 Şeklinde yazılabilir. dc >>1 olduğundan IC=I1 'dir. Eğer I1 sabit ise IC akımı veya çalışma noktası kararlı olmuş olur. Şekil-4.10.b 'den, VCC R 1 I1 VD veya I 1 V CC V D elde edilir. R1 Entegre devre diyotun VD gerilimi yaklaşık olarak 0.65V civarındadır. Bu değerde 0.1V 'tan büyük bir değişme olamaz. VCC ise 0.65V 'tan çok büyük bir değerdir. Böylece, eğer VCC kaynak gerilimi sabit ise (VCC- VD) farkı da sabit olduğu kabul edilebilir. Anlaşılacağı üzere, çalışma noktasının kararlılığı güç kaynağının regülasyonuna bağlı olmuş olur. Sonuç olarak; IC 'nin sabit olması için I1'in sabit tutulması gerekir. I1= IC eşitliğini sağlayan bu devreye akım aynası veya sabit akım kaynağı devresi adı verilir. Böylece bir entegre diyot akımı ile birkaç transistörün kollektör akımını sabit tutmak mümkündür. Herbir transistörün kollektör akım I1 'e eşit olur. bu entegre diyot sabit bir akım kaynağı oluşturmaktadır. Herhangi bir devre için sabit akım gerektiğinde, bu devreyi RC ile seri bağlamak gerekir. Bu sabit akım kaynağı, lineer entegre devre tasarımının temel birimini oluşturmaktadır. 4.6. JFET VE KANAL AYARLAMALI MOSFET'İN ÇALIMAS NOKTASI Bu bölümde, FET 'lerin kararlı çalışma noktasının nasıl elde edildiği konusu anlatılacaktır. Daha önceki bölümlerde FET'lerle ilgili bazı devrelerin DC analizi yapıldı. Şekil-3.13'teki örnekte çalışma noktasına ait VGS, ID ve VDS büyüklüklerinin belirlenmesi için lineer olmayan devre modeli kullanıldı. p-kanallı FET'e ait devrenin benzer analizi Şekil-3.14.a'daki devrede gözönüne alındı. Transistör dışındaki devre elemanlarının hesaplanması için IDSS ve VP büyüklüklerinin doğru bilinmesi ve kararlı olmaları gerekir. Bipolar transistörde görüldüğü gibi aynı elemanlar arasındaki Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 16 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI imalat farklılıkları, sıcaklık ve bu ikisinin toplam etkisi çalışma noktasının kararlılığını çok değiştirmektedir. JFET parametrelerindeki en büyük farklılık, IDSS doyma akımı ile VP boğulma gerilimlerinde gözükmektedir. Aslında bu iki parametre doyma bölgesindeki lineer olmayan transfer eğrisinin belirlenmesinde gereklidir. Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 17 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI Şekil gelecek Şekil-4.11. 2N3823 transistörüne ait bir katalog sayfası. Sıcaklık arttıkça IDSS azalmasına rağmen, VP gerilimi pek etkilenmemektedir. İmalat teknikleri arasındaki farklar bu iki parametreye çok etki etmektedir. IDSS akımı kanal genişliği ile orantılı iken, Vp gerilimi kanal genişliğinin karesi ile orantılıdır. Şekil-4.11'de 2N3823 numaralı n-kanallı JFET'in bir katalog sayfası gösterilmiştir. Burada, VGS=0V için IDSS akımı 4mA'den 20mA'e kadar değişirken, ID=400µA=0.4mA'lik bir akım için VGS =-1V ile -7.5V arasında değerler almalıdır. VP boğulma gerilimi -7.5V'tan biraz daha negatiftir. Eğer, IDSS=20mA ve VGS=-7.5V olduğunda ID=0.4mA ise, ID I DSS V 2 P ( VGS V P ) 2 20 2 VP ( 7 .5 VP ) 2 bağıntısından, V P 8 . 74 V bulunur. Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 18 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI Akımların alt sınırları için VP =-1.46V bulunur. Dolayısı ile VP gerilimi; -1.46 ile -8.74V arasında bir değerdir. Yani, büyük IDSS akımı için daha negatif boğulma gerilimi gereklidir. Görüldüğü gibi V P gerilimi büyük bir toleransa sahiptir. IDSS 'in maksimum ve minimumu değerleri için 2N3823 transistörünün transfer karakteristiği Şekil-4.12'de gösterilmiştir. ID(mA) IDSS= 20 15 VDS³(VGS-VP) 10 5 -10 -8 -6 -4 -2 VGS(V) Şekil-4.12 2N3823 transistörünün maksimum ve minimum I DSS akımlarına ait transfer karakteristikleri. Karakteristiği geniş bir değişim aralığına sahip olan böyle bir transistörde sabit ve kararlı çalışma uygun bir kutuplama devresi ile sağlanır. Şekil-4.13.a'daki sabit kutuplama devresini gözönüne alalım. Burada negatif kaynak kapıya, pozitif kaynak kollektöre uygulanmıştır. Bu devre ile Şekil4.13.b'deki çalışma noktaları elde edilir. Bunlardan biri; IDSS=20mA, VP=-8.74V ve ID=11.9mA ve değeri ise; IDSS=4mA, VP=-1.46V ve ID=0'dır. Eğer, VGS=-1V yapılırsa çalışma alanı omik bölgeye kayar. Bu durumdaki çalışma noktaları ID=15.7mA ve 0.4mA 'dir. VDD ID(mA) ID IDSS= 20 RD 15 IG IDSS=20mA, 4mA G RG + VDS³(VGS-VP) D S 10 VP=-8.74V, -1.46V 5 VGG 2V -10 -8 -6 (a) -4 -2 VGS(V) (b) Şekil-4.13. a) n-kanallı JFET'in sabit kutuplama devresi (IG=0 olduğundan VGS=-2V'tur. b) 2N3823 JFET'nin alt ve üst sınırlarına ait iki çalışma noktasını gösteren transfer karakteristikleri. Noktalardan biri kesimde (ID=0) iken, diğeri doyma bölgesindedir. Şekil-4.14'teki devrede ise VGS ön gerilimi RSS direnci üzerindeki gerilim düşümü ile sağlanmaktadır. Eğer, IG akımı sıfır kabul edilirse kapı çevresinden, Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 19 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI VGS I G R G R SS I D 0 . 5 I D eşitliği elde edilir. Bu lineer bir eşitlik olup, yük doğrusu adını alır. Şekil-4.14.b'de RSS=0.5kΩ için yük doğrusu çizilmiştir (VGS=-0.5ID). İkinci eşitlik ise, ID I DSS V 2 P ( V GS V P ) 20 2 ( 8 . 74 ) 2 7 . 5 ( 8 . 74 ) 2 olup, bu iki denklemin çözümünden; VGS=-3.54V, ID=7.08mA elde edilir. VDD ID(mA) ID IDSS= 20 Küçük RSS RD 15 RSS=0.5k IG=0 D IDSS=20mA, 4mA G S RG ID 10 Büyük RSS VP=-8.74V, -1.46V RSS 5 + -10 -8 -6 (a) -4 -2 VGS(V) (b) Şekil-4.14 a) RSS direnci ile oluşturulmuş kendi kendine kutuplama devresi. b) RSS=0.5kΩ için her iki çalışma noktası da doyma bölgesindedir. Alt sınır için yani IDSS=4mA ve VP=-1.46 için VGS=-0.637V ve ID=1.27mA elde edilir. RSS direnci küçüldükçe iki çalışma noktası arasındaki fark artar. RSS direnci büyüyünce yük doğrusunun eğimi azaldığı gibi iki nokta arasındaki fark da azalır. Görüldüğü gibi Şekil-4.13.a'daki sabit kutuplama devresinde çalışma noktaları arasında oldukça fark vardır. Bundan dolayı kendi kendine kutuplama devresi daha uygundur. Çalışma noktaları arasındaki farkı azaltmak gayesi ile Şekil-4.15.a'daki devreyi gözönüne alalım. Bu devrede hem sabit, hem de kendi kendine kutuplama vardır. VP ve IDSS 'teki değişim fazla olmasına rağmen, ID 'nin sabit kalması için yük doğrusunun yatay eksene paralel olması gerekir. Yaklaşık bir çözüm için çalışma noktasındaki kollektör akımı IDSS=4mA civarında olmalı ve yük doğrusu Şekil4.15.b'deki gibi olmalıdır. Şekil-4.15.a'dan yük doğrusu denklemi, VGS VGG R SS I D olur. Bu doğrunun çizimi için (ID=0, VGS=VGG) ve (ID= VGG/RSS, VGS=0) noktalarını gözönüne almak uygun olur. Gerçek çalışma noktası; yük doğrusu ile transfer eğrisinin kesim noktasıdır. VGG=10V, ID=4mA ve VGS=0 için RSS=2.5kΩ olup çalışma noktası VGS=-4.10V ve ID=5.64mA'dir. Şekil-4.15.c 'deki devrede VG kapı-toprak gerilimi pozitif olduğundan bu gerilim gösterildiği gibi VDD kaynağından bir gerilim bölücü ile elde edilebilir. Böylece tüm devre için bir gerilim kaynağı yeterli olmuş olur. Kapı akımının ihmal edildiği düşünülürse, Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 20 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI VDD VDD VDD ID ID R1 RD IG RD D D G VG G S S RG R2 RSS RSS VGG + (c) (a) ID(mA) IDSS= 20 15 (4.1V, 5.64mA) RSS=2.5k VG=10V 10 5 -10 -8 -6 -4 -2 2 4 6 8 10 VGS(V) (b) Şekil-4.15 a) Sabit ve kendi kendine kutuplama devresi. b) Alt ve üst limitler (veya farklı JFET'ler) için oldukça yakın kollektör akımlarını veren yük doğrusu. c) (a) devresinin pratikteki uygulaması. V G V DD R2 R1 R 2 olur. Eğer, VDD=25V ve VGG=10V ise R1=1.5R2 olmalıdır. FET'in giriş direncini büyültmek gayesi ile R1 veya R2 dirençlerinin büyük seçilmesi daha uygun olur. Şekil-4.16a'daki ortak emetörlü devresinde orta frekans kazancının büyük olmasını sağlamak için RSS direncine paralel bir köprüleme kapasitesinin konulması gerekir. Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 21 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI VDD ID(mA) VDD ID R1 RD D G Kanal ayarlamalı S R2 Kanal oluşturmalı VP RSS VGS (a) (c) ID IDSS1 VG R2 VDD R1 R 2 IDSS2 VP1 VP2 VGS (b) Şekil-4.16 a) n-kanallı arıtılmış MOSFET'in pratik kutuplama devresi. b) V G ve RSS'in yeterli derecede büyük olması ile farklı elemanlar için benzer ID değerleri elde edilir. c) Kanal ayarlamalı-kanal oluşturmalı modtaki MOSFET'in transfer karakteristiği. Kanal ayarlamalı MOSFET'in kutuplama devresi de benzer bir devre olup, Şekil-4.16.a'da gösterilmiştir. Buradaki yük doğrusu, V GS R2 R1 R 2 V DD R SS I D şeklindedir. Doyma bölgesindeki çalışmalar için VDS≥VGS-VP şartının sağlanması gerekir. Burada da kapı akımının akmadığı düşünülmüştür. Şekil-4.16.c'de ise arıtılmış ve arttırılmış modtaki çalışmalara ait transfer eğrileri gösterilmiştir. 4.7. KANAL OLUŞTURMALI MOSFET'İN ÇALIŞMA NOKTASI Bu tip MOSFET'in de çalışma noktası daha önceki kurallara göre bulunur. Kanal oluşturmalı MOSFET'in doyma bölgesindeki transfer eğrisinin matematik ifadesi, Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 22 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI VDD ID VG/RSS VG R2 VDD R1 R 2 VDD ID R1 RD D G Eğim=1/RSS S R2 0 VT1 VT2 RSS VG VGS (a) (b) Şekil-4.17 a) n-kanallı kanal oluşturmalı MOSFET'in transfer karakteristikleri ve yük doğrusu. b) Sabit ve kendi kendine kutuplama devresi. ID K 2 ( V GS V T ) 2 şeklindedir. Sıcaklığın artması ile VT ve K'nın değerleri azalır. JFET'te ise IDSS sıcaklıkla azalır. Bu değişiklik benzer isimli elemanlar arasındaki farktan büyük olamaz. Farklı iki VT ve K değeri için n-kanallı MOSFET'in transfer karakteristiği Şekil-4.17.a'da gösterilmiştir. Burada da sabit kutuplama devresi ile oluşan yük doğrusu oldukça farklı ID çalışma noktaları oluşturmaktadır. Şekil-4.17b'deki sabit ve kendi kendine kutuplama devresine ait yük doğrusu denklemi, VGS VG R SS I D olur. Kapı akımı ihmal edildiği için kapı gerilimi, V G V DD R2 R1 R 2 olur. R1, R2 ve RSS 'in değerleri JFET ve kanal ayarlamalı MOSFET'te hesaplandığı gibi hesaplanır. Burada VGS≥VT'dir. Şekil-4.17.b'deki devrenin tasarımını sayısal bir örnek üzerinde yapılım. ID(µA) 800 600 400 Q1 360µA Q2 240µA VG 200 0 VT1 VT2 2 3 4 5 VGS Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 23 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI Şekil-4.18 Kollektör akımı 240≤ID≤360µA olan bir kanal ayarlamalı MOSFET'te çalışma noktası Q1 ve Q2 arasındaki herhangi bir noktadadır. I D ( 300 60 ) A , V DD 10 V V T 1 0 . 5 V , K 1 200 A / V V T 2 1 V , K 2 100 A / V 2 2 Değerleri ile transfer karakteristiği denkleminden, I D1 200 ID2 200 2 2 ( V GS 1 0 . 5 ) ( V GS 2 1) 2 2 eşitlikleri yazılabilir. Bu iki transfer karakteristiği Şekil-4.18'de gösterilmiştir. ID1=360µA için VGS1=2.40V ve ID2=240µA için VGS2=3.19V değerleri bulunur. Bu iki nokta yardımı ile RSS için bulunabilecek en küçük değer, R SS 3 . 19 2 . 40 360 240 x 10 6 . 61 k 6 kadardır. Yük doğrusu ile yatay eksenin kesim noktası VGS=VG olup, VG 3 . 19 ( 240 x 10 6 ) x 6 . 61 x 10 4 . 78 V değerindedir. 3 Gerilim bölücü devreden, V G = 10 R2 = 4.78V yazılır. R1 + R2 Keyfi olarak R2=100kΩ seçilirse, R1=109.3kΩ olur. Bundan sonra RD'nin değeri hesaplanmalıdır. RD'nin büyük değerli olması işaret kazancını arttırır. Çok büyük olursa transistör omik bölgeye kayabilir. Doyma bölgesindeki çalışma için geçerli olan VDS≥VGS - VT şartından faydalanarak, VDS1≥2.40-0.5=1.90V ve VDS2≥3.19-1=2.19V elde edilir. (RSS+RD)'deki toplam gerilim düşümü, V1=10-1.90=8.10V ve V2=10-2.19=7.81V olur. Bunlardan biri kullanılırsa, (RSS+RD)=V1/ID1=8.10/0.360=22.5kΩ olur. RSS=6.61kΩ olduğuna göre, RSS+RD=6.61+RD≤22.5kΩ bulunur. Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 24 ELEKTRONİK TRANSİSTÖRLÜ DEVRELERİN DC ANALİZİ VE TASARIMI Buradan RD=15kΩ olarak alınabilir. 4.8. ORTAK KOLLEKTÖRLÜ (DRAIN) VE ORTAK KAPILI (GATE) DEVRELERİN KUTUPLANMASI Ortak kollektörlü bir JFET'in kutuplama devresi Şekil-4.19.a'da gösterilmiştir. Dikkat edilirse bu devre ortak emetörlü devrede (Şekil-4.15.c) RD=0 yapılarak elde edilir. Ortak kapılı devre ise Şekil4.19.b'de çizilmiştir. Değişken işaretlerde kapı ucunun topraklanması için R2'ye paralel büyük değerli bir kapasitenin bağlanması gerekir. Şekil-4.19'daki devreler arıtılmış ve arttırılmış modtaki MOSFET'ler için de kullanılır. Çalışma noktası doyma bölgesinde olacak şekilde devre elemanları hesaplanmalıdır. VDD VDD ID S Giriş R1 D G D G Giriş RSS R2 ID R1 RD + Çıkış S Çıkış R2 VDD RSS (a) (b) Şekil-4.19. a) Ortak kollektörlü n - kanallı JFET'in DC kutuplama devresi. b) Ortak kapılı n - kanallı JFET'in DC kutuplama devresi. R2 direnci büyük değerli bir kapasite ile değişken işaretler için köprülenir. Prof. Dr. Halit PASTACI (ÇOĞALTILIP SATILAMAZ) 25