MAKROMODELLER

• Makromodeller, herhangi bir elemanın veya

devrenin lineer ve lineer olmama

ğ

uygun

yg

özelliklerini aslına olabildiğince

modellemek üzere, lineer elemanlar,

bağımlı ve bağımsız kaynaklar ve az sayıda

diyot, tranzistor gibi lineer olmayan

elemanlarla

l

l l oluşturulan

l t l eşdeğer

d ğ ddevreler.

l

Makromodellerin amacı:

• Çok tranzistorlu yapılarda benzetim süresini

kısaltmak

• Geniş ölçekli yapıların benzetiminde

nümerik analiz problemlerinin giderilmesi

• Aktif

k if elemanların

l

l

id

idealsizlik

l i lik analizi

li i

Günümüzdeki makromodeller üç ana

grup altında toplanabilirler:

• 1. Lineer olmayan kontrollu kaynaklar içeren modeller

•

Bu tür modellerde,

modellerde lineer olmama özelliğini temsil eden

analitik fonksiyonlar kullanılır.

y içeren

ç

modeller

•

2. Yarıiletken diyot

•

Bu tür modellerde, lineer olmamayı temsil etmek üzere

yarıiletken diyotların üstel akım-gerilim ilişkisinden

yararlanılmaktadır.

l l k d

•

3. Yarıiletken tranzistor ve diyot kullanan modeller

•

Lineer olmamanın hem tran

tranzistor,

istor hem de diyot

di ot

elemanlarının kullanılmasıyla temsil edildiği modeller bu

ggruba ggirmektedir.

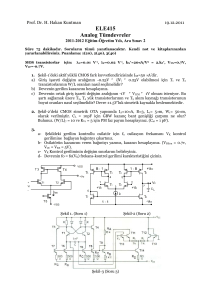

Ö k 11: İşlemsel

Örnek

İl

l kuvvetlendirici

k

tl di i i

makromodelleri

C

VCC=15V

I2

T3

R1

T4

T5

1mA

vi

+

T1

IT

T7

T6

-VEE

I1

360uA

-VEE

25uA

T8

T9

R5

T2

IQ

0.5mA

vo

T15

Ix

50uA

R4

T11

RL

1k

T10

T14

T12

T13

R2

R3

-VEE=-15V

•

İşlemsel

ş

Kuvvetlendirici Yapı

p Örneği

ğ

Ö k 11: İşlemsel

Örnek

İl

l kuvvetlendirici

k

tl di i i

makromodelleri

+V CC

RC1

R

C 1 C2

VC

R

P

Vb

C2

+V a -

D

1

R2

R e1 Ve Re2

CE

I

EE

R O1

Vc

RE

G cm .Ve G .V

a a

D

D4 +V O

2

R

O2

RC

D3

V

E

Gb .V b

-V EE

• Tranzistorlar, yarıiletken diyotlar, bağımlı ve bağımsız

kaynaklar ve lineer elemanlar kullanılarak kurulan işlemsel

kuvvetlendirici makromodeli (Boyle 1974)

• yapıda çok fazla sayıda yer alan fiziksel

ggerçek

ç elemanlar yerine

y

basit ideal

elemanlar

• Basit bir diferensiyel

y ggiriş katı yyardımıyla

y

lineer olmayan giriş karakteristiğinin

modellenmesi.

• T1-T2 tranzistorları ve bunlarla ilişkili diğer

elemanlar ile yapının fark ve ortak işaret

davranışı.

• CE kondansatörü yükselme eğimi,

• C1 kondansatörü faz yanıtı

• Ara kattaki Gcm , Ga , R2 , RO2 elemanları

Fark

k ve ortak

k iişaret kazançları

k

l

• Çıkış katında D1 , D2 , RC elemanları

yapının kısadevre akımının maksimum

ğ ,

değeri,

• D3 ,VC ve D4 ,VE elemanları

l

l

çıkış

k

geriliminin maksimum değerini ve kırpılma

sınırları

• Yapının çıkış katı devreye tam anlamıyla

b

benzemeyen,

ancakk ddevre öözelliklerini

llikl i i

sağlayan bir topoloji kullanılarak

kurulmuştur.

• Tüm makromodeller, bir tümdevre benzetim

programı ile birlikte kullanılacakları

ş

ile tasarlanırlar.

düşüncesi

+VCC

3

css

1+

2-

rss

j1

iss

dp

4

-VEE

rp

j2

C1

rd1

d1

+

vc 9

r2 6

dc

rd2

d2

ve

+

de

-

+

vb

-

-

gcm

+

din

+

fb

egnd

ga C2

dip

ro2

+

6

7 +

hlim

vlim

ro1

vip

5

+VO

Giriş

Gi

i katı

k t p kkanallı

ll JFET’l

JFET’lerle

l kurulmuş

k l

olan

l işlemsel

il

l

kuvvetlendiriciler için geliştirilen makromodel (LF351 ).

vin

din

+VCC

3

Cee

1+

2-

ree

re1

Q1

4

rc1

-VEE

•

iee

dp

+

vc 9

r2

2

dc 6

rp

re2

Q2

C1

ve

de

rc2

+

-

gcm

+

vb

-

+

C2

egnd

ga

-

ro2

dip

+

+

fb

7 +

hlim vip

vlim

6 -ro1

vin

5

+VO

Giriş katı pnp tranzistorlarla kurulmuş olan işlemsel kuvvetlendiriciler

için geliştirilen makromodel (LM324) .

+VCC

rc1 C1

1+

2-

rc2 dp

rp

Q1 Q2

re1 re2

Cee ree

gcm

ve

de

iee

4

-VEE

•

+

vc 9

r2

dc 6

+

-

+

vb

-egnd

C2

ga

ro2

+

-

+

dip

din

+

fb

7 +

hlim

vlim

6 ro1

vip

vin

5

+VO

Giriş katı npn tranzistorlarla kurulmuş olan işlemsel kuvvetlendiriciler

için geliştirilen makromodel (LM301A ).

R O2

+V 4

V OS

P

R ID/2

VA

R

+V

IC

R ID/2 CM

R IC

N

+'

K

V

CM CM

-

I B1

I1

R1

+ V1 -V2

D1 +

D2

I B2

VB

I 1 = G1 .(( VA-V

V B)

+V5

C1

I2

+

R2

-

D3 - V +V4 D

3

4

I 2 = G2 .V

V4

RO1

D 5 D6

C2

V5

+ VO

+

VO

-

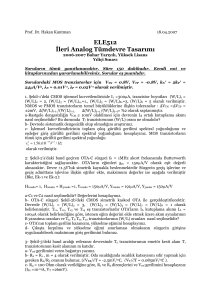

• Yarıiletken diyotlar,

diyotlar bağımlı ve bağımsız kaynaklar ve

lineer elemanlar kullanılarak kurulan işlemsel

kuvvetlendirici makromodeli (Peic, 1991).

• Birinci ara katta V1

V1-D1

D1 ve V2-D2

V2 D2 gerilim

sınırlama devreleri

• Birinci hücrede C1 ve R1 elemanları

yapının transfer fonksiyonunun baskın

olmayan ikinci kutbu

• ikinci ara hücrede G2.V4 kontrollu kaynağı

C2 kkondansatörü

d

ö ü üüzerindeki

i d ki gerilimin

ili i

yükselme hızı

• İkinci kazanç katında R2 ve C2 elemanları

y

f1

kuvvetlendiricinin transfer fonksiyonunun

baskın kutbu

Model Parametrelerinin belirlenmesi

Burada diyotlar ideal alınmıştır.

• Ortak işaret kazancı ve dengesizlik akımı

• Gerçek diyot modeli kullanılırsa, diyot

d

doyma

akımı

k

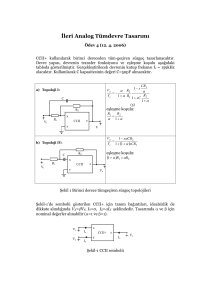

Örnek

Ö

k 22: Geçiş

G i il

iletkenliği

tk liği kuvvetlendiricisi

k

tl di i i i

(OTA) makromodeli (Kuntman 1994)

• İşlemsel kuvvetlendiricilerden daha geniş

bandlı olmaları ve eğimlerinin kontrol

y OTA'lar da

edilebilir olması nedeniyle

gittikçe yaygınlaşarak kullanım alanı

bulmaktadır.

bulmaktadır

OTA devre sembolü

tanım bağıntısı

I

O

,

Gm =

V I1 - V I 2

Gm = f ( I A)

IA kontrol akımı

• CMOS tteknolojisi

k l ji i il

ile kolayca

k l

tümleştirilebilme

• OTA-C aktif süzgeçleri

• Çok sayıda OTA içeren aktif süzgeçlerin

benzetim sürelerinin kısaltılması

• Geniş ölçekli devrelerde nümerik sorunların,

ıraksama sorunlarının giderilmesi

Simetrik BJT OTA Yapısı

B:1

1:B

T5

T3

T4

4

1

T1

+VI1

+VDD

T6

5

3

T2

2

VO

7

+VI2

CL

6

IA

T7

T8

1:1

• Simetrik CMOS-OTA yapısı

y p

-VSS

Temel tanım bağıntıları

G m = B.. K n . I A .(W / L )1

I Omaks = - I Omin = - B. I A

KV = G m . R O

fd

1

=

2.π . RO .( C n7 + C L )

f nd1

g m7

f nd 2 =

2.π .C n6

g m4

=

2.π .C n5

f z = 2. f nd 2

GBW = KV . f d

B. I A

YE =

C L + Cn7

+VDD

-V

V 'P

R I1

- VOS +

P

C2

C1

+V CMN

C3 RI2

+

V 'N

K

.V

CM CM

.V

I1 = g m1

1 ID

VID=V ' -V '

P N

+V1

Cn5

I1

R3

I2 = B

B.g

g m4 .V

V1

R 3 =1/g

m4

+ VC - R C

D4

- V +R

E

E

D3

SS

A

+V

D1 A

+

V

- B1

+ V2

Cn6

I 2 R4

I3

I 4 R O2

I 3 = gm7

V2

7 .V

R 4= 1/g m 7

+

VO

-

I

4

R

+VO

D2 O1

CO

V B2

+

=G

G.(VA - V O)

• Simetrik CMOS OTA için makromodel.

M d lP

Model

Parametrelerinin

t l i i Belirlenmesi

B li l

i

M d lP

Model

Parametrelerinin

t l i i Belirlenmesi

B li l

i

Benzetim Sonuçları

Model parametreleri, IA = 100 μA

eleman

değer

eleman

değer

VOS

59E-3 V

Cn6

.06018 pF

VB1

10 7V

10.7V

RO2

42 kΩ

VB2

13.11V

RO1

31 kΩ

VC

1.46V

CO

0.15pF

VE

1.673V

RC

2.2 kΩ

RI1

12.0E+12Ω

RE

2.2 kΩ

RI2

12.0E+12Ω

12.0E

12Ω

gm11

2.72E-44 A/V

2.72E

C2

0.028pF

gm5

3.04E-4 A/V

C3

0.028pF

gm7

2.42E-4 A/V

C1

0.153pF

G

2.2E-5 A/V

R3

12.626 kΩ

KCM

1E-3

Cn55

0.338pF

R4

4.132 kΩ

• Simetrik CMOS OTA için

ç VO-(VP

(

- VN)) ggeçiş

çş

eğrisi

• Simetrik CMOS OTA için IO-(VP - VN) geçiş eğrisi

•

Simetrik CMOS OTA’da Gm g

geçiş

ç ş iletkenliğinin

ğ

frekansa bağımlılığı

ğ

ğ

• Simetrik CMOS OTA’da KV gerilim kazancının

f k

frekansa

bbağımlılığı.

ll

Tasarım Örneği,

Örneği 4.

4 derece AG

Butterworth süzgeç

g ç

OTA2

OTA1

+

+

+V

IN

+V O

C1

C2

a0

___________________

2

s + b 1s + b 0

g /C = b / b

0 1

m1 1

g m2 / C 2 = b 1

,

a0 = b

0

• İkinci dereceden alçak geçiren OTA-C aktif süzgeç

d

devresi.

i

• Ardarda bağlı iki 2.

2 derece süzgeç

• Bütün OTA'ların eğimleri eşit ve Gm =

1 041 mA/V

1.041

A/V

• İlk hücrenin değer katsayısı QP1 = 1.307,

• ikinci hücrenin değer katsayısı QP2 = 0.541

• köşe frekansı ωP = 22.34

34 x 106 rad/sn

• normalize geçiş fonsiyonu

1

H(s) =

2

2

( s +0,765s +1).( s +1,848s +1)

• Dördüncü

ö dü cü dereceden

de ecede alçak

a ça geçiren

geç e OTA-C

O

C aaktif

t süzgecinin

sü gec

DC gerilim geçiş eğrisi.

Süzgecin

g

frekans eğrisi.

ğ

Zaman bölgesi

g yyanıtı

Benzetim Süresi Kısalma Çarpanı

T(makromodel) = K * T(eleman modeli)

• DC Analiz: K = 0.35

• AC Analiz: K = 00.644

644

• Zaman Bölgesi Analizi (Transient):

K= 0.252

0 252

Örnek

Ö

k 33: Ak

Akım ttaşıyıcı makromodeli

k

d li

(Tarım, Yenen, Kuntman 1996, 1998)

vx

i

x

x

vy

y

CCX +-

z

iz

vz

iy

• Akım Taşıyıcı

ş y Devre Sembolü (X=I,

(

, II,, III))

Örnek 3: Akım taşıyıcı makromodeli

• CCII, aşağıda verilen bağıntılarla

tanımlanan üç uçlu bir devredir:

,

,

v X = vY

iY = 0

iZ = m i X

• İdeal bir akım taşıyıcıda,

şy

, ggirişş ve ççıkışş

empedansları sonsuz, band genişliği

sonsuz X ucundan içeriye doğru

sonsuz,

bakıldığında görülen empedans sıfırdır.

• Uç büyüklüklerinin sınırları

I X min < i X (t ) < I Xmaks

V X min < v X (t ) < V Xmaks

VZ min < v Z (t ) < VZmaks

T5

T14

T7

T12

T13

T8

M9

T15

T16

VDD

T10

T11

iz = ix

Z

I

X

bias

R

x

in +

in -

i

T1

Y

T2

Rz

x

Cc

R

bias

T3

T4

CMOS CCII devresi I

T6

T17

T18

VSS

T5

T6

T3

T4

T10

T9

iz = ix

x

T2

I

V

Y

X

v

y

I

B

T7

B

Z

i

x

Rx

Rz

I

B

T13

bi 1

bias1

V

DD

T12

M11

v

T1

V

T14

T8

bias 2

CCII devresi II

T15

T16

V

SS

İdeal Olmama,, Küçük

ç İşaret

ş

Eşdeğer

ş ğ

devresi

• Akım Taşıyıcı

ş y Makromodeli

Makromodel bağıntıları

RE = RP//RX,

RX büyüklüğü X ucuna dışarıdan bağlanan direnç

Benzetim Sonuçları

RX = 5k

5k, RZ = oo için eleman modeli ve makromodel yardımıyla elde

edilen VX-VY ve VZ-VY değişimleri.

X ucundan içeriye ve dışarıya doğru akıtılan akımın sınırları, RX = 0.

• RX = ∞ için

ç VX - VY değişimi

ğş

X ucundan görülen ZX empedansının frekansla değişimi için

makromodel ve eleman modeli yardımıyla elde edilen simülasyon

sonuçları.

•

Z ucundan görülen ZO empedansının frekansla değişimi için

makromodel ve eleman modeli yardımıyla elde edilen simülasyon

sonuçları.

•

vx/vy ve vz/vy gerilim transfer oranlarının frekansla değişimi için

makromodel ve eleman modeli yardımıyla elde edilen simülasyon

sonuçları.

l

Ö k CCII+ ve CCII

Örnek,

CCII- tabanlı

b l aktif

k if süzgeç

ü

Y

Z CCII+

X

R2

Y

Vi

CCII- Z

10k

X

C1

R1

Y

.1nF

Vo

CCII- Z

X

10k

R3

R4

10k

10k

fp

p = 159kHz,, Qp = 0707

C2

.1nF

• Süzgecin

g

Frekans Eğrisi

ğ

•

Sinüs y

yanıtı,, Girişş işareti

ş

VP = 1V,, f = 100kHz

Yükselme eğimi nedeniyle çıkış

işaretinde

ş

ortaya

y çıkan

ç

bozulma

• THD = %3,4 (Eleman modeli ile)

• THD = %2

%2,88 (Makromodel ile)

Benzetim Süresi Kısalma Çarpanı

T(makromodel) = K * T(eleman modeli)

• AC Analiz:

K = 00.093

093

• Zaman Bölgesi Analizi (Transient):

• K=

K 00.188

188

Kaynaklar:

• H. Kuntman, Modified Ebers-Moll model,

Electronics Letters,

Letters Vol.18,

Vol 18 No.7,

No 7 pp.293

pp 293294,1982.

• H. Kuntman: Application

pp

of modified Ebers-Moll

model to nonlinear distortion analysis of transistor

amplifiers, Electronics Letters, Vol.19, No.4,

pp 126 127 1983

pp.126-127,1983.

• H. Kuntman: New Method for modelling highinjection effects in bipolar transistors,

transistors Bulletin of

The Technical University of İstanbul,

Vol.37,No.1,pp.73-79, 1984.

• H

H. Kuntman

Kuntman, H

H. Çelik: A nonlinear analysis and

simulation program for bipolar transistor circuits,

Bulletin of The Technical Universityy of Istanbul,,

Vol.39, No.1, pp.89-107, 1986.

• H. Kuntman: Novel modification on SPICE BJT

model

d l to obtain

b i extended

d d accuracy, IEE Proc.

P

PtP

G, Vol.138, pp.673-678,1991.

• H.

H Kuntman and S

S. Özcan: Minimisation of total

harmonic distortion in active-loded differential

BJT amplifiers,

p

, Electronics Letters,Vol.27,

,

,

pp.2381-2383, 1991.

• H. Kuntman: On the harmonic distortion

coefficients

ffi i t off active-loaded

ti l d d BJT amplifiers,

lifi

International Journal of Electronics,

Vol.72,pp.459 465,1992

Vol.72,pp.459-465,1992

•

•

•

•

H. Kuntman, S. Özcan:

Ö

Extraction of SPICE BJT model

dynamic parameters from dc measurement data,

International Journal of Electronics,, Vol.74,,

No.4,pp.541-551,1992.

E.İ.Tekdemir, H. Kuntman: Implementation of a novel

BJT model into the SPICE simulation program to obtain

extended accuracy, International Journal of Electronics,

Vol.75, NO.6, pp.1185-1199, 1993.

H K

H.

Kuntman:

t

IImproved

d representation

t ti off channel-length

h

l l th

modulation in junction field-effect transistors,

International Journal of Electronics, Vol.75, No.1,pp.5764 1993.

64,

1993

H. Kuntman: Simple and accurate nonlinear OTA

macromodel for simulation of CMOS OTA-C active

filters, International Journal of Electronics, Vol.77,

No.6, pp.993-1006, 1994.

•

•

•

N. Tarım, B. Yenen, H. Kuntman: Simple and accurate

nonlinear

li

current conveyor macromodel

d l for

f simulation

i l i

of active filters using CCIIs, International Journal of

Circuit Theory and Applications, 26, pp.27-38, 1998.

N. Tarım, B. Yenen, H. Kuntman: Simple and accurate

nonlinear current conveyor macromodel, Melecon 96:

8th Mediterranean Electrotechnical Conference, Vol.1,

pp 447-450, May 13-16, Bari, Italy, 1996.

M. Yazgı, H. Kuntman, A new approach for parameter

extraction of complex models and an application for

SPICE MOSFET level-3 static model, Microelectronics

Journal, Vol.30, No.2, pp.149-155, 1999

• H. Kuntman and A. Toker, 'Novel nonlinear

macromodel suitable for SPICE simulation of

analogue multipliers realised with bipolar and

CMOS technologies', Int. Journal of Circuit

Theory and Applications, 27, pp.485-495, 1999.

p and accurate

• U. Cam and H. Kuntman,, ‘Simple

non-linear macromodel for four terminal floating

nullors ((FTFNs)’

) Int. Journal of Electronics, Vol.

88, No.4, pp 435-447, 2001.

•

•

U. Çam,

U

Çam H.

H Kuntman,

Kuntman Simple and accurate non

nonlınear macromodel for four terminal floating

nullor ((FTFN),

), Proc. of Int. Conference on

Electrical and Electronics Eng. ELECO'99,

Electronics: pp. 73-77, Bursa,Turkey, 1-5

December

b 1999.

H. Kuntman, A. Dolar: Implementation of a

Novell MOSFET

OS

Model

d l into

i

S C

SPICEProgram

to

Obtain Extended Accuracy for Simulation of

Analogue Circuits,

Circuits Proc.

Proc of the 7th International

Conference

on

OPTIMIZATION

OF

ELECTRICAL

AND

ELECTRONIC

EQUIPMENT: OPTIM 2000, May 11-12, 2000

Brasov,, ROMANIA,, pp

pp. 765-770.

•

•

G. Dü

G

Düzenli,

enli H.

H Kuntman,

K ntman The Basic of an Analytical

Anal tical

Model Development for the P-MOS Transistor

Degradation,

g

Proc. of OPTIM’2002 (8th

(

International

Conference: OPTIMIZATION OF ELECTRICAL AND

ELECTRONIC EQUIPMENT), pp. 829-834, May 1617 2002 Brasov,

17,

Brasov ROMANIA

ROMANIA.

F. Kaçar, A. Kuntman, H. Kuntman, "A Simple

pp

for Modellingg The Influence of Hot-Carrier

Approach

Effect ON Threshold Voltage Of MOS Transistors",

Proceedings of the 13th International Conference on

Microelectronics (ICM

(ICM’2001)

2001), pp.43-46,

pp 43-46 Rabat,

Rabat

Morocco, October 29-31, 2001.

• H

H. Kuntman

Kuntman, Elektronik Elemanların

Modellenmesi, İTÜ Kütüphanesi, 1998.

• H. Hakan

k Kuntman, Analog

A l MOS

OS

Tümdevre Tekniği, İTÜ Kütüphanesi, Sayı:

1587, 1997.

• H.

H H

H. Kuntman

Kuntman, Analog tümdevre tasarımı

tasarımı,

Birsen Yayınevi, İstanbul, 1998.

• P. Antognetti, G. Massobrio,

g with

Semiconductor device modeling

SPICE, Mc Graw Hill, 1988.

• BOYLE,G.R., COHN, B.M., PEDERSON,

D O and

D.O.

d SOLOMON

SOLOMON, JJ.E.,

E M

Macromodeling

d li

of integrated circuit operational amplifiers,

IEEE Journal of Solid-State Circu-its, 9,

353-363,

353

363, 1974.

• PEIC, R.V., Simple and accurate nonlinear

macromodel

d l for

f operational

ti l amplifiers,

lifi

IEEE Journal of Solid-State Circuits, 26,

896-899, 1991.