KOCAELİ ÜNİVERSİTESİ

TEKNİK EĞİTİM FAKÜLTESİ

ELEKTRİK ÖĞRETMENLİĞİ

4. SINIF

ELK 435

ENDÜSTRİYEL ELEKTRONİK

LABORATUAR UYGULAMALARI

HAZIRLAYANLAR

Doç.Dr. Engin ÖZDEMİR

Arş.Gör. Mehmet UÇAR

EKİM 2009

İÇİNDEKİLER

Deneysel Çalışma 1: İşlemsel yükselteçleri (op-amp) tanımak ve önemli parametrelerini

incelemek. 747 op-amp’ını kullanarak, giriş ofset gerilimini ve giriş polarlama akımını

ölçmek.

(Sayfa: 2)

Deneysel Çalışma 2: Op-amp uygulaması olarak eviren yükselteci (inverting amplifier)

incelemek.

(Sayfa: 10)

Deneysel Çalışma 3: Op-amp uygulaması olarak evirmeyen yükselteci (non-inverting

amplifier) incelemek.

(Sayfa: 14)

Deneysel Çalışma 4: Op-amp uygulaması olarak gerilim izleyici (voltage follower)

devresini incelemek.

(Sayfa: 18)

Deneysel Çalışma 5: Op-amp uygulaması olarak toplar yükselteci (summing amplifier)

incelemek.

(Sayfa: 20)

Deneysel Çalışma 6: Op-amp uygulaması olarak çıkartma yapan devreyi (difference

amplifier) incelemek.

(Sayfa: 22)

Deneysel Çalışma 7: Op-amp uygulaması olarak türevleyici (differentiator) devresini

incelemek.

(Sayfa: 25)

Deneysel Çalışma 8: Op-amp uygulaması olarak integratör devresini incelemek.

(Sayfa: 32)

Deneysel Çalışma 9: Kıyaslayıcı (comparator) devresini incelemek.

(Sayfa: 35)

Deneysel Çalışma 10: PWM üretici SG3524 ile Buck (azaltan) çevirici devresini incelemek.

(Sayfa: 39)

Deneysel Çalışma 11: Op-amp kullanarak hassas tam dalga doğrultmaç yapmak.

(Sayfa: 42)

Deneysel Çalışma 12: Op-amp kullanarak gerilim regülatörü yapmak ve çalışmasını

incelemek.

(Sayfa: 45)

1

DENEYSEL ÇALIŞMA

----- 1 ----KONU:

İşlemsel yükselteçleri (operational amplifier) tanımak ve önemli parametrelerini incelemek.

747 op-amp’ını kullanarak, giriş ofset gerilimi ve giriş polarlama akımını ölçmek.

ÖN BİLGİ:

İşlemsel yükselteçle (kısaca op-amp) 1940’lı yıllardan beri bilinmekle beraber, asıl yaygın

kullanım alanına 1960’lı yılların sonlarına doğru, tümleşik devre teknolojisi ile üretilmeye

başlandığı zaman kavuşmuştur. Bugün artık op-amp denildiğinde tümleşik devre durumunda

olanlar akla gelir.

Genel olarak op-amp, çok yüksek kazançlı bir DC yükselteçtir. Çeşitli özellikleri, devreye

dışarıdan bağlanan devre elemanları ve bunların bağladığı geri besleme ile kontrol altına

alınabilir. Op-amp devresi tek başına düşünüldüğünde 5 önemli özelliğe sahiptir. Bunlar:

-

Kazancı çok fazladır (örneğin 200.000)

-

Giriş empedansı çok yüksektir (5 Mohm)

-

Çıkış empedansı sıfıra yakındır

-

Band genişliği fazladır (1 MHz gibi)

-

Girişe 0V uygulandığında çıkışta yaklaşık 0V elde edilir.

Op-amp devresinin iki tür sembolik gösterilişi vardır. Bunlar Şekil 1.1’de çizilmişlerdir.

Genellikle kullanılan sembol Şekil 1.1(a)’dekidir.

Şekil 1.1

Op-amp devrelerinde, genel olarak, birbirine ters polaritede iki kaynak kullanılır. Bu

kaynaklar devre şemalarında her zaman gösterilmezler. Daha ziyade girişler ve çıkış

belirtilir.

2

Şekil 1.1’de de görüldüğü gibi op-amp devresinin biri (+) diğeri (-) ile işaretlenmiş 2 girişi

vardır. (+) girişe uygulanan işaret çıkışa aynı fazda; (-) girişe uygulanan işaret ise 180 derece

ters fazda aktarılır.

İki girişe birden uygulanan aynı işaret çıkışa aktarılmaz. (-) giriş “eviren (inverting)’’, (+)

giriş ise “evirmeyen (non-inverting)” giriş olarak isimlendirilmiştir. Devre özellikleri giriş

ucu olarak hangi ucun kullanıldığına ve çıkıştan girişe yapılan geri belsem miktarına

bağlıdır. Şekil 1.2(a)’da giriş ucu olarak (+) uç kullanılmıştır. Bu devreye “evirmeyen

yükselteç” denilir. Şekil 1.2(b)’de ise giriş (-) uçtan yapılmıştır ve devre “eviren yükselteç”

olarak bilinir. Her iki yükselteç de ileriki denetlerde ayrıntılı olarak incelenecektir. Burada

yükselteç kazançlarının farklı olduğuna dikkat çekilmekle yetinilecektir.

Şekil 1.2

Bu deneyde op-amp devresinin önemli parametrelerini üzerinde çalışma yapılacaktır. Bu

parametrelerden aşağıda kısa kısa söz edilmiştir. Deney sırasında sadece bazı parametrelerin

ölçümü yapılacak, diğerlerinin ise, ölçüm zorlukları nedeniyle ölçümleri yapılmayacaktır.

Giriş Ofset Gerilimi (Vio): Op-amp’ın (+) ve (-) girişler arasında ideal olarak “0” volt

olması gerekir. Ancak pratikte giriş uçlarının bağlı oldukları transistörlerin tam uyum içinde

olmamaları nedeniyle giriş uçları arasında, çok küçük de olsa, bir ofset gerilimi oluşur.Bu

gerilim op-amp kazancı ile çarpılarak çıkışına aktarılır ve çıkışı V0 çıkış ofset gerilimi

meydana gelir.V0 gerilimi devrenin kazancına bağlı olmasına rağmen Vi0 gerilimi sabittir.

V0 ölçüldüğünde, Vi0 giriş ofset gerilimi,

V0 = Vi 0 (1 +

R2

)

R1

Formülünden bulunur. Bu formül, op-amp devresinin eviren veya evirmeyen yükselteç

olarak çalışmasına bağlı değildir. Her iki durum için de geçerlidir. (Şekil 1.2’ye bakınız).

3

Op-amp devresinin kazancı yüksek tutulduğunda (R2/R1 oranı büyük seçilerek) çıkışta

oluşturulacak ofset gerilimi istenmeyen boyutlarda olabilir. Bu nedenle op-amp’ların

çoğunda dılarıdan ofset sıfırlama uçları bulunur. Bu uçlar arasında Şekil 1.3’deki gibi

bağlanacak bir potansiyometre ile çıkış ofset gerilimini sıfırlamak mümkündür. Sıcaklığın

giriş ofset gerilimi üzerinde etkisi vardır. Transistör tekniği ile imal edilen op-amp’larda her

bir santigrad derece sıcaklık artışında ofset gerilimi 5-10 uV gösterilir.

Giriş polarlama akımı (Ib): Her iki girişten op-amp devresine akan akımların ortalama

değeridir. Vi0 gerilimi gibi çıkışta istenmeyen DC seviye oluşumuna yol açar. Şekil 1.3’teki

devrede Vgr 0 iken akım yönleri görülüyor. Burada;

Şekil 1.3

I b = I 1 + I 2 olmaktadır. I b =

Vb Vçk − Vb

+

olur. Vb’nin çok küçük olduğu göz önüne

R1

R2

alınırsa; Vçk = I b R2 olur. Şu halde polarma akımının çıkış ofset gerilimine olan katkısı bu

şekilde bulunabilir. Giriş polarma akımının çıkışa yol açacağı ofset gerilimi oluşumunu

minimum düzeye indirmek için Şekil 1.4(a) ve (b)’deki yöntemler kullanılabilir.

Rp =

R1R 2

R1 + R 2

Şekil 1.4

Giriş ofset akımı ( Ii0 ): Vçk=0V olduğunda her iki giriş polarma akımı arasındaki farktır ve

çıkışa, Vçk = R2 I i 0 kadar ilave bir ofset geriliminin oluşmasına yol açar.

4

Giriş empedansı ( Zi ): Girişlerden birinden bakıldığında (diğeri topraklanmış durumda

iken) görülen empedanstır. Çok yüksektir.

Çıkış empedansı ( Z0 ): Çıkıştan bakıldığında görülen empedanstır. Oldukça düşüktür.

Çıkış kısa devre akımı ( Iosc ): Op-amp devresinden çekilebilecek maksimum akımdır.

Geri besleme yok iken gerilim kazancı (Avo): Op-amp devresine dışardan her hangi bir

geri besleme sağlanmadığı zaman ki çıkış geriliminin giriş gerilimine oranıdır.

Ortak mod tepki oranı (common mode rejection ratio-CMRR): Op-amp devresinin, her

iki girişine de ortak olan işareti kabul etmeme özelliğidir. Her iki girişe aynı anda uygulanan

işaretin, çıkış işaretine oranına (dB cinsinden ) eşittir.

Kanal ayırımı: Bazı tümleşik op-amp devrelerinde birden fazla op-amp bir arada

bulunabilir. Örneğin deneylerde kullanılacak 747 nolu op-amp bünyesinde iki adet

birbirinden bağımsız op-amp vardır. Bu tür op-amp devrelerinde,op-amplardan birinin

girişine uygulanan işaret, diğerinin çıkışında çok küçükte olsa bir işaret oluşturur. Bu işaret

ne kadar küçük ise kanal ayrımı o kadar iyidir. Genellikle dB cinsinden oran ifadesi

kullanılır.

Slew rate: Op-amp’ın band genişliği ile ilgili parametredir. Bu parametre V/µsn cinsinden

ifade edilir. Op-amp’ın ne kadar çabuk durum değiştireceği hakkında bilgi verir. Bu değer

ne kadar büyük ise op-amp o kadar geniş bandlıdır ve girişine uygulanan çabuk değişen

işaretleri bozmadan yükselterek çıkışa aktarır.

Örnek olarak söz konusu parametrelerin 747 op-amp’ı için tipik değerleri Tablo 1.1’de

verilmiştir. İnceleyiniz.

Tablo 1.1

Vi 0

IB

Ii0

Zi

Z0

I osc

Avo

CMRR

1mV

30nA

70nA

2MΩ

75Ω

25mA

200.000

90dB

Kanal

ayrımı

120dB

Slow rate

0,5V/msn

Ön bilgi bölümünün başlarında op-amp devresine dışarıdan geri besleme sağlamak suretiyle

devrenin özelliklerini kontrol altına alma olanağı olduğu belirtilmişti. Şekil 1.5’te op-amp

devresinin çıkışından (-) girişe R2 direni ile geri besleme yapılmıştır. Bu durumda devrenin

kazancı artık Avo değildir. Yeni kazanç, Av=R2/R1

5

Şekil 1.5

Şeklinde formüle edilir. R2 ve R1 direnç oranını ayarlamak suretiyle kazanç kontrol altına

alınır. Av daima Avo 'dan küçüktür. Örneğin, R2 = 1 M, R1 = 10 K ise Av = 100 olur.

Avo~200.000 sayısı yanında bu değer oldukça küçük kalmaktadır. Bu konuya ileriki

deneylerde daha etraflıca değinilecektir.

Burada üzerinde durulması gereken bir diğer önemli nokta da op-amp devresinin DC ve

DC’ye yakın frekanslarda yüksek kazanç göstermesidir. Avo~ 200.000 sayısı sadece DC ve

çok düşük frekanslardaki işaret uygulamaları için geçerlidir. Op-amp devresine uygulanan

işaretin frekansı yükseldikçe Avo düşer. Şekil 1.6’da bu durum 741 op-amp'ı için grafiksel

olarak izah edilmiştir. Dikkat edilecek olursa;

Şekil 1.6

Kazanç x Band Genişliği = Sabit olmaktadır. Bu sabite 1 MHz dir. Yine Şekil 1.6’dan

hemen görüleceği gibi, 5–6 Hz'e kadar Avo 200.000 civarındadır. Bu frekanstan sonra hemen

hemen doğrusal bir şekilde azalmakta ve 1 MHz civarında Avo=1 olmaktadır. Bu frekans fT

ile gösterilir ve “1 kazanç frekansı” olarak tanımlanır.

Deneylerde 747 op-amp tümleşik devresi kullanılacaktır. Bu devrenin yapısında 2 adet

birbirinden bağımsız op-amp vardır. Şekil 1.7’de 747 op-amp tümleşik devresinin bacak

tanımlaması görülmektedir.

6

Şekil 1.7

Şekil 1.8

741 op-amp devresi deneylerimizde kullanılmamakla beraber çok sık olarak rastlanır. Bu

nedenle Şekil 1.8’deki bu devrenin bacak tanımlaması da verilmiştir. 747 op-amp

devresindeki her op-amp’ın özellikleri Tablo 1.2’de verilmiştir, inceleyiniz.

Tablo 1.2

Parametre

Giriş Ofset Gerilimi

Giriş Ofset Akımı

Giriş Polarma Akımı

CMRR

Belseme Akımı

Çıkış Kısa Devre Akımı

Giriş Empedansı

Çıkış Empedansı

Kanal Ayrımı

Slew Rate

Güç Harcaması

Geri Beslemesiz Gerilim

Kazancı

Koşullar Minimum Tipik

1

7.

0,03

70

90

2

25

0,3

2

7,5

120

Ry>=2K

0,5

50

Ry>=2K 2500

Maksimum

7,5

300

0,8

3,3

85

Birim

mV

nA

µA

dB

mA

mA

MΩ

Ω

dB

V/µsn

mW

2.105

ÖN ÇALIŞMA:

1. Şekil 1.9’daki devrede Vo=100 mV olduğuna göre giriş ofset gerilimini nasıl

hesaplarsınız? ( I b = 0,1 µ A Ii0 = 0,02 µ A varsayılacaktır.)

2. Şekil 1.10’daki devrede VA = 20 mV VB = 15 mV ölçülüyor. Giriş ofset akımını

hesaplayınız. (Vo=0 V)

7

Şekil 1.9

Şekil 1.10

DENEYDE KULLANILACAK DEVRE ELEMANI VE CİHAZLAR:

2 adet 10 K direnç

1 adet 470 K direnç

Yeteri kadar kısa devre elemanı

1 adet 747 tümleşik op-amp devresi

1 adet sayısal multimetre

DENEY:

1. Deneyi Şekil 1.11’deki gibi kurunuz.

2. (+) ve (-) besleme kaynaklarını ± 12 V ayarlayınız. Her ikisini aynı anda devrenize

uygulayınız.

3. Sayısal multimetreyi mV düzeyinde gerilim ölçmeye hazırlayınız.

a). Vo çıkış gerilimini ölçüp not ediniz.

b). Ölçtüğünüz bu gerilim çıkış ofset gerilimidir. Bu gerilimi oluşturan ana 3 faktörü

yazınız.

4. Besleme gerilimlerini devreden kesip op-amp’ın iki nolu ucu ile toprak arasına R3=10K

direnç yerleştiriniz. Bu direncin konulma amacı nedir? Açıklayınız?

5. Yaptığınız değişiklikten sonra besleme gerilimlerini tekrar devrenize uygulayınız.

6. Sayısal multimetre ile

a). Vo gerilimini ölçüp not ediniz.

b). Bu değer öncekine kıyasla küçüldü mü? Niçin? Çıkış ofset gerilimi oluşturan

faktörlerden hangisi etkisizleştirilmiştir.

c). Polarma akımının ortalama değeri yaklaşık olarak hesaplayınız?

8

7. Besleme gerilimlerini kesiniz ve devreyi Şekil 1.12’deki duruma getiriniz. P

potansiyometresi başlangıçta orta konumda olmalıdır. Devrede yapılan bu değişliğin amacı

nedir?

8. Yaptığınız değişiklikten sonra devrenize gerilim uygulayınız.

9. P potansiyometresi ile oynamak sureti ile Vo ~ 0 mV yapınız.

a) Va ve Vb gerilimlerini ölçüp not ediniz.

b)

Va

V

ve b değerleri neyi verir. Buna göre Iio akımı yaklaşık ne kadardır.

R1

R3

c) Bu durumda Iio akımından dolayı çıkışta oluşan ofset gerilimini hesaplayabilir misiniz?

d) Ib ve Iio akımlarından dolayı çıkışta meydana gelen ofset gerilimleri bilindiğine göre

giriş ofset gerilimlerinden kaynaklanan çıkış ofset gerilimlerini bulunuz.

e) Bu durumda giriş ofset gerilimi ne kadardır?

f) Bulduğunuz Ib, Iio ve Vio değerlerini Tablo 1.2’de verilenlerle karşılaştırınız?

Bulduğunuz sonuçlar normal mi?

Şekil 1.11

Şekil 1.12

9

DENEYSEL ÇALIŞMA

----- 2 ----KONU:

Op-amp uygulaması olarak eviren yükselteci (inverting amplifier) incelemek.

ÖN BİLGİ:

Şekil 2.1’de, op-amp devresinin eviren yükselteç olarak kullanımı görülüyor. Burada işaret

(-) girişe uygulanmıştır. R1 giriş direnci, R2 geri besleme direncidir. Op-amp devresinin

özelliğinden dolayı X noktasındaki gerilim 0 volta yakındır. Vgr=Igr.R1 yazılabilir. Benzer

şekilde Vçk = -If.V2 olur.

If = Igr olduğundan Vçk = − I gr R2 = −(

V gr

R1

) R2 Av =

Vçk

V gr

=−

R2

olur.

R1

Şu halde eviren yükseltecin gerilim kazancı –R2/R1 oranına eşit olmaktadır. İfadenin

önündeki (-) işareti eviren yükseltecin giriş ve çıkışı arasında 180° faz farkı olduğunu

göstermektedir. Eviren yükseltecin giriş empedansı R1 direnç değerine eşittir. Çıkış

empedansı ise çok küçüktür ve Av ile ters orantılıdır. R2 = R1 olarak seçildiğinde devrenin

kazancı 1 olur. Böyle bir devre genellikle bir işaretin polaritesini değiştirilmek istendiğinde

kullanılır.

Şekil 2.1

R2 direnç değerini değiştirmek suretiyle, Şekil 2.1’de görüldüğü gibi kazancı kontrol

edilebilir bir yükselteç oluşturulabilir. K komütatörünün bulunduğu konuma göre devre

kazancı değişik değerler alacaktır. Daha önceki deneyde op-amp geri beslemesiz olarak

kullanıldığında kazancın DC ve DC’ye yakın frekanslarda çok yüksek olduğu, frekans

artıkça kazancın 1’e yaklaştığı belirtilmişti. Bu durum Şekil 2.2’de yinelenmiştir.

10

Şekil 2.2

Genellikle op-amp devrelerinin Av (Geri besleme varken ki kazanç) gerilim kazançlarının

ne olması gerektiği şu şekilde belirlenir. İstenilen band genişliğinde Avo’un değeri (Şekil

2.2’den yada benzer grafiklerden) bulunur. Emniyet payı düşünülerek Av=Avo/10 olarak

saptanır.

Örneğin band genişliğinin 10 KHz olması isteniyorsa (741 veya 747 op-amp kullanarak)

Şekil 2.2’den Avo=100 bulunur. Buna göre Av=100/10=10 olur. Şu halde 741 (veya 747)

kullanılarak 10 KHz band genişlikli bir yükselteç yapılacak ise, bu yükseltecin gerilim

kazancı 10 olacak şekilde R1 ve R2 dirençleri seçilmelidir. Kazanç daha büyük olacak

şekilde yapılacak R1 ve R2 seçimi bandı daraltacaktır.

ÖN ÇALIŞMA:

1. Şekil 2.3’deki devrenin DC gerilim kazancı R2=10K, R2=33K, R2=100K değerleri için

ayrı ayrı bulunuz.

2. Şekil 2.4’deki devrenin kazancını ve band genişliğini hesaplayınız.

Şekil 2.3

Şekil 2.4

DENEYDE KULLANILACAK DEVRE ELAMANI VE CİHAZLAR:

2 adet 10 K direnç

1 adet 33 K direnç

11

1 adet 100 K direnç

1 adet 747 op-amp

1 adet işaret üretici

1 adet osiloskop

Yeterince kısa devre elemanı

DENEY:

1. Devreyi Şekil 2.5’deki gibi kurunuz. R2=10K olacaktır.

2. Güç kaynağının (+) ve (-) bölümlerini sıra ile +12 volta ve -12 volta ayarlayınız.

3. ±12 besleme gerilimlerini devreye uygulayınız.

4. İşaret üreteci çıkışını, Frekans 1 KHz, Genliği 1 V(t-t) olan bir sinüsoidal dalgaya

ayarlayınız.

5. Osiloskobunuzun A kanalına giriş işaretini, B kanalına da çıkış işaretini uygulayınız. Her

iki kanalı da, frekansı 1 KHz genliği 2 Volt olabilecek bir işareti en iyi şekilde

görüntüleyebilecek biçimde ayarlayınız (B kanalı için daha sonra yeniden ayarlama yapmak

gerekebilir).

6. İşaret üreteci çıkışını devre girişine uygulayınız.

a). Vçk ve Vgr işaretlerini osiloskop ekranında bir arada gözleyiniz. Aralarında faz farkı var

mı? Ne kadar?

b). Devrenin gerilim kazancını bulup, Tablo 2.1'de ilgili haneye not ediniz.

Tablo 2.l

R2(K)

10

33

100

Av

7. R2 direncini 33 K yapınız. Devrenin gerilim kazancı, bu durumda ne kadar oluyor?

Tablo 2.1’de ilgili haneye yazınız.

8. R2 direncini 100 K yapınız. Devrenin gerilim kazancını bulup, Tablo 2.1’de ilgili haneye

yazınız.

12

9. Tablo 2.1' in incelenmesi sonucu:

a). Av =

R2

oluyor mu ?

R1

b). Deneysel olarak bulduğunuz sonuçları ön çalışma 1’deki bulduklarınız ile karşılaştırınız.

10. R1 = 10 K R2 = 100 K iken, işaret üretecinin frekansının yavaş yavaş artırınız.

Çıkış işaretinin genliği, hangi frekansta 1 KHz'deki genlik değerinin üçte ikisine iniyor? Bu

değeri (yükseltecin band genişliği) not ediniz ve ön çalışma 2’de bulduğunuz sonuç ile

karşılaştırınız. Farklılık varmı? niçin?

11. R1 = 10 K R2 = 33K yapınız. İşaret üreteci frekansını 1 KHz’e ayarlayınız. Sonra

frekansı yavaş yavaş artırınız.

a) Bu durum için, devrenin band genişiğini belirleyiniz.

b) Önceki işlemde bulduğunuz (Av=10) band genişliği ile bu işlemde bulduğunuz (Av=3.3)

band

genişliğini karşılaştırınız. Gerilim kazancının miktarı band genişliğini etkiliyor mu?

Nasıl ve ne ölçüde?

Şekil 2.5

13

DENEYSEL ÇALIŞMA

----- 3 ----KONU:

Op-amp uygulaması olarak evirmeyen yükselteci (non-inverting amplifier) incelemek.

ÖN BİLGİ:

Şekil 3.l'de, op-amp devresinin evirmeyen yükselteç olarak kullanılması görülüyor. Burada

işaret (+) girişe uygulanmıştır. Giriş ile çıkış işaretleri aynı fazdadırlar. Devrenin gerilim

kazancı Av =

Vçk

V gr

= (1 +

R2

) olarak ifade edilebilir. Bu bağlantıda çıkış empedansı oldukça

R1

yüksektir. Şekli 3.1’deki devrenin bir diğer çizilmiş şekli de Şekil 3.2’de gösterilmiştir. Her

iki devrenin de birbirinin aynı dikkat ediniz.

Şekli 3.1

Şekil 3.2

Evirmeyen yükselteç daha önceden incelenen eviren yükselteç arasındaki belli başlı farklar

şunlardır:

-

Evirmeyen yükselteçte giriş ve çıkış işaretleri aynı fazdadır. Eviren yükselteçte ise

arlarında 180° faz farkı vardır.

-

Evirmeyen yükseltecin giriş empedansı op-amp giriş empedansına eşit olup çok

yüksektir. Eviren yükseltecin giriş empedansı ise R1 kadardır.

-

Evirmeyen yükseltecin kazancı, eviren yükseltecinkinden daima 1 fazladır, daima da

1’den büyüktür.

Çıkış empedansı, band genişliği gibi diğer özellikler bakımında aralarında fazla fark yoktur.

ÖN ÇALIŞMA:

1. Şekil 3.3’deki devrenin gerilim kazancı, R2=10K, R2=33K, R2=100K değerleri için ayrı

ayrı bulunuz.

2. Şekil 3.4'deki devrenin band genişliğini, yaklaşık olarak, hesaplayınız.

14

Şekil 3.3

Şekil 3.4

DENEYDE KULLANILACAK DEVRE ELEMANI VE CİHAZLAR:

2 adet 10 K direnç

1 adet 33 K direnç

1 adet 100 K direnç

Yeterince kısa devre elemanı

1 adet 747 op-amp

1 adet işaret üreteci

1 adet osiloskop.

DENEY:

1. Devreyi Şekil 3.5'deki gibi kurunuz. R2=10 K olacaktır.

2. Giriş kaynağının (+) ve (-) bölümlerini sırasıyla +12 volta ve -12 volta ayarlayınız.

3. +12 volt besleme gerilimlerini devreye uygulayınız.

4. İşaret üretecinin çıkışını, Frekansı 1 KHz, Genliği 1V(t-t) olan bir sinüssoidal işarete

ayarlayınız.

5. Osiloskobunuzun A kanalına giriş işaretini, B kanalına da çıkış işaretini uygulayınız.Her

iki kanalı da, frekansı 1 KHz genliği 1 volt olabilecek bir işareti en iyi şekilde

görüntüleyebilecek biçimde ayarlayınız. (B kanalı için daha sonra yeniden ayarlama yapmak

gerekebilir).

6. İşaret üretici çıkışı devre girişine uygulayınız.

15

a). Vgr ve Vçk işaretlerini

osiloskop ekranında bir arada gözleyiniz. Aralarında

faz

farkı var mı?

b). Devrenin gerilim kazancını bulup Tablo 3.l'de ilgili haneye not ediniz.

7. R2 direncini 33K yapınız. Devrenin gerilim kazancı, bu durumda ne kadar oluyor? Tablo

3.1’de ilgili haneye yazınız.

Tablo 3.1

R2(K)

10

33

100

Av

8. R2 direncinin değerini 100K yapınız. Devrenin gerilim kazancını bulup, Tablo 3.1’de

ilgili haneye yazınız.

9. Tablo 3.1’deki sonuçlara göre;

a). Av = 1 +

R2

oluyor mu?

R1

b). Deneysel olarak bulduğunuz sonuçları ön çalışma 1’deki bulduklarınız ile karşılaştırınız.

10. Eviren yükselteç için bulduğunuz sonuçları hatırlayarak. Evirmeyen yükselteç

kazancının aynı şartlar altında, eviren yükselteç kazancından daima 1 fazla olduğunu

gözlediniz mi?

11. R1= 10K ve R2= 100K iken, işaret üretecinin frekansını yavaş yavaş artırınız. Çıkış

işareti, hangi frekans değerinde 1 KHz'deki genliğinin üçte ikisine iniyor? Bu değeri not

ediniz ve ön çalışma 2’de bulduğunuz sonuç ile karşılaştırınız. Farklılık var mı? Niçin?

12. Eviren yükselteç için bulduğunuz sonucu hatırlayınız. Eviren ve evirmeyen

yükselteçlerin, yaklaşık aynı gerilim kazançlarında, benzer band genişliğine sahip

olduklarını gözlemlediniz mi?

16

Şekil 3.5

17

DENEYSEL ÇALIŞMA

----- 4 ----KONU:

Op-amp uygulaması olarak gerilim izleyici (Voltage follower) sini incelemek.

ÖN BİLGİ:

Gerilim izleyici devresi, isminden de anlaşılacağı gibi, gerilim kazancının 1 ve giriş-çıkış

işaretlerinin aynı fazda olduğu bir yükselteçtir. Bu özellikler, kazancı 1 olan evirmeyen

yükselteç ile sağlanabilir. Böyle bir devre Şekil 4.1’de görülmektedir.Bu devrenin kazancı 1

olduğu için band genişliği de oldukça yüksektir, empedansı büyük, çıkış empedansı ise

çok küçüktür.

Şekil 4.1

ÖN ÇALIŞMA:

1. 747 op-amp'ı kullanılarak yapılan bir gerilim izleyici devresinin band genişliğini

hesaplayınız.

2. Daha önceki deneylerde incelenen transistor devrelerinden emiter izleyici devresi ile op-

amp’lı gerilim izleyici devresini karşılaştırıp benzerlikleri sıralayınız.

DENEYDE KULLANILACAK DEVRE ELEMANI VE CIHAZLAR:

1 adet 74 7 op-amp

1 adet işaret üreteci

1 adet osiloskop.

DENEY:

1. Devreyi Şekil 4.2’deki gibi kurunuz.

2. Güç kaynağının (+) ve (-) bölümlerini sırasıyla +12 volta ve -12 volta ayarlayınız.

18

3. ±12 volt besleme gerilimlerini devreye uygulayınız.

4. İşaret çıkışını, Frekansı 1 KHz, Genliği 1 V(t-t) olan bir sinusoidal dalgaya ayarlayınız

5. Osiloskobunuzun A kanalına giriş işaretini, B kanalına da çıkış işaretini uygulayınız. Her

iki kanalı da, frekansını 1 KHz genliğini 1 volt olabilecek bir işareti en iyi şekilde görülecek

biçimde ayarlayınız.

6. İşaret üretici çıkışını devre girişine uygulayınız. Vgr ve Vçk işaretlerini osiloskop

ekranında bir arada gözleyiniz. İşaretler her bakımdan birbirinin aynısı mı?

7. İşaret üretecinin frekansını yavaş yavaş artırınız. Çıkış işaretinin genliği hangi frekans

değerinde 1 KHz'dekinin üçte ikisine iniyor? Bu değeri not ediniz ve daha önceki deneylerde

bulunan çeşitli op-amp devrelerine ait band genişlikleri ile karşılaştırınız.

Şekil 4.2

19

DENEYSEL ÇALIŞMA

----- 5 ----KONU:

Op-amp uygulaması olarak ‘toplar yükselteci’ (summing amplifier) incelemek.

ÖN BİLGİ:

Şekil 5.1’de, op-amp devresinin toplar yükselteç olarak kullanımı görülmektedir. Burada

op-amp eviren yükselteç olarak çalışmakta olup çıkış:

Vçk = (

Rf

R1

V gr1 +

Rf

R2

V gr 2 ) olarak yazılabilir.

Rf=R1=R2 seçilirse Vçk = V gr1 + V gr 2 olur. Burada (-) işaret op-amp'ın eviren yükselteç

olarak çalışmasından kaynaklanmaktadır.

Şekil 5.1

ÖN ÇALIŞMA:

1. Şekil 5.2’deki devrenin çıkışında kaç volt gözleriz. Hesaplayınız.

2. Aynı soruyu Şekil 5.3'deki devre için de cevaplayınız.

Şekil 5.2

Şekil 5.3

20

DENEYDE KULLANILACAK DEVRE ELEMANI VE CİHAZLAR:

1 adet 1 K direnç

1 adet 2,2 K direnç

3 adet 10 K direnç

2 adet 33 K direnç

Yeterince kasa devre elemanı

1 adet 747 op-amp

1 adet sayısal multimetre.

DENEY:

1. Devreyi Şekil 5.4'deki gibi kurunuz.

2. Güç kaynağının (+) ve (-) bölümlerini sırasıyla,+12 volta ve -12 volta ayarlayınız.

3. ±12 volt besleme gerilimlerini devreye uygulayınız. Sayısal multimetre kullanarak;

a) V gr1 , V gr 2 , Vçk gerilimlerini not ediniz. Vçk = V gr1 + V gr 2 oluyor mu?

b) Bulduğunuz sonucu, ön çalışma 1'de bulduğunuz sonuç ile karşılaştırınız.

4. Rf = 33 K yapınız. Sayısal multimetre kullanarak;

a) V gr1 , V gr 2 , Vçk gerilimlerini ölçüp not ediniz. Vçk = V gr1 + V gr 2 eşitliği hala geçerli mi?

Değil ise niçin? Açıklayınız.

b) Bulduğunuz sonucu, ön çalışma 2'de bulduğunuz sonuç ile karşılaştırınız.

Şekil 5.4

21

DENEYSEL ÇALIŞMA

----- 6 ----KONU:

Op-amp uygulaması olarak çıkartma yapan devreyi (difference amplifier) incelemek.

ÖN BİLGİ:

Şekil 6.1’de op-amp devresinin çıkartma işlemini nasıl yaptığına ait devre görülmektedir.

Devrede superpozisyon teoremi uygulandığında; Vgr1 'den dolayı

V ı çk = −

Rf

R1

V gr1 olur. V gr 2 'den dolayı;

V ıı çk = (V gr 2

R3

R

)(1 + F )

R 2 + R3

R1

V ıı çk = V gr 2 (

R3

R

)(1 + F )

R2 + R3

R1

Vçk = V ıı çk + V ı çk = −

Rf

R1

V gr1 + V gr 2 (

R3

R

)(1 + F ) olarak bulunur.

R2 + R3

R1

Şekil 6.1

Eğer R1=R2=R3=Rf ise: Vçk = V gr 2 − V gr1 olur.görüldüğü gibi dever girişine uygulanana

gerilimleri farkını almaktadır. R3=Rf ve R1=R2 olarak seçmek suretiyle, devreyi fark

yükselteci haline getirmek mümkündür. Örneğin, R3=Rf=100 K ve R1=R2=10 K ise devre

çıkışında giriş işaretleri arasındaki farkın 10 katı görülecektir.

ÖN ÇALIŞMA:

1. Şekil 6.2’deki devre çıkışı kaç volttur? Hesaplayınız.

2. Aynı soruyu, Şekil 6.3’deki devre içinde cevaplayınız.

22

Şekil 6.2

Şekil 6.3

DENEYDE KULLANILACAK DEVRE ELEMANI VE CİHAZLARI:

1 adet 2.2 K direnç

1 adet 5,6 K direnç

4 adet 10 K direnç

3 adet 33 K direnç

Yeterince kısa devre elemanı

1 adet 747 op-amp

1 adet sayisal multimetre.

DENEY:

1. Devreyi Şekil 6.4’deki gibi kurunuz.

2. Güç kaynağının(+) ve (-) bölümlerini sırasıyla, +12 volta ve -12 volta ayarlayınız.

3. ±l2 volt besleme gerilimlerini devreye uygulayınız.

4. Sayısal multimetre kullanarak;

a) V gr1 , V gr 2 , Vçk gerilimlerini not ediniz. Vçk = V gr 2 − V gr1 oluyor mu?

b) Bulduğunuz sonucu, ön çalışma l'de bulduğunuz sonuç ile karşılaştırınız.

5. R3=Rf=33 K yapınız. Sayısal multimetre kullanarak,

a) V gr1 , V gr 2 , Vçk gerilimlerini not ediniz

Vçk = V gr 2 − V gr1 hala geçerli mi? Değilse niçin? Açıklayınız.

b) Bulduğunuz sonucu ön çalışma 2'de bulduğunuz sonuç ile karşılaştırınız.

23

c) Devre fark yükselteci olarak çalışıyor mu?

Şekil 6.4

24

DENEYSEL ÇALIŞMA

----- 7 ----KONU:

Op-amp uygulaması olarak türevleyici (differentiator) devresini incelemek.

ÖN BİLGİ:

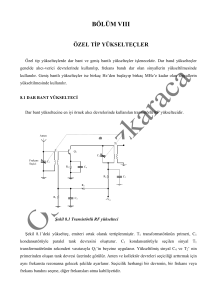

Türevleyici devresi, genel olarak bir eviren yiikselteç özelliğindedir (Şekil 7.l). Fark olarak

girişte direnç yerine kondansatör (Cgr ) bulunmaktadır. Devre, girişine Şekil 7.1 uygulanan

periyodik işaretin türevini alarak çıkışa aktarır. Bu işlem formüllerle, kısaca, şu şekilde

açıklanabilir. Op-amp devresinin giriş empedansı çok yüksek olduğundan X noktasındaki

gerilim yaklaşık, 0 volt (+ uçtaki gerilim) civarındadır. Buna göre; C kondansatörü

üzerinden akacak akım;

Igr =Cgr.dVgr/dt olur.

Şekil 7.1

Çıkış gerimi ise; Vçk = R f İ f olarak yazılabilir (X noktası yaklaşık 0 V olduğundan).

Vçk = − R f C gr

dV gr

dt

olacaktır. Görüldüğü gibi, Şekil 7.1’deki devre girişine uygulanan Vgr

işaretinin türevini alıp

dVgr

dt

belirli bir sabit ile (Rf Cgr) çarparak çıkışına aktarmaktadır.

Şekil 7.1'deki devre uygulamada bu haliyle yeterli değildir. Çünkü Cgr kondansatörü yüksek

frekanslardaki işaretlere kısa devre gibi davranacağından yükselticin kazancı artar, çıkış bu

frekanslar için yüksek değerlere ulaşır.Vgr işaretinin frekansı yüksek olmasa

bile

beraberinde görültü mevcut olabilir. Gürültü işareti çok geniş frekans tayfına sahip

olduğundan, Şekil 7.1’deki devre gürültünün yüksek frekans bölümü olduğu gibi

yükseltebilir. Bu ise istenmeyen bir durumdur. Bu nedenle op-amp devresi kazancına yüksek

25

frekanslar için bir sınır koymak gerekir. Bu işlem Şekil 7.2’de görüldüğü gibi bir Rgr

direncinin eklenmesi ile sağlabilir. Artık devrenin maksimum kazancı Rf/Rgr olarak

sınırlandırılmıştır.

Şekil 7.2

Bu devrenin türevleyici olarak çalışabilmesi için 2 koşulun sağlanması gerekir.

1. Giriş işaret frekansı; f gr ≤

1

= fc

2πR gr C gr

olmalıdır. Bu değerden frekansa sahip

frekanslar için devre türevleyici olarak çalışmaz.

2. Devrede Rf Cgr çarpımı ‘zaman sabitesi olarak isimlendirilir. Giriş işaretinin peryodu

yaklaşık bu değer civarında olmalıdır.

Örnek: Şekil 7.3’deki devre frekansı 1 KHz bir sinüsoidal işaret için türevleyici olarak

çalışabilirmi?

Şekil 7.3

fc =

1

1

10 4

Bu durumda fgr<fc olur.

=

=

2πR gr C gr 2π ∗ 10 3 ∗ 0,1 ∗ 10 −6 2π

Devrenin zaman sabitesi, C gr R f = 0,1 * 10 −6 * 10 * 10 3 = 1 msn

26

Giriş işaretinin peryodu, Tgr =

1

1

=

= 1msn .

f gr 1KHz

Görüldüğü gibi, giriş işaretinin peryodu, devrenin zaman sabitine eşittir. Şu halde, devre 1

KHz frekansı sinüsoidal işaret için türevleyici olarak çalışabilir. Şekil 7.3’deki devrenin söz

konusu işaret için türevleyici olarak çalışabileceğini kanıtladıktan sonra, devre girişine 0,5 V

genlikli ve 1 KHz frekanslı bir sinüsoidal uygulandığında çıkışta görülecek işaretin ne tip bir

işaret olduğunu araştıralım; Giriş işaretini,

V gr = 0,5 * sin 2πft

V gr = 0,5 * sin 2π (1000)t

olarak formülize etmek mümkündür.

Vçk = − RfCgr

dVgr

olduğuna göre

dt

Vçk = −(10 K )(0,1µF )

d

(0,5 sin 2π (1000)t )

dt

Vçk = −(10 K )(0,1µF )(0,5 * 2π * 1000)(cos 2π (1000)t )

Vçk = −3,14 cos 2π (1000)t olur.

Şu halde çıkış işareti, 3,14 V tepe değerli ve 1 KHz frekanslı bir cosinüs eğrisidir.

NOT:

d

sin 2π f t = 2π f cos 2 π f t olur.

dt

ÖN ÇALIŞMA:

1. Şekil 7.4’deki devre girişine, Şekil 7.5’deki işaret uygulandığında devre türevleyici olarak

görev yapar mı? fc ve fgr frekanslarını ve devre sabiti ile Tgr değerini karşılaştırarak bu

sonuçlara dayandırınız.

27

Şekil 7.4

Şekil 7.5

Şekil 7.4’deki devre girişine, Şekil 7.5’deki işaret uygulandığında çıkış işaretinin şekli,

frekansı ve genliği ne olur açıklayınız? Vgr ve Vçk işaretlerini alt alta çiziniz.

Yol Gösterme: Şekil 7.5’deki işaretin genel çizimi Şekil 7.6’da gösterilmiştir.

Şekil 7.6

Burada a b arasındaki doğru parçası t1 msn kadar süre içinde –V den + V’ye çıkmaktadır.

Denklemi Vab = −V + 2

V

* t olarak yazılabilir. Çünkü t=0 olduğunda Vab=-V t = t1

t1

olduğunda Vab= +V olmaktadır. bc arasındaki doğru parçası ise t1 ile 2t1 arasıda +V den

–V ye inmektedir.

Denklemi,

Vbc = +V − 2

V

(t − t1 ) olur. Çünkü, t = t1 olduğunda Vbc = +V

t1

t = 2t 1 olduğunda Vbc = −V olmaktadır.

V gr = Vab = −V + 2

Vçk = RF C gr

V

t olduğunda,

t1

d

V

(−V + 2 t )

dt

t1

28

V

Vçk = − RF C gr ( )

t1

Vçk = −2 RF C gr

V

olur.

t1

V gr = Vbc = +V − 2

Vçk = − R F C gr

V

(t − t1 ) olduğunda ise,

t1

d

V

(V − 2 (t − t1 ))

t1

dt

V

Vçk = RF C gr (−2 )

t1

Vçk = 2 RF C gr

V

olur.

t1

Buna göre Vçk işaretinin ( V gr ’in tamamı için) genliği, 2 RF C gr

V

olan bir kare dalga olacağı

t1

açıktır. Bu bilgilerin ışığı altında ön çalışma 2’yi cevaplayınız.

DENEYDE KULLANILCAK DEVRE ELEMANI VE CİHAZLARI:

1 adet 10 K direnç

Yeterince kısa devre elemanı

1 adet 10 nF kondansatör

1 adet 747 op-amp

1 adet işaret üretici

1 adet osiloskop

DENEY:

1. Devreyi Şekil 7.7’deki gibi kurunuz.

2. Güç kaynağının (+) ve (-) bölümlerini sırasıyla +12 V’a ve -12 V’a ayarlayınız. ± besleme

gerilimlerini devreye uygulayınız.

29

3. İşaret üretici çıkışını, Frekansı 1 KHz, Genliği 2 Vt −t olan bir üçgen dalgaya ayarlayınız.

4. Osiloskobun A kanalına giriş işaretini, B kanalına ise çıkış işaretini uygulayınız. Her iki

kanalı da; frekansı 1 KHz, genliği 1 volt olabilecek bir işareti en iyi şekilde görüntüleyecek

biçimde ayarlayınız.

5. İşaret üreteci çıkışını, devre girişine uygulayınız.

a) V gr ve Vçk işaretlerini birlikte gözleyip, aralarındaki farkları not ediniz. Devre türev alıcı

olarak çalışmışmıdır?

b) Vçk işaretinin tepe genliğini ölçüp net ediniz. Bu sonucu, ön çalışma 2’de bulduğunuz

sonuç ile karşılatırınız.

6. Girişi uygulanan üçgen dalganın genliği aynı kalmak koşuluyla frekansını yarıya

indiriniz. (0,5 KHz).

7. Çıkışta gözlediğiniz işarette ne gibi değişiklikler oldu? Bu değişiklikleri nasıl

açıklarsınız?

8. Girişe uygulanan üçgen dalganın genliği aynı kalmak koşuluyla frekansını 20 KHz

yapınız. Çıkış işaret şekli, öncekilere kıyasla değişti mi? Niçin? Devrenin gerilim kazancı ne

kadar? Bu kazanç Av =

RF 10 K

=

= 10 sonucuna yakın mı? Devre sadece eviren yükselteç

1K

R gr

gözüyle bakılabilir mi? Niçin? Açıklayınız.

Şekil 7.7

30

DENEYSEL ÇALIŞMA

----- 8 ----KONU:

Op-amp uygulaması olarak integratör devresini incelemek.

ÖN BİLGİ:

İntegratör devresi, genelde, girişine uygulanan işaretin integralini alır ve çıkışa aktarır. Bu

işlemi yapan bir op-amp devresi Şekil 8.1’de görülmektedir. Dikkat edilecek olursa,

türevleyici devresindeki direnç ve kondansatörlerin yerlerini değiştirmek suretiyle integratör

devresi elde edilmektedir. Bu devrede de x noktasındaki gerilim op-amp çıkış özelliğinden

dolayı, 0 V civarındadır.

Şekil 8.1

Bu durumda; İ gr =

1

Vçk =

CF

Vçk = −

V gr

R gr

yazılabilir.

t

∫İ

f

dt ve İ f = − İ gr olduğuna göre

0

1

CF

t

∫ İ gr dt = 0

t

1 V gr

dt

C F ∫0 R gr

t

1

Vçk = −

V gr dt

C F R gr ∫0

Olarak bulunur. Bilindiği gibi integral anlam olarak bir eğrinin altında kalan alana karşılık

gelmektedir. Op-amp devresindeki giriş ofset geriliminin giderek op-ampı doyuma

götürmesini önlemek için Şekil 8.1’deki devre de değişiklik yapmak gerekir. Bu değişiklik

31

Cf kondansatörüne paralel bir R1 direnci bağlanarak yapılır (Şekil 8.2). Giriş polarma

akımlarının eşit olmayışından doğacak ofset gerilimini ve dolayısıyla bu gerilimin etkilerini

gidermek amacıyla Şekil 8.3’te görüldüğü üzere R2 direnci kullanılır.

Şekil 8.2

Bu direncin değeri R2 = R1 // R gr

Şekil 8.3

R2 =

R1 R gr

R1 + R gr

olmalıdır. Devrenin bir integratör olarak

görev yapabilmesi için girişine uygulanan frekansı (fgr) f gr ≥ f c =

Ayrıca devrenin zaman sabitesi (

1

olmalıdır.

2πR1C f

1

) ile girişine uygulanan işaretin peryodu birbirlerine

R gr C f

yakın değerde olmalıdırlar. fgr<fc olduğunda devre eviren yükselteç olarak çalışır ve çıkışta

girişin

R1

kadar yükseltilmişi görülür. İntegral alma işlemi türev almanın tersi olduğundan

R gr

bir integratör girişine kare dalga uygulandığında çıkışta üçgen dalga elde edilir.

ÖN ÇALIŞMA:

1. Şekil 8.4’deki devre girişine Şekil 8.5’deki işaret uygulandığında devre integratör olarak

çalışır mı? fc ile fgr frekanslarını ve devrenin zaman sabiti ile Tgr değerini karşılaştırarak

cevabınızı bu sonuçlara dayandırınız.

2. Şekil 8.4’deki devre girişine Şekil 8.5’deki işaret uygulandığında çıkış işaretinin şekli,

frekansı ve genliği ne olur? Açıklayınız. Vgr ve Vçk işaretlerini alt alta çiziniz.

32

Şekil 8.4

Şekil 8.5

Yol Gösterme: 0 ile 0,5 msn arasında

t

Vçk = −

1

V gr dt

C F R gr ∫0

Bu bir −

Vçk = −

1

C F R gr

t

∫ İ dt

Vçk = −

0

1

t

R gr C f

1

eğimli doğru denklemidir ve tepe değerini t = t1 = 0,05 * 10 −3 sn anında alır.

R gr C F

−3

0 , 05*10

1

t

I = −0,5 V olur. 0,05 msn ile 0,1 msn

Bu durumda Vçk (tepe) = −

0

10 * 10 3 * 0,01 * 10 −6

arasındaki durum buna benzer şekilde hesaplanabilir.

DENEYDE KULLANILACAK DEVRE ELAMANI VE CİHAZLAR:

3 adet 10 K direnç

1 adet 100 K direnç

Yeterince kısa devre elamanı

1 adet 0,01 µF kondansatör

1 adet 747 op-amp

1 adet işaret üreteci

1 adet osiloskop

DENEY:

1. Deneyi Şekil 8.6’daki gibi kurunuz. Kurduğunuz devreyi öğretmenize kontrol ettiriniz.

2. Güç kaynağının (+) ve (-) bölümlerini sırasıyla +12V ve -12V ‘a ayarlayınız. ±12V

besleme gerilimlerini devreye uygulayınız.

3. İşaret üreteç çıkışını, Frekans 10KHz, Genliği 2V(t-t) olan bir kare dalga ayarlayınız.

33

4. Osiloskobunuzun A kanalına giriş işaretini B kanalına ise çıkış işaretini uygulayınız. Her

iki kanalıda frekansı 1KHz genliği 1V olabilecek işareti en iyi şekilde görüntüleyecek

biçimde ayarlayınız.

5. İşaret üretici çıkışını, devre girişine uygulayınız.

a) Vgr ve Vçk işaretlerini birlikte gözleyip aralarındaki farkları not ediniz. Devre integral

alıcı olarak çalışmıdır?

b) Vçk işaretinin tepe genliği ölçüp not ediniz. Bu sonucu ön çalışma-2’deki bulduğunuz

sonuç ile karşılaştırınız?

c) Vçk gerilimi 0V etrafında mı salınıyor? Niçin? R1=100K direncine paralel 10K

bağlayınız ne oldu? Niçin?

6. Girişe uygulanan kare dalganın genliği aynı kalmak koşuluyla frekansını 5KHz yapınız.

Çıkışta gözlediğiniz işarette ne gibi değişiklikler oldu? Bu değişiklikleri nasıl açıklarsınız?

7. Girişe uygulanan kare dalganın genliği aynı kalmak koşuluyla frekansını 50 Hz yapınız.

Çıkış işaret şekli öncekilere kıyasla değişti mi? Niçin? Devrenin gerilim kazancı ne kadar bu

kazanç Av =

R1 100

=

= 10 sonucuna yakın mı? Devreye artık sadece eviren yükselteç

10

R gr

gözüyle bakmak doğru olur mu? Niçin? Açıklayınız.

Şekil 8.6

34

DENYESEL ÇALIŞMA

----- 9 ----KONU:

Kıyaslayıcı (comparator) devesini incelemek.

ÖN BİLGİ:

Op-amp devresine dışarıdan geri besleme uygulanmadığı sürece kazancı çok yüksektir. Şekil

9.1’de Vgr ve Vref gerilimleri arasında çok küçükte olsa fark varsa bu fark op-ampın açık

devre kazancı( 20 000 civarında ) ile çarpılır ve çıkışa yaklaşık olarak +V ve –V görülür.

Şekil 9.1

Şekil 9.1’deki kıyaslayıcı, evirmeyen özelliktedir. Çünkü Vgr(+) uca uygulanmıştır.

Vgr>Vref olduğunda Vçk= + V ( yaklaşık ) Vgr<Vref olduğunda Vçk=-V (yaklaşık) olur.

Tersi durumda eviren kıyaslayıcı elde edilir. Eğer kıyaslayıcı devresi bir TTL devreyi

sürecek ise o zaman Şekil 9.2’de görülmektedir.

Şekil 9.2

Vgr>Vref olduğunda: Vçk= 5 V

Vgr< Vref olduğunda: Vçk=- 0.6 V olur.

Bu şekilde kıyaslayıcı çıkışı TTL devre girişine bağlanabilir. Deneylerde kullanılacak 747

op-amp devresinin maksimum dayanabileceği diferansiyel giriş ± 30V civarındadır. Buna

35

göre Vgr ile Vref arasındaki gerilim farkı hiçbir zaman 30 voltu aşmamalıdır. Örneğin

Vgr=18 V Vref=-18 V olması halinde op-amp hasara uğrar.

Kıyaslayıcı devresi A/D (analog to digital) çeviricilerde delta modülatörlerinde ve daha bir

çok alanda kullanılan önemli bir devredir.

ÖN ÇALIŞMA:

1. Şekil 9.3’deki devrede Vgr=0.8 V Vref= 0.7 V olduğuna göre Vçk gerilimini bulunuz.

Devre ne tür kıyaslayıcıdır?

Şekil 9.3

2. Aynı soruyu Zd diyotu nu yok varsayarak cevaplayınız.

3. R1, R2, R3 dirençleri niçin gereklidir?

DENEYDE KULLANILACAK DEVRE ELEMANI VE CİHAZLAR:

1 adet 270 Ω direnç

2 adet 1 K direnç

3 adet 10 K direnç

1 adet 33 K direnç

1 adet 10 K potansiyometre

Yeteri kadar kısa devre elemanı

1 adet 747 tümleşik op-amp devresi

1 adet 1N4002 diyot

1 adet BC238B transistör

1 adet led

1 adet 3 V zener

1 adet sayısal multimetre

36

DENEY:

1. Devreyi Şekil 9.4’deki gibi kurunuz. R1=R2=10K olmalıdır dikkat ediniz.

2. Besleme gerilimleri +12 V ve -12 V’a ayarlayınız.

3. Kurduğunuz devreye gerilim uygulayınız.

4. Sayısal multimetreyi DC gerilim ölçümüne hazırlatıp devre çıkışına bağlayınız.

5. P potasiyometresini saat yönü olarak sonuna kadar çeviriniz.

6. Vgr , Vref ve Vçk gerilimlerini ölçüp not ediniz. Durum kurumsal bilgilerle uyum içinde

mi? Devre evirmeyen kıyaslayıcı olarak mı çalışıyor?

7. Vçk gerilimi +12 V’luk kaynak gerilimine ulaşana kadar potansiyometreyi saat yönüne

ters olarak çevirininiz. Tam geçiş anındaki Vgr , Vref ve Vçk değerlerini kaydediniz.

Bu Vgr değerini ölçünüz. Bu değeri Vref ile kıyaslayınız. Durum kurumsal bilgilerle

uyumlu mu?

8. Devreyi Şekil 9.5’deki duruma getiriniz. R3= 10K olduğunda emin olunuz. Daha küçük

değer op-amp’ın yanmasına neden olur.

9. Vgr= 6 V ve Vref = 3 V için LED’in durumunu gözleyiniz. Bu devrede D diyotunun

görevi nedir? Devrenin çalışmasını kısaca açıklayınız.

10. Vref gerilimini hassas biçimde ölçüp not ediniz. Vgr gerilimini, Vref geriliminin 20 mV

üstüne ayarlayıp LED’in durumuna bakınız. Aynı işlemi, Vgr gerilimini Vref geriliminin

230 mV altına ayarlayıp yineleyiniz. Devre 20 mV’luk farkı dahi değerlendirebiliyor mu?

37

Şekil 9.4

Şekil 9.5

38

DENEYSEL ÇALIŞMA

----- 10 ----KONU:

PWM üretici SG3524 ile Buck (azaltan) çevirici devresini incelemek.

ÖN BİLGİ:

DA çeviricilerin en önemli uygulamaları anahtarlamalı güç kaynakları ve DA motor sürme

devreleridir. Bu uygulamada, DA çeviricinin anahtarlama sinyalleri darbe genişlik

modülasyonlu (PWM) çıkış sinyali üreten SG3524 entegresi ile sağlanmaktadır. Belli

frekanstaki bir sinyalin çalışma oranının (D) başka bir giriş sinyali ile kontrol edilmesi

olayına darbe genişlik modülasyonu denir. Çalışma oranı D Şekil 10.1’ de gösterildiği gibi

zamanının periyot uzunluğuna (Ts) oranı olarak tanımlanır.

Şekil 10.1

Değişik çalışma oranları bir Vs doğru geriliminin testere dişi bir dalgayla karşılaştırılması

ile elde edilir (Şekil 10.2).

Şekil 10.2

39

PWM üretici SG3524 ile Buck (azaltan) çevirici çalışma prensibi Şekil 10.3’de ve çalışma

oranı D %25 ve %75 iken PWM ve ortalama çıkış sinyalleri Şekil 10.4’de gösterilmektedir.

Şekil 10.3

Şekil 10.4

DENEYDE KULLANILACAK DEVRE ELEMANI VE CİHAZLAR:

1 adet 270 nF kondansatör

1 adet 1000 uF kondansatör

1 adet 1 K direnç

1 adet 10 K direnç

1 adet 100 uH bobin

1 adet 10 K potansiyometre

1 adet 22 K potansiyometre

Yeteri kadar kısa devre elemanı

1 adet SG3524 entegresi

1 adet BA158 diyot

1 adet BC516 transistör

1 adet sayısal multimetre

DENEY:

1. Devreyi Şekil 10.5’deki gibi kurunuz.

2. Besleme gerilimleri +12 V’a ayarlayınız.

3. Kurduğunuz devreye gerilim uygulayınız.

40

4. Sayısal multimetreyi ve osiloskobu DC gerilim ölçümüne hazırlatıp devre çıkışına

bağlayınız.

5. P1 ve P2 potansiyometresini çeviriniz.

6. Görev devrini (D) değiştirerek Vçk gerilimlerini ölçüp not ediniz ve osiloskop dalga

şekillerini çiziniz.

P1

P2

Şekil 10.5

Şekil 10.6. SG 3524 blok diyagramı (iç yapısı).

41

DENEYSEL ÇALIŞMA

----- 11 ----KONU:

Op–amp kullanarak hassas tam dalga doğrultmaç yapmak.

ÖN BİLGİ:

Hassas, tam dalga doğrultmaç devresi Şekil 11.1’de görülmektedir. Burada 1. op-amp hassas

yarı dalga doğrultmaç olarak, 2. op-amp ise toplar devre (eviren) olarak görev

yapmaktadırlar.

Şekil 11.1

Vgr işaretinin negatif alternansları doğrultulmakta ve pozitif olarak 1. op-amp çıkışına (V1)

aktarılmaktadır. Bu sırada op-amp’ ın gerilim kazancı 1’dir. 2.op-amp’ ın (-) ucuna hem Vgr

ve hem de V1 işaretleri birlikte gelmektedirler. Normal olarak, R4=2R5 seçilir. Böylece

Vgr’in pozitif alternanslarında V1=0’dır ve Vçk = -Vgr olur (R6=R4 seçilir). Vgr‘in

negatif alternanslarında ise, Vçk = - (2V1+Vgr ) olur (R6=2R5 olduğundan). Bu sırada

V1=Vgr olduğundan, Vçk= -(-2Vgr + Vgr) = Vgr olur. bu sırada Vgr negatiftir. Anlatılanlar

Şekil 11.2’de çizilmişlerdir inceleyiniz.

Şekil 11.2

42

ÖN ÇALIŞMA:

Şekil 11.3’deki devrede, D1 ve D2 diyotlarının yönleri çevrilirse çıkış işaretinden ne gibi bir

değişiklik meydana gelir? Kısaca açıklayınız.

DENEYDE KULLANILACAK DEVRE ELEMANI VE CİHAZLAR:

1 adet 2,2 K direnç

1 adet 4,7 K direnç

4 adet 10 K direnç

Yeterince kısa devre elemanı

2 adet BA158 diyot

1 adet 747 tümleşik op-amp

1 adet işaret üreteci

1 adet osiloskop

DENEY:

1. Deneyi Şekil 11.4’deki gibi kurunuz.

2. (+)ve (-) kaynakları +12 V ve –12V değerlerine ayarlayınız.

3. Kurduğunuz devreye (+) ve (-) gerilimleri aynı anda devrenize uygulayınız.

4. İşaret üretecinizin çıkışını 1 V (t-t) genlikli ve 500 Hz frekanslı bir sinüsoidala

ayarlayınız.

5. Osiloskobun A kanalına Vgr işaretini, B kanalına da V1 işaretini uygulayıp birlikte

gözleyiniz. Her iki kanal girişi de DC konumda olmalıdır. Vgr ve V1 işaretlerini, genlik

değerlerini de belirterek alt alta çiziniz. İlk op-amp yarım dalga doğrultmaç olarak çalışıyor

mu?

6. Osiloskobun B kanalından V1 işaretini ayırıp Vçk işaretini bağlayınız. Vçk işaretini Vgr

ve V1 işaretlerinin altına çiziniz.

7. Devre tam dalga doğrultmaç olarak çalışmış mıdır? İkinci op-amp eviren toplar yükselteç

olarak görev yapıyor mu?

43

8. Giriş işaretinin genliği 200 mV (t-t) değere düşürünüz. Devre hala tam dalga doğrultmaç

olarak çalışmakta mı? Bu kadar küçük genlikli AC işareti normal diyotlarla doğrultmaya

imkan var mı?

9. Giriş işaretinin genliği yeniden 1 V (t-t) yapınız. R5 direncini (1,5K’yı kısa devre ederek)

3,6 K yapınız. Vçk işaretinde meydana gelen değişikliği ve nedenini yazınız.

10. Devrenin ±12 V besleme gerilimlerini kesiniz. R5 direncini tekrar ilk değerine getiriniz.

11. D1 ve D2 diyotlarının yönlerini ters çeviriniz.

12. Tekrar ±12 V gerilimlerini devreye uygulayınız.

13. Vgr ve Vçk işaretlerini osiloskopta gözleyiniz. Dalgaların yönü pozitifleşti mi? Bu

durum ön çalışmada bulduğunuz sonuç ile uyum içinde mi?

14. Op-amp kullanılan yarım ve tam dalga doğrultmaçlar çok küçük genlikli AC işaretlerini

doğrulta bildiklerine göre; Sayısal multimetreler de bu tip devreler kullanılır mı?

Şekil 11.4

44

DENEYSEL ÇALIŞMA

----- 12 ----KONU:

Op-amp kullanarak gerilim regülatörü yapmak ve çalışmasını incelemek.

ÖN BİLGİ:

Op-amp kullanılarak çok çeşitli gerilim regülatörleri yapmak mümkündür. Şekil 12.1’de

böyle bir devre görülmektedir. Devrede regüle edilecek gerilim Vgr olarak op-amp’ın (+V)

ucuna uygulanır. Op-amp (-V) ucu toprağa bağlanır. Şu halde, bu devrede tek polariteli

besleme gerilimi kullanılmaktadır. Vgr gerilimi devreye uygulandığında Vçk işareti

pozitifleşmeye başlar. Vçk<Vz olduğu sürece zener diyot yalıtkandır.

Şekil 12.1

Vçk>Vz olunca zener diyot iletkenleşir ve kırılma gerilimine eşit bir gerilim x noktasında

oluşur. ( V REF = V z olur). Artık bundan sonra op-amp’ın pozitif girişine sabit V REF gerilimi

uygulanmaktadır.

Vçk = V REF (1 +

Bu

sırada

op-amp

evirmeyen

yükselteç

olarak

çalıştığından;

R2

) olur. Bu durumda hem Vçk ve hem de Vz gerilimleri regüleli

R1

olduklarından Zd içinden akan akım oldukça kararlıdır. Bu durum, hep Vref’in ve

dolayısıyla da, Vçk’ın kararlı olmasına yol açar. R2 ve R1 dirençleri ile Vçk gerilim

değerini ayarlamak mümkündür.

ÖN ÇALIŞMA:

Şekil 12.1’deki devrede Vz=3 V R2=2,2 K, R1=3,3 K, R3=370 Ohm olduğuna göre Vgr’in

10 ile 20 V arasında değişmesi sırasında Vçk ne değer alır? Zener içinden aka akımı

hesaplayınız.

45

DENEYDE KULLANILACAK DEVRE ELAMANI VE CİHAZLARI:

1 Adet 100 ohm direnç

1 Adet 270 ohm direnç

1 Adet 2,2 K direnç

1 Adet 3,3 K direnç

2 adet 33 K direnç

1 adet 3 V zener

Yeterince kısa devre elamanı

1 adet 747 tümleşik op-amp deversi

1 adet sayısal multimetre

DENEY:

1. Devreyi Şekil 12.2’deki gibi kurunuz.

2. Güç kaynağını çıkışını +12 V’a ayarlayınız.

3. Rk1=Rk2=33 K dirençleri devre girişlerini korumak için konumlulardır. Doğru

bağlandıklarını kontrol ediniz.

4. Kurduğunuz devreye gerilim uygulayınız.

5. Sayısal multimetre ile Vçk gerilimini ölçünüz. Sonucu Tablo 12.1’de ilgili haneye not

ediniz.

6. Tablo 12.1’de verilen diğer Vgr değerlerini sıra ile oluşturup her seferinde Vçk gerilimini

ölçünüz. Sonuçları Tablo 12.1’de ilgili hanelere yazınız.

7. Tablo 12.1’deki sonuçlara göre;

a) Örnek 1’deki devre çıkışında, geriş 10 V ile 20V arasında değişirken sabit gerilim

görülüyor mu?

b) Bu durumda devre gerilim regülatörü olarak görev yapmış mıdır?

c) Vçk geriliminin değerini ön çalışmada bulduğunuz değer ile karşılaştırınız. Fark varsa, bu

neden kaynaklanmaktadır? Ölçüm yaparak kanıtlayınız.

R1 = 2,2 K yaparak

R2

oranını büyültünüz.

R1

46

Bu durumda Vçk gerilimi ne oldu? Bu gerilimdeki artışın 2 nedenini yazınız. Cevabınızı

ölçüm yaparak kanıtlayınız.

Tablo 12.1

Vgr(V)

10

12

16

18

20

Vçk(V)

Şekil 12.2

47

DENEYDE KULLANILAN OPAMP BACAK BAĞLANTILARI

LM747

LM741

48

ELK 435 ENDÜSTRİYEL ELEKTRONİK LABORATUVAR

DENEY ELEMANLARI LİSTESİ

OPAMP (2’şer adet)

LM 741

LM 747

SG 3524 Entegre (1 Adet)

DİRENÇ

100 Ω (2 ADET)

270 Ω (2 ADET)

1 K; (3 ADET)

2.2 K; (3 ADET)

4.7 K; (3 ADET)

5.6 K; (3 ADET)

10 K; (10 ADET)

33 K; (4 ADET)

100 K; (3 ADET)

470 K; (3 ADET)

KONDANSATÖR (2’şer ADET)

10 nf

100 nf

1000 µF (1 adet)

BOBİN (1 ADET)

100 µH

DİYOT (2’şer ADET)

3V Zenerdiyot

1N4002 diyot

BA158 diyot

TRANSİSTÖR (1’er ADET)

BC516

BC238

POTANSİYOMETRE (1’er ADET)

10 K

22 K

49

ELK 435 ENDÜSTRİYEL ELEKTRONİK LABORATUARI DENEY RAPORU

İstenenler (devamı arka sayfaya)

CH1 (Volt/Div):

CH2 (Volt/Div):

Time/Div:

CH1 (Volt/Div):

CH2 (Volt/Div):

Time/Div:

Sonuçlar:

No

Deneyin

Adı

No

Öğrencinin

Adı Soyadı

Aldığı Not

OPAMPLAR

OPERASYONEL KUVVETLENDİRİCİLER

Fairchild 1965 yılında, en çok kullanılan Ua709 elemanı piyasaya sunmuştur. Aslında başarısının

yanında, bu elemanın birçok dezavantajları da vardı. Bu nedenle de uA741 olarak bilinen op-amp

geliştirilmiştir. UA741 çok ucuz ve kolay kullanımı, ayrıca üstün yetenekleri nedeniyle tercih edilmiştir.

Değişik firmalar da uaA741 dizaynlarını gerçekleştirmişlerdir. Örneğin Motorolo MCI741 National

Semiconductor LM741 ve Texas Instruments SN72741 üretmişlerdir. Bütün bu (monolithic) tek

elemanlı işlemsel kuvvetlendiriciler uA741’in eşdeğerleridir. Çünkü bunlar katologlarda da aynı

özelliklere sahiptirler. Çoğunlukla insanlar opamp’tan bahsediyorlarsa akıllarına gelen ilk eleman 741

olmaktadır.

741 elemanı endüstri standartlarına uygun hale getirilmiştir. Kural olarak yapacağınız dizaynlarda opamp kullanılmışsa bunların yerine 741 olarak devreyi kurabilirsiniz. Op-amp olarak 741’in kullanımını

anlamışsanız diğer opampları da kolaylıkla kullanabilirsiniz.

Sırası gelmişken 741 farklı versiyon numaralarına sahiptir. 741, 741A, 741C, 741E, 741N, ve

diğerleri... Bu farklılıklar bunların gerilim kazançları, sıcaklık farklılıkları, gürültü seviyeleri ve diğer

karakteristikleridir. 741C ( Ticari tipte bir elemandır.) çok ucuz ve çok geniş alanlarda kullanılmaktadır.

Bunun giriş empedansı 2M, gerilim kazancı 100.000 ve çıkış empedansı 75 ’dur.

741’İN ŞEMATİK DİYAGRAMI

Şekil 15-1, 741’in basitleştirilimiş şematik diyagramını göstermektedir. Bu devre 741’in eşdeğer devresi

olup sonradan üretilen op-ampların temelini teşkil eder.

Devre dizaynlarında her türlü ayrıntılı özellikleri anlamaya ihtiyaç yoktur. Fakat op-amp’ın nasıl

çalıştığı hakkında genel bir fikre sahip olabilirsiniz. 741’in ardındaki temel düşünce şudur:

Giriş katı Q1 ve Q2 PNP transistörlerinden oluşturulumuş bir fark kuvvetlendiricidir. Bildiğiniz gibi

emiterdeki bağlantı elemanları nedeniyle bu devre, akım kaynağı olarak çalıştığı farz edilmiştir. 741’in

içinde Q14 akım kaynağı olup emiter direnci yerine geçmektedir. R2 ve Q4’ün polarmasını kontrol ederek

fark kuvvetlendiricinin akımını üretir. Fark kuvvetlendirici de kollektör direnci yerine normal direnç

kullanarak bunu yük direnci yerine kullanabiliriz. Bu aktif yük Q4 için oldukça yüksek empedanslı bir

akım kaynağı olarak çalışır. Bu sebepten fark kuvvetlendiricinin gerilim kazancı daha büyük olmaktadır.

Beyz DC Dönüş Elemanları

Şekil 15-1’de görüldüğü gibi giriş beyzleri boşluktadır. İşlemsel kuvvetlendirici her iki girişe beyz

dirençleri RB ve toprak arasındaki DC bağlantılar yoksa çalışmayacaktır. Bu dönüş yolları işlemsel

kuvvetlendiriciyi süren devrenin, Thevenin dirençleri tarafından temin edilir. Eğer sürücü devreler

kapasitif kublajlı ise mutlaka beyz dönüş dirençlerine ihtiyaç vardır. Bu düşüncenin anahtarı her giriş

için beyzden toprağa bir bağlantı olmalıdır. Eğer beyzden toğrağa da bir yol yoksa op-ampın

transitörleri kesimde olacaktır.

GİRİŞ EMPEDANSI

Fark yükselticinin giriş empedansı şu şekilde ifade edilir.

Rgiriş = 2re

Fark yükselticideki ortak emiterli bağlantı nedeniyle işlemsel kuvvetlendirici oldukça yüksek giriş

empedansına sahiptir. Örneğin 741’in giriş fark kuvvetlendirici (tail) akımı yaklaşık olarak 15uA’dir.

Her emiter bu akımın yarısını üzerinden akıtır.

25mV

ré= _______________= 3.33 k

7,5uA

741’de girişteki her transistörün ’sı tipik olarak =300 olduğuna göre giriş empedansı:

ri= 2 (300) . (3,3K) = 2m

Bu 741’in kataloglarında tesbit edilen giriş direnci değeridir.

Eğer daha yüksek giriş empedansları gerekiyorsa dizayn yapan kişi BIFET (fetgirişli) op-amp kullanma

zorunluluğu vardır. Bu op-amp fet’in ve bipolar transitörlerin bir araya getirilmesiyle oluşturulmuştur.

Örneğin LF12741-741 olarak modife edilmiş JFET kaynak takip edicinin çıkışı normal 741 op-amp

sürmektedir. Bu kombinasyon 741 diğer karakteristikleri ile JFET kaynak takip edici giriş avantajlarını

meydana getirmektedir. Bu sebepten LF13741 standart 741 için yedek olarak kullanılabilir.

ŞEMATİK SEMBOLLER

Bir op-ampın şematik sembolü Şekil 15-2 de görülmektedir. A op-ampın gerilim kazancıdır. Faz

terslemeyen giriş V1, farz tersleyen giriş ise V2’dir Fark girişi

Vgiriş = V1 - V2

V1, V2 gerilimleri ve çıkış gerilim noktalarına dikkat ediniz. Bunun anlamı ölçümlerin daima toprakla

bu noktalar yapılmasıdır. Fark girişi Vgiriş iki giriş gerilimi V1, V2 arasındaki farktır.

Biz çoğu zaman Şekil 15-2 de görülen toprak hattını çizerek göstermeyiz. Bunun anlamı toprak noktası

olmasa da ölçülen değerlerin toprağa göre olmasıdır.

Vçıkış = A . Vg,iriş

Vçıkış

Vgiriş = ________________________

A

741 için A= 100.000 dir ve çıkış empedansı Zçıkış = 75 ’dur. Genellikle opampın çıkışına bağlanan

yük direnci Zçıkış ‘dan küçüktür. Vçıkış yaklaşık olarak Vth = Vçıkış değerine eşittir.

Örnek 15-1

Bir 741 giriş gerilimi 1uv’tur. Bu opampın çıkışındaki gerilim ne kadardır?

Çözüm

Giriş gerilimini, gerilim kazancı ile çarptığımızda 741C’nin kazancı 100.000 olduğuna göre çıkış

gerilimi:

Vçıkış = 100.000 . (1uV)= 0.1V

Bu cevaptan op-amp çıkışına yük direnci bağlanmadığı farzedilmiştir.

Eğer yük direnci kullanılmış ise Thevenin çıkış geriliminin bir kısmı bu yük üzerinde düşecektir. Eğer

yük direnci op-amp çıkış direnci değerinden 100 defa daha fazla ise çıkış direnci üzerinde meydana

gelen gerilim düşümünü ihmal edebilirsiniz. 741C’nin çıkış empedansı 75 olduğuna göre yük direnci

7,5 k’dan büyük ise yükleme etkisi dikkate alınmayabilir.

Örnek 15-2

Bir 741C’nin çıkış gerilimi 5V ise kazancı 100.000 olan op-ampın giriş gerilimi ne kadardır.

5V

Vgiriş = ________________ = 50 uV

100.0000

OP-AMP KARAKTERİSTİKLERİ

Op-amp bir yükselticidir. Ancak problemlerin analizinde ve op-amp devrelerinin dizaynlarında AC ve

DC karakteristikleri gözönünde bulundurmamız gerekmektedir. Bu bölümde, ofset problemlerine ve opampın performansını etkileyen diğer karakteristikler açıklanacaktır.

ÜÇ ÖNEMLİ KARAKTESTİK

Daha evvel (CMRR) sinyali bastırma oranı tanımlanmıştı. 741C için CMRR= 90 Db düşük frekanslar

için uygundur. Common mode sinyalinde arzı edilen sinyal 90Db daha büyüktür. Bunun anlamı

yükseltilecek sinyal ortak gürültü CMRR’nin Şekil 18-15’da görüldüğü gibi azalmasına neden olur.

Dikkat edilirse CMRR yaklaşık 1KHz’de 75db, 10 KHz’de 56db’dir.

Maksimum tepeden tepeye değeri yükselticinin çıkışından kırpılmadan alınan en büyük değerdir. Opampın girişinde herhangi bir sinyal yoksa çıkış ideal olarak sıfırdır. AC çıkış gerilimi pozitif ve negatif

yönde salınım yapar. Yük direncinin Zçıkış empedansından büyük olması halinde çıkış gerilimi besleme

geriliminde salınım yapar. Örneğin VCE = + 15 V ve V ve VEE = - 15 V olan devrede 10 k’luk yük

direnci uçlarındaki gerilim 30 V olacaktır. Ancak bu gerilim 741C’nin çıkış katından dolayı genelde

27V ve 10 k yük direncinde 27V, 1 k’luk yük uçlarında 25 V ve 100 yük uçlarındaki gerilim ise 7

V kadar olacaktır.

FREKANS TEPKİSİ

741C’nin Şekil 15-5c’de küçük sinyal frekans tepkisi görülmektedir. Orta bandın gerilim kazancı

100.000’dir. 741’in kritik frekansı fc= 10 Hz’dir Şekilde görüldüğü gibi 10 Hz seviyesinde gerilim

kazancı %70 kazanç değerini -3 db noktasından düşmektedir. Kritik frekansın üzerinde gerilim kazancı

her dekat artışı için 20 db düşmektedir.

Gerilim kazancının bire düştüğü frekans 1 MHz’dir. Kataloglarda bu değer genellikle belirtilir. Çünkü

bu değer op-ampın faydalı kazanç üst değerini temsil etmektedir. Örneğin kataloglarda 741C listelerinde

f1= 1 MHz. Bunun anlamı 741C sinyali 1 MHz kadar yükselir. Bunun üzerindeki değerlerde çıkış

azalmaya başlar. Örneğin LM318’in f1 = 15 MHz’dir. Bunun anlamı op-amp 15 MHz’e kadar çıkışında

kazanç verebilir. Bunun üzerindeki değerlerde çıkış azalarak gider.

YÜKSELME HIZI BOZULMASI ( Slew Rate )

Bir 741’in kompanzasyon kapasitesinden dolayı fark yükseltici çıkışı verilen slew rate değerinden daha

hızlı değişemez.

It

Sr = ________________

Cc

Bir 741C’de It = 15 mA ve Cc = 30 pF’tır. Bu sebepten 741’in slew rate yükselme hızı,

15 mA

Sr = _____________= 0,5 V/us’dir.

30 pF

Bu 741C’nin büyük sinyal sınırıdır. Bunun çıkış gerilimi 0,5 V/us’den daha hızlı değişmez.

Bildiğimiz gibi bir op-ampın yükselme hızı (slew rate) büyük sinyal yüksek frekans tepkisi sınırlar. Eğer

sinüs dalganın yükseltilmesindeki başlangıç eğitimi op-ampın yükselme hızından daha büyük ise çıkış

küçülmeye başlar ve girişteki sinüsodial dalga üçgen olarak görülmeye başlar. Daha evvel biz bu

eşitliği güç band genişliği olarak ifade ettik.

Sr

fmax = ___________

2n Vp

Bu yüksek frekansta yükselme hızı oranında bir bozulma olmadan 2n değerine bölünerek elde edilen

tepe geriim değeridir. Faydalı olan alternatif eşitlik:

Sr

Vp = _______________

2n fmax

Örnek 15-3

Şekil 15-6, 741C’nin ayak numaralarını göstermektedir. 3 Nolu giriş faz çevirmeyen giriştir. 7 ve 4 nolu

ayaklar güç kaynağı bağlantılarıdır. 6 nolu ayak ise çıkıştır. Bir 741C’nin en kötü şartlar altında

kataloglarda verilen değerleri

VBE = 2 mV, lgiriş = 80 nA ve Igiriş = 20 nA

En kötü durumdaki istenmeyen giriş gerilimi toplamı nedir? Çıkış ofset gerilimi nedir?

Çözüm

İstenmeyen giriş geriliminde iki farklı kompanent vardır. Önce farklı VBE eğrilerini etkileyen faktör.

İkinci olarak farklı ’da değerleri iki beyz gerilimini 3 ve 2 nolu ayaklardaki farkını transfer

etmektedirler.

Vgiriş = +2mV +(20nA) . (220 k) = +6.4mV

Bunun anlamı istenmeyen giriş gerilimleri - 6,4 mV ile + 6.4 mV arasında herhangi bir yerde olabilir.

En kötü durumda bunun büyüklüğü 6.4 mV olabilir.

741C lineer bölgede çalışıyorsa ve onun gerilim kazancı 100.000’dir. Buna göre ofset gerilimini

hesaplayacak olursak

Vçıkış = 100.000 (+ 6.4 mV) = +640V

Bu cevap saçmalık örneği olarak ve azaltılması gereken bir değer olarak gözönüne alınmalıdır. Çünkü

640V imkansızdır.

Bu saçma sonuçtan sonra şunu söyleyebiliriz: Sonuçta op-amp doyuma ulaşmıştır ve op-amp lineer

bölgede çalışmaktadır ve bu doğrudur.

Oysa bir 741C’nin maksimum (tepe to tepe) tepeden tepeye vereceği çıkış +27 V olabilir. Yani -13,5 V

ile +13,5 V volt arasında salınım yapar. Giriş gerilimi +6,4 V olduğu zaman op-ampın çıkışı 13,5 V’ta

gider. Giriş gerilimi olduğu zaman çıkış -13,5 V’ta gider.

Örnek 15-4

Bir önceki örnekte kullanılan katalog bilgilerini kullanarak op-amp çıkışını doyuma götürecek ofset giriş

gerilimini bulunuz.

Çözüm

Pozitif taraftan bakılacak olursa op-amp +13,5 V doyuma ulaşmadan (swing) salınım yapılacaktır. Opamp kazancı 100.000 olduğuna göre giriş gerilimi

13,5 V

Vgiriş =_______________=0,13 mV

100000

Bu en kötü durum olarak ifade edilen değerden 6,4mV’tan çok küçüktür.

Örnek 15-5

Bir 741C’nin yükselme hızı 0,5 V/usn’dir Çıkış gerilimi tepe değeri 10 V ise band genişliği nedir?

Çözüm

Yükselme hızında bir bozulma olmadan hesaplanan maksimum değer

0,5 V/us

fmax = ________________=7,96 kHz

2n . 10V

Bu frekansta op-amp bozulmamış sinüsodial çıkış sinyali tepe değeri 10V’tur. Eğer giriş frekansını 7,96

kHz’in üzerine çıkarırsanız çıkıştaki değerde bir azalım başlar. Girişin sinüsodial olmasına karşın

çıkışta üçgen dalgalar görülmeye başlar.

Örnek 15-6

50 kHz’lik giriş sinyallerinde çıkışta alınan sinyallerin bozulmadan alınabilecek değeri nedir?

0,5 V/usn

VP = _______________=1,59 V

2n . (50 kHz )

Bunun anlamı op-amp frekansı 50 kHz ve giriş sinyalinin tepe değeri 1,59 V olan sinyalin çıkıştan

bozulmadan alınabilir demektir.

ENTEGRE DEVRELERİNİN DİĞER LİNEER KULLANIMLARI

Aslında op-amplar çok önemli entegre devreleridir. Onları birçok değişik kullanımlar için

genişletebilirsiniz. Burada birkaç kullanım özet olarak verilmiştir.

SES YÜKSELTİCİLER

Ön yükselticiler çıkış gücü 50mW’tan daha az olan bu ses yükselticilerdir. Ön yükselticiler oldukça

düşük gürültü seviyesine sahip olmalıdırlar. Çünkü bunlar ses sistemlerinin girişinde kullanılmakta

olup, manyetik band kristallerden ve mikrofonlardan gelen zayıf sinyalleri yükseltmektedir.

Entegre edilmiş ön yükselticiye örnek LM381 düşük gürültülü çiftli bir ön yükselticidir. Her bir

yükseltici birbirinden tamamen farklıdır. LM381’in gerilim kazancı 112 db’dir ve 10V’da güç band

genişliği 74kHz ve 9V’tan 40V’ta kadar pozitif besleme ile çalışır. Giriş empedansını 100 k, çıkış

empedansı 150 ’du. Lm381’in giriş katı, fark kuvvetlendirici olup tekli çıkışa sahiptir.

Ses güç yükselticiler çıkışlarından 500 mW’tan fazla güç alınmaktadır. Bunlar phonograph yükselticiler

AM, FM radyolar ve diğer kullanımları bulunur. LM380 bir örnektir. Bunun gerilim kazancı 34db band

genişliği 100 kHz ve çıkış gücü 8W’tir.

Video Yükselticiler

Bir video veya geniş band yükseltici geniş bir frekans bandında sabit gerilimi kazancı düz bir tepki

gösterir. Tipik olarak band genişliği MHz bölgesindedir. Video yükselticilerde DC yükselticiler gerekli

değildir. Fakat çok düşük frekanslarda çok yüksek frekanslara kadar (range) değere sahiptirler. Örneğin

bir çok osilaskoplarda frekans değeri 0’dan 100-MHz’e kadar gider. Bu tür cihazlarda video

yükselticiler kullanılması sinyal genliğini arttırır. Diğer bir örnek televizyon alıcılarıdır. Kullanılan

frekans yaklaşık 0’dan 4MHz’e kadardır.

RF ve IF Yükselticiler

Bir radyo frekans ( RF) yükseltici TV alıcılarında veya AM-FM alıcılarda umumiyetle ilk kattır. Orta

frekans (IF) yükselticilerde tipik olarak orta katlardadırlar. Entegre devreler LM703 RF ve IF

yükselticiler aynı chip içinde bulunurlar. Yükselticiler ayarlı yapılmak suretiyle yalnız dar band

frekansında kullanılabilirler. Bu televizyon ve radyo istasyonlarının arzu edilen sinyallerinin alınmasına

(tuning) ayar devreleri ile mümkün kılar. Daha evvel bahsedildiği gibi büyük kondansatör ve self

değerlerinin chip içine yerleştirilememesi nedeniyle dışarıdan LS ve CS elemanlar ayar yükselticilerine

bağlanırlar.

GERİLİM REGÜLATÖRLER

Bölğm 4’te doğrultmalı güç kaynakları açıklanmıştı. Filtre işleminden sonra DC gerilimde biraz daha

riplle kalmaktadır. Bu DC gerilim hat gerilimi ile orantılıdır. Hat gerilimi %10 değişirse bu da seviye de

%10’luk değişmeye sebep olur. Birçok uygulamalarda %10’luk değişme DC gerilim değeri oldukça

fazladır ve bu sebepten DC regülasyon gereklidir.

Yeni entegre devrelerde LM340 serileri bu iş için kullanılmaktadır. Bu tipte chipler çıkış DC gerilimini

%0,01 olarak hat geriliminin ve yük direncinin değişmesini tutarlar. Diğer bir özellik olarak pozitif ve

negatif ayarlanabilen çıkış gerilimleri ve kısa devre koruma sağlarlar.

OP-AMPLARIN TEMEL KULLANIMLARI

İşlemsel kuvvetlendiriciler terim olarak analog bilgisayarların alan örneklerindendir. Bu tipteki

yükselticiler matematiksel işlemlerin, toplama, çıkartma, çarpma, bölme, integral, türev ve logoritma

alma gibi uygulamalarında başarılı bir şekilde kullanılmışıtır. Aslında op-amplar çok geniş bir alanda

kullanılmalarına karşın hala orijinal isimleri kullanılmaktadır.

Temelde op-amp yüksek gerilim kazancı DC fark kuvvetlendiriciler olup aşağıdaki karakteristikleri

taşımaktadır.

Sonsuz band genişliği,

Sonsuz giriş empedansı,

Sıfır çıkış empedansı,

Şekil 15-8 a’da görülen op-amp (+) pozitif noninvert ve (-) negatif invert girişli ve tek çıkışa sahiptir.

İlave olarak op-amp normalde çift kaynaklı + 5 V’dan + 18V’a kadar gerilim uygulanan bir elemandır.

Tek besleme kullanıldığında + 5 V’dan +15 ve -5 V’dan -15V’a kadar toprakla arasında bağlantı

yapılan bir beslemeye sahiptir

Aslında op-amp tek bir pozitif polarite ile de beslenebilir. Ancak, op-ampların daha çok çift kaynakla

beslemek adet olmuştur. Şekillerde besleme uçları bağlantı gösterilmeden görebilirsiniz.

Daha evvel bahsedildiği gibi op-amp iki girişi sahiptir. Bu iki giriş arasındaki fonksiyon fark aşağıda

izah edildiği gibidir.

Eğer sinyal op-ampların (+) noninvert girişine uygulanmış ise çıkış girişte aynı fazda olacaktır. Giriş

sinyali pozitife gittiği zaman çıkışta pozitife gider.

Eğer sinyal op-ampların (-) girişine (invert) uygulanmış ise çıkış 180 C faz farklı olarak veya yarım

saykıl olarak çıkacaktır.

Bunun anlaöı giriş sinyali pozitife gittiği zaman çıkış negatife gider veya girişin tersi olan çıkış alınır.

Şekil 15-10’da görülüyor. Bu bölümde op-amp devrelerin aktif olarak ve geri besleme elemanları ile

çıkış sinyalinin giriş sinyaline göre nasıl değiştiğini, op-amp karakteristikleri üzerinde duracağız.

TERSLEYİCİ YÜKSELTİCİ

Op-ampın bir tersleyici yükseltici olarak kullanımı Şekil 15-11 deki bağlantısında görülmektedir.RA ve

RB geri besleme elemanı olarak isimlendirilir. Bu devre için her iki elemanda dirençtir. Giriş

topraklanmıştır. RB direnci çıkış geriliminden geri besleme olarak tersleyici girişine bağlanmıştır. RA ve

RB terimleri çıkış geriliminin saptanmasında kullanılır.

RB

Vçıkış = ___________________ . Vgiriş

RA

Sonuç olarak gerilim kazancı, çıkış geriliminin giriş gerilimine oranıdır.

Vçıkış

RB

Gerilim kazancı = ___________=__________

Vgiriş

RA

GERİLİMİ TAKİP EDİCİ

Gerilim takip edici bazen tampon emiter takip edici veya katod takip edici ile aynı fonksiyona sahiptir.

Bu sebepten oldukça yüksek giriş empedansı ( 100 k’dan büyük ) ve çok düşük çıkış empedansı ( 750

’dan küçük ) değere sahiptir.

Gerilim takip edici faz terslemeyen yükselticiye benzemekte ancak, RA= Sonsuz ve RB = 0 bu sebepten

de gerilim kazancı daima eşittir.

TOPLAMA YÜKSELTİCİSİ

İki veya daha bağımsız giriş sinyalini toplamak istiyorsak toplama yükseltici devresini Şekil 15-14’de

kurmak gerekmektedir. Bu devre tersleyici yükseltici devreye iki girişi hariç V1 ve V2 aynıdır.

Gerilim kazancı her giriş için geri besleme RB direnci ile giriş direnci tarafından sağlanır.

Vçıkış

RB

Gerilim kazancı A = _________=___________

V1

R1

Vçıkış

RB

Gerilim kazancı AV = ___________=______________

V2

R2

Böylece çıkış gerilimi,

RB

RB

Vçıkış = ________________ . V1 + __________________ . V2

R1

R2

Daha faydalı devre, Şekil 15-14’da görülen devredir.

Aslında bu devre biraz daha karmaşık görülmektedir. Analiz oldukça basit olup, bu bölümde

öğrendiklerimizle halledebiliriz. Önce V3 noktasının toprağa kısa devre olduğunu farz edelim. Bu

durumda, devreniz toplama devresidir. Şekil 15-14’de görüldüğü gibi toplama yükseltici çıkış gerilimi

eşitliğinde verilmiştir.

İkinci olarak giriş sinyalleri V1 ve V2 toprağa kısa devredir. Şimdi de bir faz terslemeyen yükseltici

olup R1 ve R2 dirençleri paralel duruma getirmişti,r. Bu ifade Şekil 15-14’de RA olarak görülmektedir.

R1 . R2

RA= __________________

R1 + R2

Gerçek faz terslemeyen giriş gerilimi ki op-amp V3 görür ki gerilim bölücü eşitliğinin V3 ile ilişkisidir.

R4

V3= ______________ . V3

R3 + R4

Faz terslemeyen çıkış gerilimi eşitliğinden,

RF

Vçıkış = (1 + ______________ ) V3

RA

Daha evvelki eşitlikleri nazarı dikkate alırsak;

R1.R2.RF.R1+R1.R2

R4

Vçıkış = (_________________________________) ( __________________________) V3

R1 . R2

R3+R4

İNTEGRAL

Tersleyici yükseltici devrenin geri besleme direncinin bir kondansatörle değiştirilmesi Şekil 15-15 ‘daki

İntegral devresi oluşturulmuş olur.

Giriş sinyali integral eğrisinin altındaki alanı temsil etmektedir. Çıkış gerilimi aşağıdaki eşitlikle

verilmiştir.

1

Vçıkış = _____________________ Vgiriş. DT

RA. C0

1

________ terimi en küçük giriş frekansı beklenen değere uygun olmalıdır. Böylece ;

RA. C

1

RA . C = _____________________

2n Fmin

İntegral sonuç olarak çıkışta ofset gerilimi yaratılmasına sebep olacaktır. Bunun sebebi de beyz akım

ofsetidir.

Çıkış ofset gerilimini minimuma indirebilmek için faz terslemeyen girişe RA değerinde bir dirençle

toprağa bağlantı yapılır.

TÜREV DEVRESİ

İntegral devresi olarak kullandığımız şemada girişe kondansatör çıkışa ise direnç ilave ettiğimizde yani

integral devresindeki dirençle kondansatörü yer değiştirdiğimizde elde edilen devre türev devresidir.

Türev çıkışı giriş sinyalinin türevi ile orantılıdır. Görülen devrede F= 2000 Hz, 2.5 V, üçgen dalga çıkış

A 10 V kare dalgadır.

Girişe verilen kare dalgalar çıkışa aşağıdaki görülen pasler biçiminde transfer edilecektir.

F= 2 Khz V = 10 V V1 = 0.5 V Çıkış= 7V

Philips Semiconductors

Product specification

SMPS control circuit

SG3524

DESCRIPTION

PIN CONFIGURATION

This monolithic integrated circuit contains all the control circuitry for

a regulating power supply inverter or switching regulator. Included in

a 16-pin dual-in-line package is the voltage reference, error

amplifier, oscillator, pulse-width modulator, pulse steering flip-flop,

dual alternating output switches and current-limiting and shut-down

circuitry. This device can be used for switching regulators of either

polarity, transformer-coupled DC-to-DC converters, transformerless

voltage doublers and polarity converters, as well as other power

control applications. The SG3524 is designed for commercial

applications of 0°C to +70°C.

D, F, N Packages

INVERT INPUT 1

16 VREF

NON-INV INPUT 2

15 VIN

OSC OUTPUT 3

14 EMITTER B

(+)CL SENSE 4

13 COLLECTOR B

(–)CL SENSE 5

12 COLLECTOR A

RT

6

11 EMITTER A

CT

7

10 SHUTDOWN

GROUND 8

FEATURES

• Complete PWM power control circuitry

• Single ended or push-pull outputs

• Line and load regulation of 0.2%

• 1% maximum temperature variation

• Total supply current is less than 10mA

• Operation beyond 100kHz

9

COMPENSATION

TOP VIEW

SL00174

Figure 1. Pin Configuration

ORDERING INFORMATION

TEMPERATURE RANGE

ORDER CODE

DWG #

16-Pin Plastic Dual In-Line Package (DIP)

DESCRIPTION

0 to +70°C

SG3524N

SOT38-4

16-Pin Ceramic Dual In-Line Package (CERDIP)

0 to +70°C

SG3524F

0582B

16-Pin Small Outline (SO) Package

0 to +70°C

SG3524D

SOT109-1

BLOCK DIAGRAM

VREF 16

VIN 15

REF

REG

+5V TO ALL

INTERNAL CIRCUITRY

+5V

OSCILLATOR

3

OUTPUT

FLIP FLOP

+5V

RT 6

CT 7

(RAMP)

12

OSC

11

13

+5V

+

14 E

B

–

INV INPUT 1

+5V

ERROR

–

AMP

N.I. INPUT 2

+

CB

NOR

COMPARATOR

GROUND

8

(SUBSTRATE)

CA

NOR

+5V

+

CL

–

9

1k

4

+SENSE

5 –SENSE

COMPENSATION

10

SHUTDOWN

10k

SL00175

Figure 2. Block Diagram

1994 Aug 31

1

853-0891 13721

Philips Semiconductors

Product specification

SMPS control circuit

SG3524

ABSOLUTE MAXIMUM RATINGS

SYMBOL

PARAMETER

RATING

UNIT

VIN

Input voltage

40

V

IOUT

Output current (each output)

100

mA

IREF

Reference output current

50

mA

Oscillator charging current

5

mA

PD

Power dissipation

Package limitation

1000

mW

Derate above 25°C

8

mW/°C

0 to +70

°C

-65 to +150

°C

TA

Operating temperature range

TSTG

Storage temperature range

DC ELECTRICAL CHARACTERISTICS

TA=0°C to +70°C, VIN=20V, and f=20kHz, unless otherwise specified.

SYMBOL

PARAMETER

TEST CONDITIONS

LIMITS

UNIT

Min

Typ

Max

4.6

5.0

5.4

V

Reference section

VOUT

ISC

Output voltage

Line regulation