4. CMOS GEÇøù øLETKENLøöø KUVVETLENDøRøCøSø,

OTA

øúlemsel kuvvetlendiricinin gerilim kontrollu gerilim kayna÷ı özelli÷i

göstermesi, çıkıú direncinin çok küçük olması ve kazancın

KV =

VO

V I1 -V I 2

(4.1)

ba÷ıntısıyla tanımlanmasına karúılık, geçiú iletkenli÷i kuvvetlendiricisi gerilim

kontrollu akım kayna÷ı özelli÷i gösterir. Çıkıú empedansı yüksektir ve tanım

ba÷ıntısı

G =

IO

V I1 -V I 2

(4.2)

úeklindedir.

4.1. CMOS OTA tasarımı

En yaygın kullanım alanı bulan OTA yapıları, basit OTA, simetrik OTA ve

Miller OTA olarak isimlendirilen geçiú iletkenli÷i kuvvetlendiricisi yapılarıdır. Bu

bölümde, ilk önce, yukarıda isimleri verilen üç temel OTA yapısı ele alınarak

incelenecektir. Daha sonra, zıt fazlı ortak kaynaklı çiftlerle kurulan OTA yapısı

(ACSP OTA: Anti-Phase Common Source Pair OTA), çapraz ba÷lamalı OTA,

lineerleútirilmiú OTA gibi özel yapılar ele alınacaktır.

4.1.1. Basit OTA yapısı

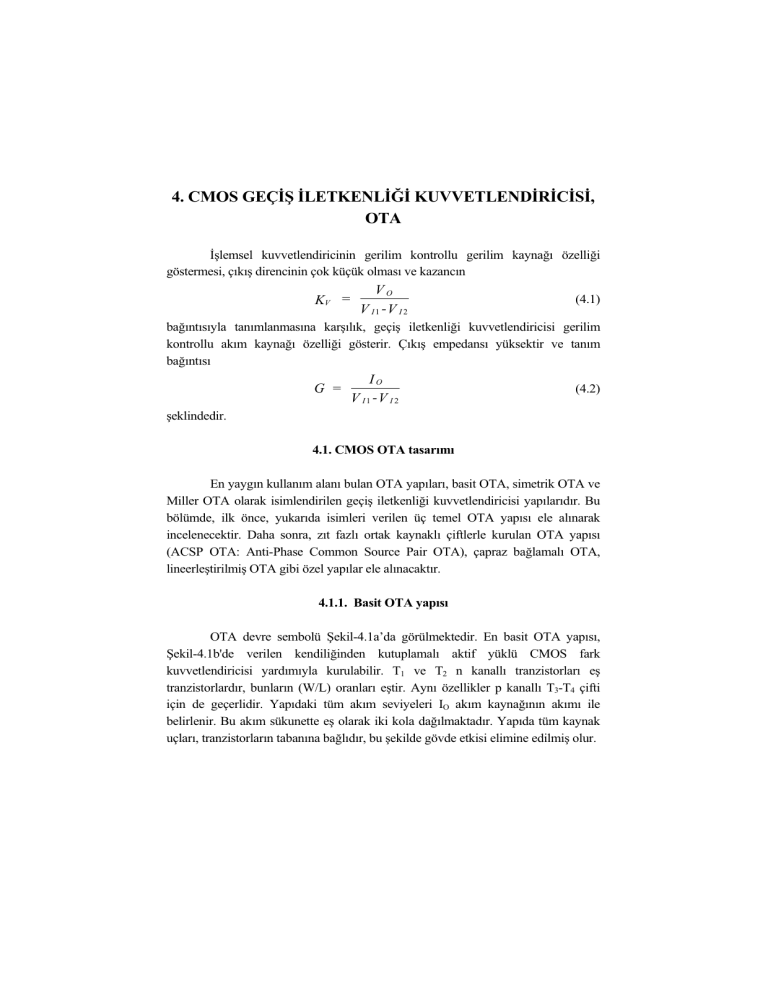

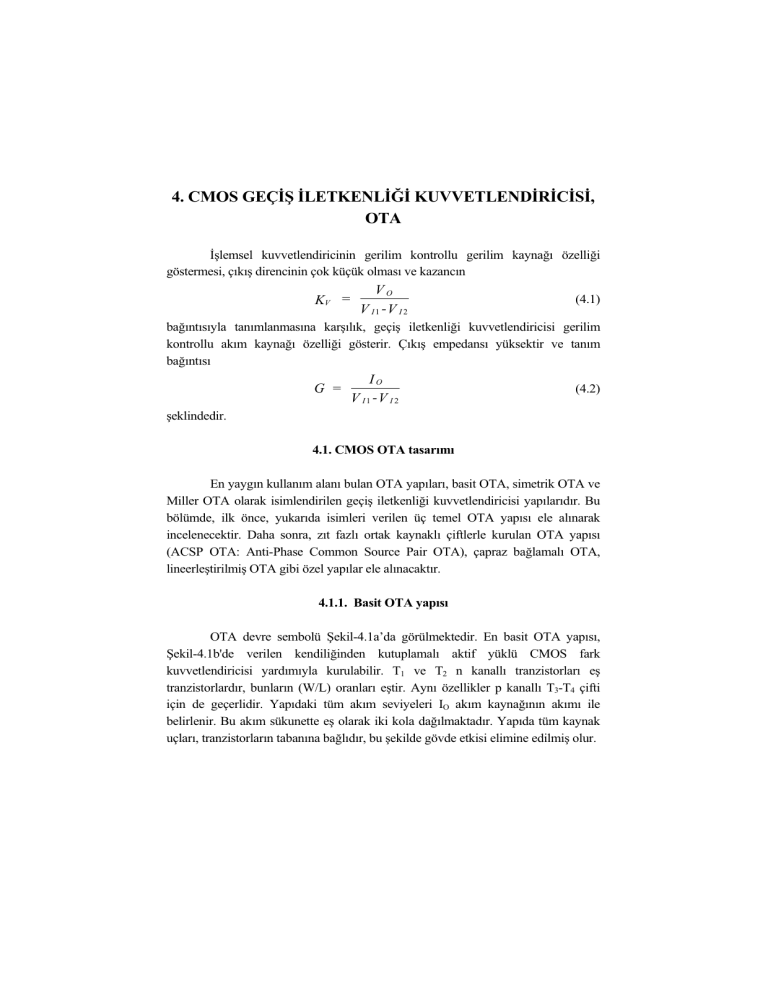

OTA devre sembolü ùekil-4.1a’da görülmektedir. En basit OTA yapısı,

ùekil-4.1b'de verilen kendili÷inden kutuplamalı aktif yüklü CMOS fark

kuvvetlendiricisi yardımıyla kurulabilir. T1 ve T2 n kanallı tranzistorları eú

tranzistorlardır, bunların (W/L) oranları eútir. Aynı özellikler p kanallı T3-T4 çifti

için de geçerlidir. Yapıdaki tüm akım seviyeleri IO akım kayna÷ının akımı ile

belirlenir. Bu akım sükunette eú olarak iki kola da÷ılmaktadır. Yapıda tüm kaynak

uçları, tranzistorların tabanına ba÷lıdır, bu úekilde gövde etkisi elimine edilmiú olur.

4.2

+VDD

T3

VI1

4

+

VI2

T4

+VI1

1

-

5

T1

T2

3

2

IO

+VO

+VI2

CL

IA

-VSS

(a)

(b)

ùekil-4.1. a) OTA devre sembolü, b) basit CMOS geçiú iletkenli÷i kuvvetlendiricisi.

Basit CMOS OTA'nın e÷imi hesaplanırsa, alçak frekanslarda

§W ·

G = k n '. I A ¨ ¸

© L ¹1

(4.3)

bulunur. Fark edilebilece÷i gibi, OTA'nın e÷imi IO kutuplama akımı ile

de÷iútirilebilmektedir; bu ise bir OTA'dan beklenen bir özelliktir. Basit OTA'nın

çıkıú direnci

(4.4)

r o = r o2 / / r o4

ba÷ıntısıyla verilebilir. Buna göre, yapının çıkıúın yüksüz durumundaki gerilim

kazancı

KV = G. r o

(4.5)

olur. Her bir tranzistorun rO çıkıú direnci, tranzistorun Early gerilimi ve savak akımı

cinsinden belirlenir. Dü÷ümlere gelen etkin dirençler, frekans cevabını belirlemede

önemli bir rol oynarlar.

4 dü÷ümü ile referans ucu arasına gelen eúde÷er direnç, T3 tranzistorunun

diyot ba÷lı olması nedeniyle

Rn4 =

1

(4.6)

§W ·

k p '. I A ¨ ¸

© L ¹4

olur. Bu ba÷ıntıda (W/L)4 büyüklü÷ü, T3 ve T4 tranzistorlarının (W/L) oranı, kP'

büyüklü÷ü ise PMOS tranzistorların proses e÷im parametresidir.

3 dü÷ümü ile referans arasına gelen direnç

4.3

Rn 3 =

1

2. g m1

(4.7)

de÷erindedir. Bu dü÷üm, yapının ortak iúaret özellikleri açısından etkili olur.

Yapının fark iúaret davranıúına, kazanç-band geniúli÷i çarpımına ve yükselme

e÷imine herhangi bir etkisi olmamaktadır.

Basit CMOS OTA'nın kazanç-band geniúli÷i

Basit CMOS OTA yapısında sadece iki dü÷ümdeki, yüksek dirençli 4 ve 5

dü÷ümlerindeki kapasiteler baskın kutbu belirleyebilirler. Yapı, genelde, iki kutuplu

bir sistem olarak düúünülebilir. Bu dü÷ümlere iliúkin etkin direnç de÷erleri Rn4 <<

Rn5 úeklindedir. Bu nedenle, Cn5 etkin kapasitesi Cn4 etkin kapasitesine göre çok

daha düúük frekanslı bir kutup oluúturur ve bu kutup baskın kutup olur. Rn5 = rO

úeklinde yapının çıkıú direncine eúit oldu÷undan, CL yük kapasitesinin de dikkate

alınmasıyla, baskın kutup

fd =

1

2S r o ( C n5 + C L )

(4.8)

biçiminde ifade edilebilir. Burada

C n5 = C gd 4 + Cdb 4 + C gd 2 + C db 2

úeklinde verilmektedir. Yapının kazanç-band geniúli÷i çarpımı hesaplanırsa

GBW = KV . f d =

§W ·

kn ' I A¨ ¸

© L ¹1

GBW =

2S ( C n 5 + C L )

g m1

2S ( C n5 + C L )

(4.9)

bulunur. Bu ba÷ıntının geçerli olabilmesi için f <GBW için frekans e÷risinin

düúme e÷imi -20dB/dek olmalıdır. Baúka bir deyiúle, baskın olmayan kutup

frekansının minimum de÷eri GBW'de olmalıdır. Bu, kararlılı÷ın sa÷lanması

açısından gereklidir; böylece, faz payı 45o olur.

4.4

Kararlılık

Di÷er dü÷ümdeki, 4 dü÷ümündeki eúde÷er elemanlardan ileri gelen baskın

olmayan kutup

1

2S R nd C n 4

f nd =

(4.10)

biçiminde ifade edilir. Bu ba÷ıntıda

Rn 4 =

1

g m4

C n 4 = C gd 1 + C db1 + C db 3 + C gs 3 + C gd 4 .(1+ g m4 .ro )

olur. 45o faz payını sa÷lamak üzere fnd = GBW alınırsa

g m4

Cn4

=

g m1

C n5 + C L

olur. kn' = a.kp' oldu÷u kabul edilirse

C L + Cn5

=

C n4

§W ·

a¨ ¸

© L ¹1

§W ·

¨ ¸

© L ¹4

yahut

§W ·

§ W · § Cn 4 ·

¨ ¸ = a¨ ¸ ¨

¸

© L ¹4

© L ¹1 © C L + Cn 5 ¹

2

(4.11)

bulunur. Elde edilen ba÷ıntı, kararlılık için gerekli olan minimum CLmin yük

kapasitesi de÷erini vermektedir.

Dört temel büyüklük, IO akımı, CL yük kapasitesi, (W/L)1 ve (W/L)4

oranları performansı belirlemektedir. Verilen bir IA akımı için GBW optimize

edilsin. CL veya (W/L)1 büyüklükleri serbest de÷iúken olarak alınabilir. Ancak, bu

durumda (W/L)4 oranı ba÷ımsız seçilemez; zira, ba÷ıntılardan fark edilebilece÷i

gibi, bunun de÷eri (W/L)1 ile belirlidir. CL serbest seçilirse, GBW büyüklü÷ü

(W/L)11/2 ile orantılı olur. Her (W/L)1 oranı için bir (W/L)4 oranı bulunur.

4.5

(W/L)1 ve (W/L)4 oranlarının serbest olarak seçilmeleri durumunda, CL yük

kapasitesinin alabilece÷i minimum de÷er buna göre belirlenebilir. Fark edilebilece÷i

gibi, CL yük kapasitesi, aynı zamanda, kompanzasyon kapasitesi görevini

üstlenmektedir.

Maksimum GBW için optimizasyon

Cn4 ve Cn5 kapasiteleri gerçekte boyutlara ba÷lı kapasitelerdir. (W/L) oranı

artarsa, kapasitenin de de÷eri artar. Basit bir model kullanılarak, dü÷üm kapasiteleri

boyuta ba÷lı biçimde ifade edilebilirler:

(4.12)

C n = C n 0 + k 1 .(W / L )1 + k 4 .(W / L )4

Cn4 ve Cn5 kapasiteleri bu úekilde ifade edilerek ba÷ıntıda yerlerine

konurlarsa

r 1 = (W / L )1 , r 4 = (W / L )4

k 4 = k 1 , C Lc = C L + C n 0

olmak üzere, kazanç-band geniúli÷i çarpımı

GBW =

kn ' I A

r1

.

2S

C Lc + k 1 ( r 1 + r 4 )

(4.13)

úekline getirilebilir.

r1 büyüklü÷ünün düúük ve yüksek de÷erli olması sınır durumları incelensin.

a- r1 büyüklü÷ü düúük de÷erli ise r4 de düúük de÷erli olur. Böylece kazançband geniúli÷i çarpımı

GBW =

k n ' I A r1

.

2S

C Lc

(4.14)

biçiminde yazılabilir. Bu durumda (W/L)11/2 arttıkça, GBW de artar.

b- r1 büyüklü÷ü yüksek de÷erli ise, GBW

GBW =

úeklinde ifade edilebilir. r4 = b.r1 için

kn ' I A

r1

.

2S

(

k 1 r1 + r 4 )

(4.15)

4.6

GBW =

1

kn'I A

.

2S (b + 1).k 1 r 1

olur. Bu durumda (W/L)11/2 arttıkça, GBW azalır. Bu iki sınırın bir ara de÷eri

bulunaca÷ı ve optimum bir GBW çarpımı elde edilece÷i açıktır. Bunun için iki

durumun eúitlendi÷i (W/L)1 = (W/L)1m durumu araútırılırsa

§W ·

C Lc

¨ ¸ =

© L ¹1m

(b + 1). k 1

elde edilir. Bu noktada maksimum kazanç-band geniúli÷i çarpımı

GBW =

1 k nc I A

1

.

2 2S

(b + 1). k 1 C Lc

olur. Bu maksimum (IA)1/2 ile do÷ru, (CL)1/2 ile de ters orantılıdır. Büyük CL

de÷erleri için giriú tranzistorları daha büyük tutulur. Yapının yükselme e÷imi

SR =

IA

C Lc + C n 5

olur. ølk bakıúta yükselme e÷imi simetrik gözükmekle birlikte, di÷er dü÷ümün

kapasitesi bu simetriyi bozar.

4.1.2. Miller OTA

CMOS tekni÷i ile gerçekleútirilen ve Miller OTA olarak isimlendirilen

geçiú iletkenli÷i kuvvetlendiricisi yapısı ùekil-4.2'de görülmektedir. Yapı iki

kazanç katından oluúur. ølk kat fark kuvvetlendiricisidir ve PMOS tranzistorlarla

kurulmuútur, ikinci kat ise CMOS evirici olarak kurulmuútur ve T3 tranzistoru aktif

yük iúlevini yerine getirir. Bunun çıkıúı, CC kompanzasyon kapasitesi ile fark

kuvvetlendiricisinin çıkıúına ba÷lanmıútır. Miller kompanzasyonu uygulandı÷ından.

yapı Miller OTA olarak da isimlendirilmektedir.

4.7

1: 1

T8

1: B

T5

T7

T1

+VI1

3

CC

T2

4

RL

+VDD

VO

CL

+VI2

2

IB

1

T3

T4

T6

-VSS

ùekil-4.2. Miller geçiú iletkenli÷i kuvvetlendiricisi (Miller OTA).

Yapı ba÷ımsız IB akım kayna÷ı ile kutuplanmıútır. T7 ve T8 tranzistorları eú

tranzistorlardır; fark kuvvetlendiricisinden de toplam olarak IB akımı akar. T5

tranzistoru çok daha büyük boyutlu oldu÷undan, ikinci katın akımı çok daha yüksek

de÷erlidir.

Devrenin katlarının gerilim kazancı

g L ' = g L + g o5 + g o 6

(4.16)

olmak üzere

KV 10 =

g m1

g o2-4

KV 20 = -

g m6

g L'

(4.17)

(4.18)

ba÷ıntılarıyla tanımlanmıútır. Böylece toplam kazanç

KVO = KV 10 . KV 20 =

olur.

Miller OTA'nın geçiú iletkenli÷i ise

g m1 g m6

.

g o2-4 g Lc

(4.19)

4.8

G =

g m1

.g

g o2-4 m6

(4.20)

ba÷ıntısıyla verilebilir.

CC kompanzasyon kapasitesi yokken kutuplar hesaplanırsa, üç kutuplu bir

sistem oluúaca÷ı fark edilebilir. (1) dü÷ümü en yüksek empedanslı dü÷ümdür ve

ço÷unlukla baskın kutup bu dü÷ümden ileri gelir. Bu dü÷üme iliúkin kutup

(4.21)

C n1 = C gd 2 + C db 2 + C gd 4 + C db 4 + C gs 6 C gd 6

olmak üzere

f

p1

g o 24

=

(4.22)

2S . Cn1

úeklindedir. 2. kutup (2) dü÷ümünün etkisiyle oluúur ve

C n 2 = C gs 3 + C db 3 + C gs 4 + C gd 4 + C gd 1 + C db1

(4.23)

olmak üzere

f

p2

=

g m3

(4.24)

2S C n 2

biçimindedir. Üçüncü kutup çıkıú dü÷ümünde oluúur ve

(4.25)

C n 4 = C gd 5 + C db5 + Cdb 6

olmak üzere

f

p4

=

gL '

2S .( C L + C n 4 )

(4.26)

ba÷ıntısıyla verilir. (2) dü÷ümü 0 dB seviyesinin altında etkilidir. Ancak, di÷er iki

kutup birbirine yakın konumdadır. Bu nedenle faz payı negatif ve devre kararsız

olur. Kompanzasyon kapasitesi ile faz payı FP = 60o civarına getirilir. Bu

yapıldı÷ında fp1 çok daha baskın olur ve -20dB/dek'lık düúme e÷imi elde edilir. CC

ile oluúturulan baskın kutup

BW = f 3dB =

g o2-4

2S KV 20 . C C

(4.27)

ve kazanç-band geniúli÷i de

GBW =

g m1

2S CC

olur. Band geniúli÷i úöyle de yazılabilir :

(4.28)

4.9

g o2-4

BW =

=

g o2-4 g L '

2S g m6 C C

2S K V2O C C

g m1

GBW

BW =

=

2S KVO CC

KVO

(4) dü÷ümünden ileri gelen baskın olmayan kutup

f nd =

g m6

1

2S C L ' 1+ Cn1 / C L + Cn1 / CC

.

olur. CL ve CC >> Cn1 oldu÷undan

f nd =

gm6

2S C L '

elde edilir. Yüksek frekanslarda CC kısadevre özelli÷i gösterdi÷inden, çıkıú direnci

rezistif ve 1/gm6 olur. Bu durumda fnd > GBW dir ve faz payı da

FP = 90o arctan(GBW / f nd )

(4.29)

úeklindedir.

Yükselme e÷imi

Birinci dereceden bir yaklaúımla, sadece CC nin

varsayımından hareketle yükselme e÷imi için

SR =

etkisi bulundu÷u

IB

CC

(4.30)

ba÷ıntısı verilebilir. økinci dereceden yaklaúımda CL nin dolup boúalması da dikkate

alınmaktadır. CL yük kapasitesinin boúalması sırasında sorun yoktur; zira, T6

tranzistoru yeteri kadar büyük akım akıtabilir. CL kapasitesi T5 üzerinden I5 -IB

akımıyla dolar, zira IB kadar bir akım CC üzerinden akacaktır. Böylece

SR+ =

I5 - I B

CL

(4.31)

olur. Bu iki büyüklükten küçük olanı yükselme e÷imi olarak alınır.

Bir OTA'dan beklenen temel özelliklerden biri de Gm geçiú iletkenli÷inin IB

kontrol akımıyla belirlenmesidir. Bu özelli÷in Miller OTA'da sa÷lanıp sa÷lanmadı÷ı

4.10

araútırılsın. Yapının geçiú iletkenli÷i daha önce (4.20) ba÷ıntısı ile verilmiúti. Bu

ba÷ıntıda

gm1 =

gm 6 =

g o2-4 =

§W ·

k p ' . I B .¨ ¸

© L ¹1

§W ·

2. k n '. B. I B .¨ ¸

© L ¹6

IB

. ON OP 2

úeklindedir. Bu büyüklükler e÷imi veren (4.20) ba÷ıntısında yerlerine konursa

Gm =

§W · §W ·

. 2 k n ' . k p ' .B.¨ ¸ .¨ ¸

© L ¹1 © L ¹6

ON OP 2

(4.32)

ba÷ıntısı elde edilir. Buna göre Miller geçiú iletkenli÷i kuvvetlendiricisinde e÷im

kutuplama akımından ba÷ımsız çıkmaktadır. Ba÷ıntıdan fark edilebilece÷i gibi,

kuvvetlendiricinin e÷imi, fiziksel büyüklüklerle geometri tarafından belirlenmekte

ve sabit de÷erli olmaktadır. Yapının e÷iminin, dolayısıyla gerilim kazancının

yüksek olmasına karúılık, e÷iminin akımla kontrol edilmesi özelli÷i bulunmamakta,

bu da Miller geçiú iletkenli÷i kuvvetlendiricisinin, kutuplama akımıyla e÷imin

de÷iútirilmesine dayanılarak akort edilen aktif OTA-C süzgeçleri

gerçekleútirilmesine uygun düúmemesine yol açmaktadır. Miller OTA’dan,

ço÷unlukla, sonuna bir çıkıú katı ba÷lanarak iúlemsel kuvvetlendirici

gerçekleútirilmesi amacıyla yararlanılmaktadır. Aktif süzgeç uygulamaları için ise,

aúa÷ıda ele alınacak olan simetrik OTA yapısı daha uygun olmaktadır.

4.1.3 Simetrik CMOS OTA yapısı

Simetrik CMOS OTA yapısı ùekil-4.3a 'da verilmiútir. Bu yapı geniú bandlı

olması nedeniyle yüksek frekanslı aktif süzgeçlerin ve osilatörlerin

gerçekleútirilmesine son derece elveriúli olmaktadır. IA kontrol akımı yardımıyla

OTA e÷imi de÷iútirilebilir; böylece süzgecin akort frekansını ayarlamak mümkün

olur. Devrenin çıkıú direncinin yüksek olması istenirse, yapıda kaskod akım aynaları

4.11

kullanılır. Bu úekilde gerçekleútirilen CMOS simetrik kaskod OTA yapısı da ùekil4.3b’de görülmektedir. Bu devrenin çıkıú direnci ve çıkıú kapasitesi hariç, di÷er

özellikleri (e÷im, akım sınırları,vb.) düz akım aynalı simetrik OTA yapısı ile

aynıdır. Küçük iúaret eúde÷er devresi kullanılarak OTA’nın çıkıú direnci

hesaplanırsa, çıkıú direncinin, düz akım aynası ile gerçekleútirilen basit OTA’ya

göre 1+gmro kadar daha büyüdü÷ü görülür.

B:1

T5

1:B

T3

T4

4

1

T1

+VI1

+VDD

T6

5

3

T2

2

+VI2

VO

7

6

IA

T7

1:1

T8

-VSS

ùekil-4.3a. Simetrik CMOS geçiú iletkenli÷i kuvvetlendiricisi ( simetrik CMOS OTA).

ùekil-4.3a’daki yapıda T1-T2 tranzistorları bir fark kuvvetlendiricisi

oluútururlar. Bunların çıkıú akımları ile diyot ba÷lı T3 ve T4 PMOS tranzistorları

sürülmektedir. Diyot ba÷lı T3 ve T4 tranzistorlarının akımları, (W/L) oranları

diyotların B katı olan T5 ve T6 tranzistorları yardımıyla B çarpanı ile çarpılıp çıkıúa

yansıtılmaktadır.

Simetrik OTA'nın e÷imi, gerilim kazancı

Yapıda, 4, 5 ve 6 dü÷ümlerinin her birinde, diyot ba÷lı birer MOS

tranzistor birer akım kayna÷ı tarafından sürülmektedir. Diyot ba÷lı bir MOS

tranzistorlar düúük de÷erli bir 1/gm empedansı, akım kayna÷ı tranzistorları ise rO >>

1/gm de÷erinde yüksek bir çıkıú empedansı gösterirler. Bunun sonunda, 4, 5 ve 6

dü÷ümlerinde akımla sürme iúlemi gerçekleútirilmiú olur.

4.12

+VDD

T6

T4

T8

T10

T5

T3

T7

M9

T1

T2

V-

+VO

V+

T11

IO

T13

IA

T12

T14

-VSS

ùekil-4.3b. Simetrik CMOS kaskod geçiú iletkenli÷i kuvvetlendiricisi ( simetrik CMOS

kaskod OTA).

Devrede, sadece, 7 dü÷ümünde küçük iúaret direnci yüksektir ve rO =

rO6//rO8 de÷erindedir. Simetrik OTA'nın geçiú iletkenli÷i hesaplanırsa

§W ·

G = B. k n ' . I A .¨ ¸

© L ¹1

(4.33)

bulunur. Bu e÷im basit OTA yapısının e÷iminin B katı kadardır. B akım çarpma

faktörünün tipik de÷eri B = 3 ...5 arasında bulunur.

Simetrik OTA'nın gerilim kazancı

RO =

2

( O N + O P ).B. I A

olmak üzere

KV = G. RO

(4.34)

ba÷ıntısıyla verilebilir. Bu büyüklük B çarpanından ba÷ımsızdır. B arttıkça devrenin

Gm geçiú iletkenli÷i de artar, ancak RO çıkıú direnci de aynı oranda azalır. Bu

nedenle, gerilim kazancı sabit kalır. Yapıda, ilk katın kazancı da önemli bir etkendir.

Bu kazanç, devrenin gürültü özelliklerini belirler. Düúük gürültülü devre

uygulamaları için kat kazancı 3 civarında tutulur. ølk katın kazancı

4.13

KV =

gm1

k n ' (W / L )1

.

k p ' (W / L )3

=

g m4

(4.35)

biçiminde ifade edilmektedir.

Kararlılık

Kuvvetlendiricinin transfer fonksiyonunda baskın olmayan kutuplar 4, 5 ve

6 dü÷ümlerinden ileri gelir. 4 ve 5 dü÷ümleri aynı iúareti iki kola da

aktardıklarından tek bir baskın olmayan kutup oluútururlar. Bu dü÷ümler üzerinden

aktarılan iúaret, iki koldan 7 numaralı çıkıú dü÷ümüne gelir. 6 dü÷ümünde ise di÷er

bir baskın olmayan kutup oluúur. Ancak, bu dü÷üm iúaret yolunun sadece bir kolu

üzerindedir; baúka bir deyiúle yarısı üzerine etkilidir. Çıkıú akımının T2, T4 ve T6

üzerinden geçen bileúeni bundan etkilenmez. Bu kutup, T3, T5 , T7 ve T8 yolu

üzerinden gelen bileúene etki eder. Yapılan incelemeler, bu etkinin devrenin transfer

fonksiyonu üzerine zaman sabitinin belirledi÷i frekansta bir kutup ve iki katı

frekanslı bir sıfır getirece÷ini göstermiútir. Böylece, baskın kutup

fd =

1

2S R O (CL C n 7 )

(4.36)

baskın olmayan kutuplar ve sıfır

gm 4

f nd 5 =

2S C n 5

(4.37a)

g m7

(4.37b)

f z 6 = 2. f nd 6

(4.37c)

f nd 6 =

2S C n 6

§

©

I 5 = arctg¨ B. KV 1 .

Cn 5 ·

¸

C L + Cn7 ¹

(4.38a)

§ B.(W/L )1 C n6

.

(W/L

)

C L + C n7

7

©

·

§

·

¸ arctg ¨ 1 . B.(W/L )1 . C n6 ¸ (4.38c)

¸

¨2

(W/L )7 C L + C n7 ¸¹

¹

©

I m = 90 o - I 5 - I 6

(4.40)

I 6 = arctg ¨¨

olmak üzere

4.14

biçiminde yazılabilir. Bu ba÷ıntı uyarınca, faz payını arttırmak üzere

-B azaltılmalı,

-KV1 azaltılmalı,

-Cn5 ve Cn6 azaltılmalı,

-CL yük kapasitesi arttırılmalı,

-(W/L)7 oranı arttırılmalıdır.

Devrenin yükselme e÷imi

SR = B.

IA

C L + Cn7

úeklinde verilebilir.

Yükselme e÷iminin arttırılabilmesi için B çarpanının arttırılması gerekir.

Ancak, faz payının arttırılması için ise B nin azaltılması gerekece÷i açıktır. Bu

nedenle, B çarpanı için iyi bir yaklaúım B = 3 almaktır.

Gürültüyü azaltmak için KV1 ilk kat kazancının arttırılması gerekir. Faz payı

için ise bu kazancın azaltılması gerekir. ølk kat kazancı için de iyi bir yaklaúım KV1

= 3 alınmasıdır.

Dü÷üm kapasitelerinin de olabildi÷ince küçültülmesi gerekir. Kararlılı÷ın

sa÷lanabilmesi için (W/L)7 oranının yahut CL nin uygun seçilmesi gerekli olur. Her

ikisinin de÷erinin birlikte de÷iútirilmesi pek uygun de÷ildir. Genelde f5 > f6 olur.

Bunlara B ve KV1 etkilidir ve bu iki büyüklü÷ün çarpımı 9 civarında olur. Bu

nedenle, CL yük kapasitesinin de÷iútirilmesi (W/L)7 oranının de÷iútirilmesine göre

daha etkili olur.

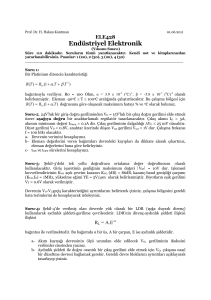

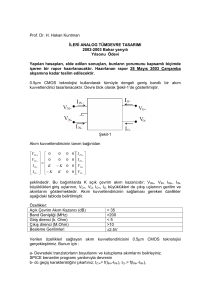

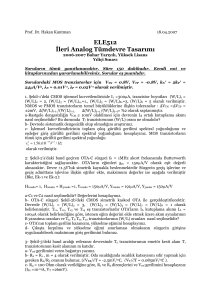

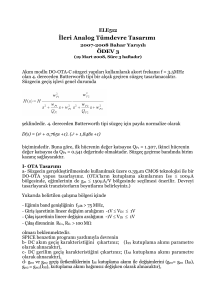

Simetrik bir OTA’yı karakterize eden temel e÷riler ùekil-4.4, ùekil-4.5,

ùekil-4.6 ve ùekil-4.7’de verilmiútir. ùekil-4.4, ùekil-4.3b’de verilen CMOS

simetrik kaskod OTA yapısında, çeúitli kutuplama akımı de÷erleri için çıkıú

akımının tipik de÷iúim biçimini göstermektedir. ùekil-4.5’de ise OTA’nın e÷iminin

çeúitli kutuplama akımı de÷erleri için frekansla nasıl bir de÷iúim gösterece÷i

verilmiútir. Bu karakteristikler çıkartılırken çıkıú ucu referans dü÷ümüne kısadevre

edilmekte yahut düúük de÷erli bir dirençle kapatılmaktadır. ùekil-4.6’da sabit

kutuplama akımında çıkıú geriliminin de÷iúim sınırları gösterilmiútir. ùekil-4.7’de

ise sabit kutuplama akımında simetrik OTA’nın gerilim kazancının frekansla

de÷iúimi görülmektedir.

4.15

*CMOS Kaskod OTA çýkýþ akýmý-giriþ gerilimi karakteristiði

Date/Time run: 09/24/96 23:29:14

I

O

Temperature: 27.0

1.0mA

IA kutuplama akýmýparametre olarak alýnmýþtýr.

250uA

200uA

0.5mA

150uA

100uA

50uA

0A

-0.5mA

-1.0mA

-2.0V

-1.5V

-1.0V

I(vci)

-0.5V

0V

0.5V

1.0V

1.5V

2.0V

Vin

ùekil-4.4. CMOS simetrik kaskod OTA’da çıkıú akımının giriú gerilimiyle de÷iúimi, IA

kutuplama akımı parametre olarak alınmıútır.

*CMOS Kaskod OTA eðimin frekansla degiþimi

Date/Time run: 09/24/96 23:47:23

e

g

i

m

Temperature: 27.0

1.5mA

250uA

200uA

150uA

1.0mA

100uA

50uA

0.5mA

IA kutuplama akýmýparametre olarak alýnmýþtýr.

0A

100h

1.0Kh

10Kh

100Kh

1.0Mh

10Mh

100Mh

I(vci)

Frequency

ùekil-4.5. Simetrik CMOS kaskod OTA’da e÷imin frekansla de÷iúimi, IA kutuplama akımı

parametre olarak alınmıútır.

4.16

*CMOS Kaskod OTA çýkýþ gerilimi-giriþ gerilimi deðisimi

Date/Time run: 09/24/96 23:34:34

V

O

Temperature: 27.0

20V

IA kutuplama akýmýparametre olarak alýnmýþtýr.

50uA

250uA

10V

0V

-10V

-20V

-2.0V

-1.5V

V(4)

-1.0V

-0.5V

0V

0.5V

1.0V

1.5V

2.0V

Vin

ùekil-4.6. CMOS simetrik kaskod OTA’da çıkıú açık devre geriliminin giriú gerilimiyle

de÷iúimi, IA kutuplama akımı parametre olarak alınmıútır.

*CMOS Kaskod OTA gerilim kazancinin frekansla degisimi

Date/Time run: 09/24/96 23:57:28

d

B

Temperature: 27.0

40

250uA

30

200uA

20

150uA

100uA

50uA

10

0

-10

IA kutuplama akimi parametre olarak alinmistir.

-20

100h

1.0Kh

Vdb(4)

10Kh

100Kh

1.0Mh

10Mh

100Mh

Frequency

ùekil-4.7. CMOS simetrik kaskod OTA’da açıkdevre gerilim kazancının frekansla de÷iúimi,

IA kutuplama akımı parametre olarak alınmıútır.

4.17

Bu iki karakteristik çıkartılırken, çıkıú ucu açık devre edilmekte yahut büyük de÷erli

bir direnç ile kapatılmaktadır. ùekil-4.4, ùekil-4.5, ùekil-4.6 ve ùekil-4.7’de verilen

karakteristikler SPICE simülasyon programı yardımıyla elde edilmiúlerdir.

4.2. Zıt fazlı ortak kaynaklı çiftlerle kurulan OTA yapısı (ACSP OTA: AntiPhase Common Source Pair OTA)

Zıt fazlı ortak kaynaklı çiftlerle kurulan OTA yapısının tasarlanmasının

en büyük nedeni daha geniú bir lineer çalıúma bölgesi elde etmek, daha önemlisi

lineer çalıúma bölgesinin mümkün oldu÷u kadar lineer bir de÷iúime sahip

olmasını sa÷lamaktır. Daha önce ele alınan simetrik OTA yapısında çıkıú

akımının de÷iúim sınırlarının rB.IA olaca÷ı gösterilmiúti. Ancak, simetrik OTA

yapısında giriú geriliminin OTA’nın lineer çalıúma bölgesine karúı düúen

de÷iúim aralı÷ı, birçok uygulama açısından yetersiz kalmakta ve lineer de÷iúim

bölgesinin geniúletilmesi zorunlu olmaktadır. Bu soruna çözüm getirmek için

geliútirilen düzenlerden biri de zıt fazlı ortak kaynaklı çiftlerle kurulan OTA

(ACSP OTA) yapısıdır.

ID1

ID2

T1

T2

Vi2

Vi1

+_

VS

ùekil-4.8 ACSP OTA temel devresi.

ACSP OTA nın tasarımı ùekil-4.8’deki devreye dayanmaktadır. Bu

devreden hareket edilirse, devredeki T1 ve T2 tranzistorlarının doymada

çalıútıkları ve eú tranzistorlar olmaları úartı altında K= E/2 olmak üzere

I D1

K.(V1 VS VT ) 2

I D2

K.(V2 VS VT ) 2

(4.41)

4.18

yazılabilir. 'ID=ID1-ID2 ve 'Vi=Vi1-Vi2 olarak tanımlanırsa, fark çıkıú akımı için

'I D

§V1 V2

·

2. K . 'Vi .¨

VS VT

© 2

¹

I D1 I D 2

(4.42)

elde edilir. (4.41) ve (4.42) denklemlerinin dikkatli bir úekilde incelenmesiyle,

lineer ve geçiú bölgesi içerisinde e÷imi çalıúma noktasından etkilenmeyen bir

geçiú karakteristi÷i elde etmek üzere, VS gerilim kayna÷ının sa÷laması gereken

koúul çıkarılabilir. Bu koúul

V1 V2

Vk

2

VS

(Vk d 0)

(4.43)

biçimindedir. Bu durumda OTA nın akım-gerilim iliúkisi

'I D

2. K . 'Vi .(Vk VT )

(4.44)

ve yapının e÷imi de

gm

w' I D

w'Vi

gm

2. K .(Vk VT )

(4.45)

'Vi 0

(4.46)

olur. ACSP OTA yapısının çıkıú katı dıúındaki temel hücresi ùekil-4.9’da

görülmektedir. ùekil 4.9’daki TD1 ve TD2 tranzistorları ùekil-4.8’deki T1 ve T2

VCC

I1

TD12

I2

TD13

TD4

V1

TD3

TD1

VB

TD6

TD9

2

VC

V2

TD2

TD8

VSS

VCC

TD11

TD5

1

2

1

TD14

VB

TD16

TD7

1

VB

2

TD10

VSS

TD17

TD15

VSS

VB

VSS

ùekil-4.9 ACSP OTA Yapısı

4.19

tranzistorlarına karúı düúmektedir. Devredeki di÷er tranzistorlar ise ùekil4.8’deki VS gerilim kayna÷ına, (4.43) koúulunu sa÷layacak biçimde karúı

düúmektedir. ùekil-4.9’daki ayırıcı katın tranzistor düzeyindeki eúde÷eri yine

úekil üzerinde gösterilmiútir. ùekil-4.9’daki TD1,TD2 trazistorları ve tampon devre

bir yana bırakılıp, devrenin geri kalan kısmı ele alınsın. Bu devre ùekil-4.10’da

görülmektedir. ùekildeki her bir tranzistorun doymada çalıúması durumunda

I1,I2,I3 ve I4 akımları için

ISS

I2

I1

V

T 1 T3

1

V1

T4

3

I4

I3

VS1

T2

2

V2

VS2

ISS

ISS

ùekil 4.10. Lineerleútirme devresi

I1

I2

I3

I4

E

2

E

2

E

2

E

2

(VGS 1 VT ) 2

(VGS 2 VTn ) 2

(VGS 3 VTn ) 2

(VGS 4 VTn ) 2

E

2

(V1 VS 1 VT ) 2

E

2

E

2

E

2

(a)

(V2 VS 2 VT ) 2 (b)

(V VS 1 VT ) 2

(c)

(V VS 2 VT ) 2

(d)

(4.47)

yazılabilir. ùekil-4.10’ dan hareket edilirse, 1,2 ve 3 numaralı dü÷ümler için

I 1 I 3 I SS (a)

I 2 I 4 I SS (b)

I 3 I 4 I SS (c)

4.20

(4.48)

elde edilir. (4.48.a) denkleminde (4.47a) ve (4.47c) denklemlerinin yerine

konması ve karesel terimlerin açılımı sonucu VS1 gerilimi için

2VS 1 2 2VS 1 (V1 VT V VT ) (V1 VT ) 2 (V VT ) 2 2I SS

E

0

ikinci dereceden denklemi elde edilir. Bu denklemin kökleri hesaplanırsa VS1

gerilimi için

VS 11, 2

V1 V 2VT 1 4I SS

r

(V1 V ) 2

2

2 E

(4.49)

bulunur. Benzer úekilde hareket edilerek, VS2 gerilimi için (4.48b) denkleminde

(4.47b) ve (4.47d) denklemleri yerine konur ve elde edilen ikinci dereceden

denklemin kökleri bulunursa, VS2 gerilimi için

VS 11, 2

V2 V 2VT 1 4I SS

r

(V2 V ) 2

2

2 E

(4.50)

yazılabilir. V1=V2=0 için devre tamamen simetrik bir yapıda oldu÷u görülür.

Buna göre V1=V2=0 oldu÷u durum için T3 ve T4 tranzistorlarından ISS/2 akımı

akmalıdır. Aynı úekilde T1 ve T2 tranzistorlarından da ISS/2 akımları akmalıdır.

Buna göre

VS 1

VS 2

V 2VT 1 4I SS

r

V 2

2

2 E

(4.51)

olur.

T1, T2, T3 ve T4 tranzistorlarının boyutları aynı oldu÷u durum için her bir

tranzistorun VGS gerilimi savaklarından akan akım ISS/2 ye ba÷lı olarak eúit

olacaktır. Bu VGS gerilimleri tranzistorların iletimde olması koúulundan ~VTN~

eúik geriliminden mutlak de÷erce büyük olmalıdır. ùekil-4.10’daki devreye

tekrar bakılacak olursa V1=V2=0 için T1 ve T3 tranzistorlarının VGS gerilimleri

aynı olması gerekti÷inden ve her iki tranzistorun da kaynak uçları ortak bir

dü÷üme ba÷lı oldu÷undan, T1 ve T3 tranzistorlarının geçit gerilimlerinin

birbirine eúit olması gerekti÷i söylenebilir. Bu koúul 3 numaralı dü÷üm gerilimi

olan V nin sıfır volt olması anlamına gelir. Buna göre (4.51) numaralı

denklemde V=0 konulursa (4.52) elde edilir. Daha önce de söylendi÷i gibi, her

bir tranzistorun iletimde olması için VGS gerilimleri

4.21

VS 1

VT r

VS 2

1 4 I SS

2 E

(4.52)

~VT~ den mutlak de÷erce büyük olmalıdır. (4.52) bu koúul altında düúünülecek

olursa, ortada karekökün önündeki iúaretin eksi olması gerekti÷i kolayca fark

edilebilir. Buna göre gerçek VS1 ve VS2 gerilimleri

V1 V 2VT 1 4 I SS

(V1 V ) 2

2

2 E

VS 1

(4.53)

V2 V 2VT 1 4I SS

(V2 V ) 2

2

2 E

VS 2

olur. (4.48c), (4.47c) ve (4.47d) denklemlerinin kullanılması ve (4.53) deki VS1

ve VS2 gerilimlerinin yerlerine konulması ile

(V V1 ).

4 I SS

E

(V1 V ) 2 (V V2 ).

4I SS

E

(V2 V ) 2

0

denklemi elde edilir. Bu denklem

­ 4 I SS

½

­ 4 I SS

½

(V V1 ) 2 . ®

(V1 V ) 2 ¾ (V V2 ) 2 . ®

(V2 V ) 2 ¾

¿

¯ E

¯ E

¿

(4.54)

biçiminde yazılabilir. a=4ISS/E olarak tanımlanırsa, bu ba÷ıntı

a . > (V V1 ) 2 (V V2 ) 2 @

(V V1 ) 4 (V V2 ) 4

(4.55)

úeklinde yazılabilir. Eúitli÷in sa÷ ve sol tarafındaki karelerin farkları úeklindeki

terimler (m-n)(m+n) úeklinde yeniden düzenlenir ve gerekli sadeleútirme

iúlemleri yapılırsa, (4.55) ba÷ıntısı

V 2 V (V1 V2 ) 1 2

(V V2 2 a )

2 1

0

(4.56)

biçimine dönüútürülebilir. (4.56) daki ikinci dereceden denlemin çözümünden

elde edilecek iki kök

V1,2

V1 V2

r

2

2 I SS

E

(V1 V2 ) 2

4

(4.57)

4.22

úeklinde olur. Daha önce söylendi÷i üzere V1=V2=0 için V=0 olmalıdır. Ancak

bu koúul (4.57) deki iki kök için de sa÷lanmamaktadır. Bu durumda (4.57) deki

kökler uygun sonuçlar de÷ildir. Bu nedenle (4.55) deki ana polinom yeniden

düzenlenirse

4V 3 (V1 V2 ) 6V 2 (V2 2 V1 2 ) V > 4V1 3 4V2 3 2a (V2 V1 )@

V1 4 V2 4 aV1 2 aV2 2

0

(4.58)

olur. Bilindi÷i üzere (4.58) deki üçüncü dereceden polinomun iki kökü (4.57)

deki gibidir. (4.58) in (4.56) polinomuna bölünmesi durumunda geriye kalan

birinci dereceden denklem bize olması gereken kökü verecek denklemdir.

(4.58)’in (4.56)’ya bölünmesinden ortaya çıkacak sonuç

4V (V1 V2 ) 2 (V2 2 V1 2 )

0

(4.59)

úeklindedir. (4.59) un çözümünde V gerilimi için

V1 V2

2

V

(4.60)

iliúkisi elde edilir. Görüldü÷ü üzere ùekil-4.8’deki VS gerilim kayna÷ının

sa÷laması gereken koúulu, bir Vk gerilimi farkıyla ùekil-4.10’daki devre

sa÷lamaktadır. Bu Vk gerilimi de ùekil-4.9’daki tampon devre yardımıyla elde

edilir. Devrenin yapısı ùekil-4.11’de yeniden çizilmiútir. Bu devrenin giriú çıkıú

ba÷ıntısı

I1

K 2 (VCC Vc VTp ) 2

I1

K1 (V1 VS VTn ) 2

I2

K 3 (VCC V X VTp )

I1 I 2

(a)

(b)

2

I SS

(c)

(d)

(4.61)

denklemleri yardımıyla çıkartılabilir.

4.23

VCC

T2

+V

c

Vx

I1

T3

I1

T1

+ V1

ISS

VSS

ùekil -4.11. Tampon Devre

(4.61a) ve (4.61.b) denklemlerinin ortak çözümünden VS gerilimi için

VS

V1 VTn K2

(V VC VTp )

K1 CC

(4.62)

bulunur. Görüldü÷ü üzere K1, K2, VTn, VCC, Vc ve VTp sabit de÷erleri için VS

gerilimi, giriú gerilimi olan V1 ile negatif bir Vk geriliminin toplamı úeklindedir.

Buna göre ACSP OTA için çıkarılmıú olan ve (4.46) da gösterilmiú olan e÷im

ifadesi yeniden

g m 2K (Vk VT )

(4.63)

biçiminde yazılacak olursa, bu denklemde Vk yerine

VK

VTn K2

V VC VTp

K1 CC

(4.64)

(4.65)

konarak ACSP OTA’nın e÷imi için

gm

E

ifadesi elde edilir.

E2

V VC VTp

E 1 CC

4.24

ACSP OTA için çıkıú katının oluúturulabilmesi, di÷er bir deyiúle

devrenin her iki kolundan akan akımların farkının alınması için, simetrik OTA

yapısında oldu÷u gibi, akım aynalarının kullanılması gerekir. Devre aslında

ùekil-4.9’daki devreye akım aynaları eklenmesi ile oluúmaktadır. Bu devrenin

çıkıú direnci hesaplanması halinde, elde edilecek sonucun simetrik OTA için

yapılmıú olan analizin verdi÷i sonuçla aynı olaca÷ı açıktır.

4.3. Çapraz ba÷lamalı OTA >11@

Çapraz ba÷lamalı OTA nın çalıúmasının temel prensipleri ùekil-4.12’ ye

bakılarak anlaúılabilir.

ùekil-4.12’de görüldü÷ü üzere TD1 ve TD2

tranzistorlarının kaynak uçlarından birer ba÷ımsız gerilim kayna÷ı çapraz olarak

ba÷lanmıútır. Her iki tranzistorun da doymada çalıútı÷ı kabul edilerek

ID2

ID1

TD1

TD2

+V1

+

VGS 1

_

_

+

+Vb +VTh

+

_

+V2

+

_ VGS 2

+Vb+V Th

ùekil-4.12. Çapraz Ba÷lamalı OTA Temel Devresi

I D1

I D2

eúitlikleri yazılabilir.

olursa, bu akımın

E

(VGS1 VTh ) 2

2

E

( VGS 2 VTh ) 2

2

(4.66)

Fark akımı olan 'ID, 'ID=ID1-ID2 olarak tanımlanacak

4.25

'I D

I D1 I D2

VGS 2 ·

§V

E(VGS1 VGS 2 2VTh )¨ GS1

¸

©

¹

2

(4.67)

biçiminde ifade edilebilece÷i açıktır. (4.67) denklemindeki VGS1-VGS2 terimi

giriú fark terimi olarak düúünülecek olursa, (VGS1+VGS2-2Vth) teriminin sabit bir

gerilim de÷erine, örne÷in Vb gibi bir de÷ere eúit olması durumunda 3.3.2

denklemi lineer bir OTA karakteristi÷i özelli÷inde olur. Bu söylenenleri

gerçekleútiren devre yapısı ùekil-4.12’de gösterilmiútir. Bu durumda 'ID çıkıú

akım farkı

'I D 2 EVbVin

(4.68)

olur. (4.68) den kolayca görülebilece÷i gibi, OTA nın e÷imi 2EVb úeklinde Vb

gerilimiyle do÷ru orantılıdır.

Devre yapısı ùekil-4.13’de görülmektedir. øki koldan akan akımların

farkının alınması ve devrenin çıkıú katının oluúturulabilmesi üzere, simetrik

OTA ve ACSP OTA yapılarındakine benzer biçimde, akım aynalarının

kullanılması gerekir.

4.4 Krummenacher’in lineer CMOS OTA yapısı >8@

CMOS analog tümdevre tasarımında fark kuvvetlendiricilerin ve geçiú

iletkenli÷i kuvvetlendiricilerinin lineer çalıúma bölgesinin geniúli÷ini arttırmak

üzere yararlanılabilecek bir di÷er yöntem de, ùekil-4.14’de gösterilen fark

kuvvetlendirici yapısından yararlanmaktır.

ùekil-4.14’deki I1 ve I2 akımlarının farkının akım aynaları yardımıyla

alınması durumunda, bu fark kuvvetlendirici yapısı OTA olarak kullanılabilir.

Devredeki R direnci, kaynak ba÷lamalı kuvvetlendirici yapısında belirlenmiú

olan lineer çalıúma bölgesinin geniúli÷ini arttırmak üzere kullanılmıútır. ùekil

4.14’deki devrede T1 ve T2 tranzistorlarının bipolar npn tranzistor olarak da

gerçekleútirilmesi mümkündür. Bipolar tranzistorlardan oluúan bir emetör

ba÷lamalı kuvvetlendiricinin lineer çalıúma bölgesinin geniúli÷i VT= k.T/q ısıl

gerilimi mertebesindedir. Bu mertebedeki oldukça dar lineer çalıúma bölgesinin

4.26

+ VDD

+ VDD

I1

I2

I2

I1

IB

IB

ùekil-4.13. Çapraz Ba÷lamalı OTA

I2

I1

T1

Vi1

T2

Vi2

R

ISS

ISS

VSS

VSS

ùekil 4.14. Lineer OTA yapısı

geniúli÷ini arttırmak üzere, bipolar tranzistorlu fark kuvvetlendiricilerinde

ùekil-4.14’deki gibi bir lineerleútirme direnci kullanılır. CMOS kaynak

ba÷lamalı kuvvetlendirici yapısı için lineer çalıúma bölgesi

4.27

Viüst

2I SS

E

,

Vialt

2I SS

E

(4.69)

alt ve üst sınırları arasında yer alır. Bu sınırlar, ISS kutuplama akımına ve

tranzistorların E e÷im parametresine ba÷lıdır; bölgenin geniúli÷i bu

parametrelere verilecek de÷erlere ba÷lı olarak ayarlanabilir. Ancak lineer

çalıúma bölgesinin geniúli÷ini arttırmak için ISS akımının de÷erinin arttırılması

halinde, sürücü tranzistorların VGS gerilimlerinin büyümesi nedeniyle, ISS

akımını sa÷layan tranzistorun doymasız bölgeye girmesi sorununu ortaya

çıkarabilir. Aynı úekilde lineer çalıúma bölgesinin geniúli÷ini arttırmak için E

e÷im parametresinin de÷erinin küçültülmesi durumunda, OTA nın e÷imi

azalacaktır. Bütün bunlardan anlaúılaca÷ı gibi, OTA nın e÷imi ve lineer çalıúma

bölgesinin geniúli÷i arasında bir optimizasyon problemi bulunmaktadır.

ùekil-4.14’deki devrede R direncinin kullanılması ile oluúan devrenin

analizi yapılacak olursa, basit kaynak ba÷lamalı kuvvetlendirici yapısında

oldu÷u gibi, genel bir 'ID-'Vi geçiú fonksiyonu elde edilemeyece÷i kolayca fark

edilebilir. Bu tür bir inceleme, daha çok sayısal analiz ya da grafiksel

gösterilimler için yapılabilir.

ùekil-4.14’de verilen devredeki R direnci, CMOS analog tümdevre

teknolojisinde MOS tranzistorlarla gerçekleútirilir ve devre yapısı ùekil4.15’deki biçimi alır. Devredeki T3 ve T3c tranzistorlarının her ikisi de NMOS

tranzistordur.

ùekil-4.15’deki devrenin analizi yapılırken, V1=V2=0 için T1 ve T2

tranzistorlarının iletimde oldukları kabulü úartı altında

(V1 ! VS 1 ), (V1 VS 1 ! VTn ), (V2 ! VS 2 ), (V2 VS 2 ! VTn )

eúitsizliklerinin her biri ayrı ayrı sa÷lanmalıdır. Aynı úekilde V1>V2 olması

durumunda, VS1>VS2 oldu÷u gösterilebilir. T3 ve T3c tranzistorlarının V1 > V2

4.28

I2

I1

T1

T2

Vi2

Vi1

T3

T3'

ISS

ISS

VSS

VSS

ùekil-4.15. Direnç eúde÷eri ile lineer OTA Yapısı

koúulu altında hangi ucunun kaynak, hangi ucunun savak ucu oldu÷u ise

VS1>VS2 olmasından kolayca anlaúılabilir. Buna göre V1>V2 için T3

tranzistorunun savak ucu VS1 de, kaynak ucu VS2 geriliminde olmalıdır. V1>V2

ve V2>V1 için T3 ve T3c tranzistorlarının kaynak ve savak uçları ve bu durumdaki

gerilimleri

V1 ! V2

V2 ! V1

VGS 3

V1 VS 2

VGS 3'

V 2 VS 2

(a)

VS 1 VS 2

VDS 3( 3' )

VGS 3

V1 VS 1

VGS 3'

V 2 VS 1

VDS 3( 3' )

(b)

(4.70)

VS 2 VS 1

ba÷ıntılarıyla verilebilir.

T3 ve T3c tranzistorlarının doymada çalıútıkları bölgelerinin sınırları ise

V1>V2 iken T3 tranzistoru için

VS 1 VS 2 t V1 VS 2 VTn

(4.71)

’

olacaktır. M3 tranzistoru için aynı koúul

VS 1 VS 2 t V2 VS 2 VTn

úeklinde de gösterilebilir. ølgili ba÷ıntıların düzenlenmesi halinde

V1 VS 1 d VTn ,

V2 VS 1 d VTn

(4.72)

(4.73)

elde edilir. (4.73) eúitsizliklerine göre, T3 ve T3c tranzistorlarının doymada

çalıúması varsayımı altında, T1 tranzistoru kesimdedir. Bu, baúta yapılmıú olan

4.29

kabule ters düúmektedir. Bu durumda T3 ve T3c tranzistorlarının doymasız

bölgede çalıútıkları kabul edilebilir. Böylece

V1 V S 1 ! V Tn

(4.74)

yazılabilir. Doymasız bölgede çalıúan bir NMOS tranzistorun akım-gerilim

ba÷ıntısı

P n Cox

ID

VDS 2 º

Wª

« (VGS VT )VDS »

L¬

2 ¼

(4.75)

úeklindedir. K=Pn.Cox.(W/L) olarak tanımlanır ve ùekil-4.15’deki ID3 ve ID3’

akımları (4.75) ba÷ıntısı dikkate alınarak yazılacak olursa

I D3

ª

(VS 1 VS 2 ) 2 º

K« (V1 VS 2 VT )(VS 1 VS 2 ) »

2

¬

¼

I D 3'

ª

(VS 1 VS 2 ) 2 º

K« (V2 VS 2 VT )(VS 1 VS 2 ) »

2

¼

¬

(4.76)

elde edilir. ùekil-4.15’deki devreden I=ID3+ID3’olarak tanımlanırsa, bu durumda

I akımını veren ba÷ıntı

I

K > (V1 V2 2VS 2 2VT )(VS 1 VS 2 ) (VS 1 VS 2 ) 2 @

(4.77)

biçiminde yazılabilir. ùekil 3.4.2 den hareket edilirse

I 1 I I SS

0

I 2 I I SS

0

(4.78)

uyarınca 'ID=I1-I2=2I oldu÷u kolayca görülebilir. T1 ve T2 tranzistorlarının

iletimde ve doymada çalıúmaları durumunda, bunların sa÷layacakları akımgerilim iliúkisi

I1

K1 (V1 VS 1 VT ) 2

,

I2

K1 (V2 VS 2 VT ) 2

(4.79)

olur.

Buna göre 'ID=I1-I2 olarak tanımlanırsa, 'ID için , (4.79) denklemleri

yardımıyla

'I D I 1 I 2 K1 ('Vø VS 2 VS 1 )(V1 V2 VS 1 VS 2 2VT ) (4.80)

yazılabilir. Buna göre

'I D

2I

uyarınca, bu eúitlik (4.77) ve (4.80) eúitliklerinin yerine konulması ile

(4.81)

4.30

K > (V1 V2 2VS 2 2VT )(VS 1 VS 2 ) (VS 1 VS 2 ) 2 @

K1

('V VS 2 VS 1 )(V1 V2 VS 1 VS 2 2VT )

2

(4.82)

biçiminde yazılabilir. Denkleminin düzenlenmesi sonucunda VS1-VS2 gerilimi

için

VS 1 VS 2

K1 'V

2 K K1

(4.83)

ba÷ıntısı elde edilir. Benzer úekilde, (4.78) denklemlerinden hareketle

I1 I 2

2I SS

(4.84)

bulunur. Buna göre (4.79) daki I1 ve I2 ifadeleri ve (4.83) deki VS1-VS2 ifadeleri

yerine konursaVS1 ve VS2 gerilimleri için

VS 1

( K K1 )V1 KV2

(2 K K1 ) 2

K

2

VT r

'V I SS

2 K K1

2 K K1

2 K 2 K1

VS 2

( K K1 )V2 KV1

(2 K K1 ) 2

K

I SS

VT r

'V 2 2 K K1

2 K K1

2 K 2 K1

(4.85)

yazılabilir. Bu durumda 'ID akımı

2

'I D

§ 2KK1 'V ·

2K

r

'V ¨

¸ 2K1 I SS

2 K K1

© 2 K K1 ¹

(4.86)

olur. Burada a=1+E1/4E2, v=gm0. 'Vi/ISS, i='ID/ISS, gm0=w'ID/w'Vi olarak

tanımlanırsa i için

i

v2

v 1

4

(4.87)

gm0 için de

g m0

w' I D

w'Vi

'Vi 0

I SS

a (VGS VT ) M 1

(4.88)

yazılabilir. (4.87) den görülebilece÷i gibi, ùekil-4.15’deki devrede T3 ve T3c

tranzistorlarının doymasız çalıútıkları bölge içinde, kaynak ba÷lamalı

kuvvetlendirici yapısının akım-gerilim iliúkisine benzer bir iliúki elde edilece÷i

4.31

açıktır. Bu iliúkinin bozuldu÷u durum, T3 ya da T3c tranzistorunun doymasız

bölgeden çıkıp, doymalı bölgede çalıúması ile de÷iúir. Bu durum

g m0 'Vi

! V1

I SS

V

a 2 a 0.5

a 4 0.25

(4.89)

eúitsizli÷inin sa÷lanması durumunda gerçekleúir. 3.4.22 koúulu altında akımgerilim iliúkisi ise

i

> av

r

4a 2 r 4a 1 a 2 v 2

@

(4 a 1) 2

2

(4.90)

olacaktır. Buradaki artı-eksi iúareti, giriú geriliminin artı veya eksi olmasına göre

belirlenen iúarettir.

Çıkıú akımının maksimum de÷eri ise

v

g m0 'Vi

I SS

V2

4a 2

a

(4.91)

ba÷ıntısı yardımıyla hesaplanabilir.

KAYNAKLAR

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

H. Kuntman, Analog tümdevre tasarımı, Sistem yayınları, østanbul, 1992.

H. Kuntman, Analog MOS tümdevre tasarımı (Endüstri Semineri Notu), øTÜ øleri

Elektronik Teknolojileri Araútırma Geliútirme Vakfı (ETA), Uygulamaya özgü

tümdevre teknolojileri yaz okulu notları, østanbul,1993.

H. Kuntman, øleri analog tümdevre tasarımı: Analog devreler, (Endüstri Semineri

Notu), øTÜ øleri Elektronik Teknolojileri Araútırma Geliútirme Vakfı (ETA),

østanbul,1994.

P.R. Gray, R.G. Meyer, Analysis and design of analog integrated circuits, John

Wiley, 1984.

F. Riedel, MOS Analogtechnik, Oldenburg Verlag, Wien, 1988.

P.E. Allen and D.R. Holberg, CMOS analog circuit design, Holt, Rinehart and

Winston Inc., New York, 1987.

C.Acar, F.Anday, H. Kuntman, On the realization of OTA-C filters, Int. Journal

of Circuit Theory and Applications, Vol 21, pp.331-341, 1993.

F.Krummenacher, N. Joehl , A 4 MHz CMOS continuous-time filter on-chip

4.32

[9]

[10]

[11]

[12]

[13]

[14]

automatic tuning, IEEE J. Solid-State Circuits, Vol. 23, pp. 750-757,. 1988.

L. Ö÷düm, Aktif OTA-C filtrelerinde uygun OTA problemi, Yüksek Lisans

Tezi, øTÜ Fen Bilimleri Enstitüsü, 1995.

W. Sansen, Advanced Analog Design, Notes of Intensive Summer Course on

CMOS VLSI Design, Swiss Federal Institute of Technology, Lausanne, 1989.

E. Seevinck and R.W. Wassenaar, A versatile CMOS linear

transconductor/square-law function circuit’, IEEE J. Solid-State Circuits, Vol.

SC-22, pp. 366-377.

G. Wilson and P.K.Chan, Comparison of four transconductors for fully

integrated filter applications, IEE Proceedings, Pt-G, Vol. 138, No.6, pp.638688, 1991.

H. Kuntman, Simple and accurate nonlinear OTA macromodel for simulation of

CMOS OTA-C filters, Int. Journal of Electronics, 77, pp.993-1006, 1994.

L. Ö÷düm, H. Kuntman, Aktif OTA-C süzgeçlerinde uygun OTA problemi, IX.

Mühendislik Sempozyumu Bildiri Kitabı, Elektronik Mühendisli÷i, 71-76,

Süleyman Demirel Üniversitesi, Isparta, Mayıs 1996.