DENEY 21 IC Zamanlayıcı Devre

DENEYİN AMACI

1. IC zamanlayıcı NE555’in çalışmasını öğrenmek.

2. 555 multivibratörlerinin çalışma ve yapılarını öğrenmek.

3. IC zamanlayıcı anahtar devresi yapmak.

GİRİŞ

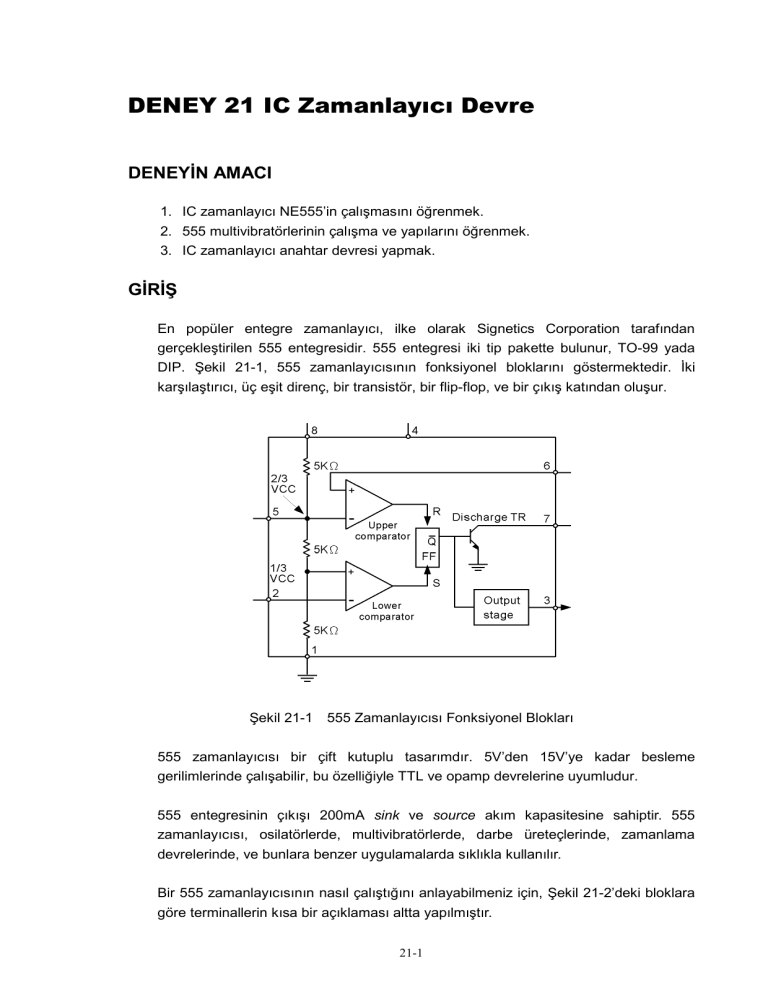

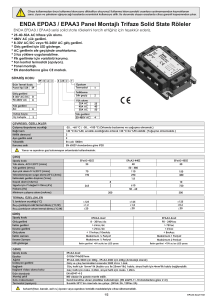

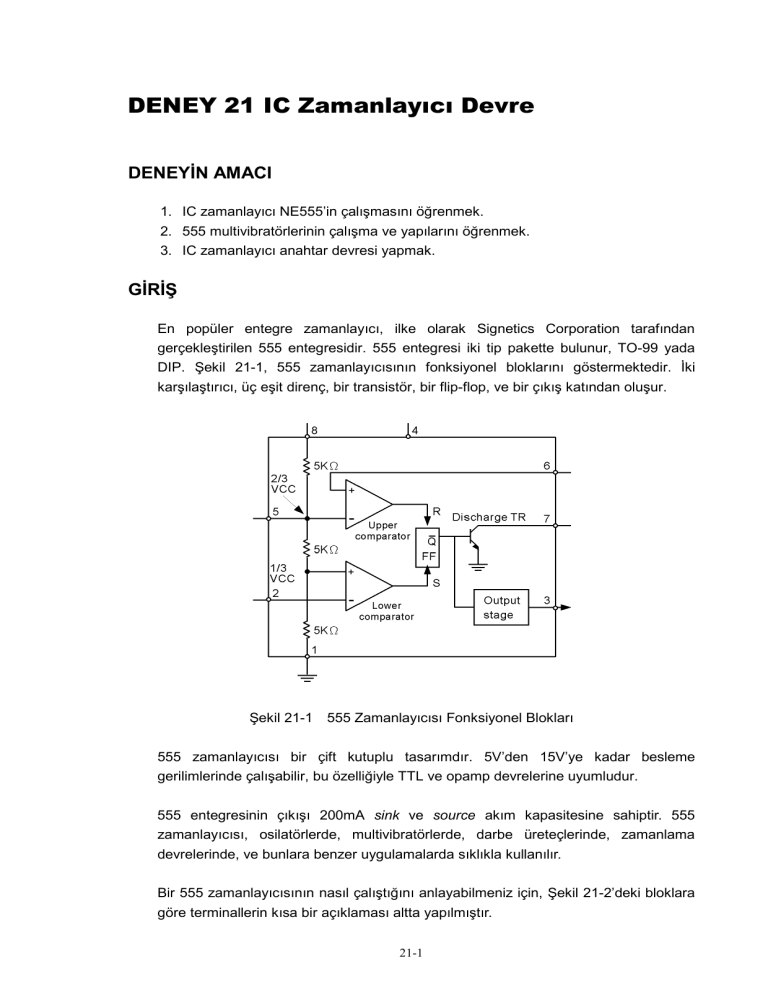

En popüler entegre zamanlayıcı, ilke olarak Signetics Corporation tarafından

gerçekleştirilen 555 entegresidir. 555 entegresi iki tip pakette bulunur, TO-99 yada

DIP. Şekil 21-1, 555 zamanlayıcısının fonksiyonel bloklarını göstermektedir. İki

karşılaştırıcı, üç eşit direnç, bir transistör, bir flip-flop, ve bir çıkış katından oluşur.

Şekil 21-1 555 Zamanlayıcısı Fonksiyonel Blokları

555 zamanlayıcısı bir çift kutuplu tasarımdır. 5V’den 15V’ye kadar besleme

gerilimlerinde çalışabilir, bu özelliğiyle TTL ve opamp devrelerine uyumludur.

555 entegresinin çıkışı 200mA sink ve source akım kapasitesine sahiptir. 555

zamanlayıcısı, osilatörlerde, multivibratörlerde, darbe üreteçlerinde, zamanlama

devrelerinde, ve bunlara benzer uygulamalarda sıklıkla kullanılır.

Bir 555 zamanlayıcısının nasıl çalıştığını anlayabilmeniz için, Şekil 21-2’deki bloklara

göre terminallerin kısa bir açıklaması altta yapılmıştır.

21-1

Şekil 21-2 555 Blok Anlatımı

Bu bloklardan, 555 zamanlayıcısının alttaki 5 kısımdan oluştuğunu görebiliriz.

1.

2.

3.

4.

5.

Karşılaştırıcı 2

Karşılaştırıcı 1

RS flip-flop

Deşarj transistörü

Çıkış tamponu

Her bir terminalin açıklaması altta anlatılmıştır:

1. RESET (pin 4): Reset terminali 555’in devre dışı kalmasına

ve tetikleme

girişindeki işaretlerden etkilenmemesine imkan sağlar. Eğer reset terminali

topraklanmışsa yada 0.4V’nin altında ise, çıkış ve deşarj terminallerinin ikisi de

yaklaşık olarak toprak potansiyelindedirler. Reset işlevi kullanılmayacaksa bu

terminal +VCC’ye bağlanmalıdır.

2. Tetikleme (pin 2): Tetikleme terminali gerilimi 2/3 VCC değerinden daha yüksekte

tutulursa, çıkış terminali gerilim seviyesi düşük olur. Büyüklüğü 1/3 VCC’nin altında

olan yeterli bir negatif darbe, çıkışın yüksek seviye olmasını sağlar. Tetikleme

terminali düşük seviyede tutulursa, çıkış terminali yüksek seviye durumunu korur.

3. Eşik (pin 6): Eğer bu terminaldeki gerilim 2/3 VCC’den daha büyükse, 555’in çıkışı

düşük seviyeye geçer. Kullanılmayacaksa, bu terminal genellikle +VCC’ye bağlanır.

21-2

4. Deşarj (pin 7): Deşarj terminali, çıkış düşük seviye olduğu sürece bir harici

zamanlama kapasitörünün deşarj olması için kullanılır. Çıkış yüksek seviye ise,

terminal açık devre gibi davranır ve harici direnç yada direnç ve kapasitör ile

belirlenen bir hızda kapasitörün dolmasına olanak sağlar.

5. Kontrol Gerilimi (pin 5): Kontrol gerilimi terminaline dışarıdan uygulanan gerilim,

eşik ve tetikleme gerilimlerini değiştirir. Kontrol gerilimi çıkış gerilimi dalga şekli

modülasyonu için de kullanılabilir. Güç kaynağından kaynaklanabilecek gürültüleri

ve/veya dalgacık gerilimlerinden entegreyi korumak için genellikle bu terminale

küçük bir filtre kapasitör bağlanır.

6. Çıkış (pin 3): Çıkış terminali sink ve source akım kapasitesi 200mA’dır. İki çıkış

seviyesine sahiptir, düşük ve yüksek.

Tek kararlı multivibratör ve astable multivibratör olmak üzere 555 zamanlayıcısının

iki çalışma modu vardır. Bir tek-kararlı multivibratör, tetiklemeli, darbe genişliği

ayarlanabilir bir darbe üreteci olarak düşünülebilir. İsminden anlaşılacağı gibi,

tek-kararlı multivibratör sadece bir durumda kararlıdır. Tetiklenerek bir süreliğine

diğer yarı kararlı durumuna geçer ve ardından tekrar başlangıç durumuna döner.

Şekil 21-3, 555 entegre zamanlayıcısı kullanılarak gerçekleştirilen bir tek-kararlı

multivibratörü gösterir. RS flip-flopu bir çift kararlı multivibratör olarak düşünülebilir.

Başlangıçta Q çıkışı düşük seviyede, Q çıkışı yüksek seviyededir. Flip-flopun S

girişine yüksek potansiyel uygulandığında Q çıkışı yüksek seviyeye, ve

Q çıkışı

düşük seviyeye geçer.

t0 anında, Q çıkışındaki yüksek seviye Q1 transistörünü iletime sürer. Böylece

C1 kapasitörü Q1 üzerinde boşalır. Bu sırada 555’in çıkışı düşük seviyedir.

Entegre içindeki 5KΩ’luk dirençler RA, RB ve RC, karşılaştırıcı girişlerinin referans

gerilimlerini belirleyen bir gerilim bölücü oluştururlar. Üstteki karşılaştırıcının

(COMP1) (-) girişinin referans gerilimi şöyle hesaplanır:

R A + RC

2

E1 = (VCC )

= (VCC ) ................................................................(21-1)

R A + RB + RC 3

Eşik terminaline uygulanan gerilim 2/3VCC’den büyükse, COMP1çıkışı yüksek

seviye olacaktır. Buna benzer olarak, alttaki karşılaştırıcının (COMP2) (+)

girişindeki gerilim şöyle hesaplanır:

RC

1

= (VCC ) ................................................................(21-2)

E 2 = (VCC )

R A + RB + RC 3

Tetikleme terminaline uygulanan gerilim 1/3VCC’nin altına düşerse, COMP2 çıkışı

yüksek seviyeye geçer.

t1 anında tetikleme terminaline bir negatif darbe uygulanırsa ve potansiyel

1/3VCC’den düşükse, COMP2 çıkışı yüksek seviyeye geçer ve RS flip-flopunun Q

21-3

çıkışını yüksek seviye yapar. Böylece 555 çıkışı yüksek seviye olur.

Q çıkışının

düşük seviye olması Q1 transistörünün kesime gitmesine neden olur. C1

kapasitörü R1 direnci üzerinden VCC değerine şarj olmaya başlar. Kapasitör

gerilimi 2/3VCC’ye ulaşınca, COMP1 çıkışı yüksek seviyeye geçer ve flip-flopu

reset yapar. Bunun sonucunda, t2 anında 555 çıkışı başlangıç durumuna (düşük

seviye) döner. Bir sonraki tetikleme darbesi uygulanana kadar çıkış terminali bu

düşük seviyede kalır.

Şekil 21-3 Tek-kararlı çalışmada 555

21-4

t1 ve t2 arasındaki zaman aralığı, çıkışın düşük seviyede kaldığı süredir, ve R1C1

zaman sabiti ile belirlenir.

T = (t2 - t1) = 1.1 R1 C1.................................................................................(21-3)

Burada T saniye, R1 ohm, ve C1 farad cinsindendir.

Şekil 21-3(c) tetikleme darbesi, kapasitör gerilimi, ve çıkış gerilimi dalga şekillerini

gösterir. T, C1 ve R1 arasındaki ilişki Şekil 21-3(d)’de 0.01~10.0 saniye zaman

aralığı için gösterilmiştir.

RESET özelliği kullanılmayacaksa, güç kaynağından kaynaklanacak gürültü ve

dalgacık gerilimi etkisini ortadan kaldırmak için RESET terminali VCC‘ye

bağlanmalıdır.

Bir astable (serbest çalışan) multivibratörün çalışması, kendi kendine tetiklenen bir

tek-kararlı multivibratör olarak düşünülebilir. İsminden de anlaşılacağı gibi astable

multivibratörün kararlı olduğu bir durum yoktur ve tek-kararlı multivibratörde

kullanılan tetikleme darbesine gerek yoktur. Şekil 2-14, astable çalışmada olan bir

555 entegre zamanlayıcısını gösterir. Başlangıçta, C1 kapasitörü R1 ve R2

üzerinden VCC değerine şarj olur. C1 kapasitörü şarj olurken, 555 çıkışı yüksek

seviyedir. Kapasitör gerilimi 2/3VCC’ye ulaşınca, COMP1 çıkışı Şekil 21-4(e)’de

gösterildiği gibi entegre çıkış geriliminin düşük seviyeye geçmesine ve Q1

transistörünün iletime geçmesine neden olur. Kapasitör R2 ve Q1 üzerinden deşarj

olur. Kapasitör gerilimi 1/3VCC’ye düşünce, COMP2 çıkışı entegre çıkışının

yüksek seviyeye geçmesine neden olur ve çevrim böylece devam eder. Şekil

21-4(c)’de gösterildiği gibi, C1 kapasitörü 1/3VCC’den 2/3VCC’ye gelene kadar

geçen süre boyunca çıkış yüksek seviyede kalır. Bu zaman aralığı şöyle

hesaplanır:

t1 = 0.693 (R1+R2) C1 .................................................................................(21-4)

C1 kapasitörü geriliminin 2/3VCC’den 1/3VCC’ye düşmesine kadar geçen süre

boyunca çıkış düşük seviyededir. Bu zaman aralığı ise şöyle hesaplanır:

t2 = 0.693 R2 C1 ..........................................................................................(21-5)

Toplam periyot, T;

T = t1 + t2 .....................................................................................................(21-6)

T = 0.693 (R1+2R2) C1 ................................................................................(21-7)

21-5

Şekil 21-4 Astable Çalışmada 555 Bağlantısı

Serbest çalışma osilasyon frekansı, F;

F = 1 / T ..........................................................................................................(21-8)

F=

1

.....................................................................................(21-9)

0.693( R1 + 2 R 2)C1

F=

1.44

...........................................................................................(21-10)

( R1 + 2 R 2)C1

21-6

Şekil 21-4(d), çeşitli (R1+R2) değerleri için Denklem (21-10)’un grafikleştirilmiş halidir,

bu grafik bir astable multivibratör tasarlamak için gerekli olacak direnç~kapasitör

kombinasyonlarını gösterir. Entegre çıkışının yüksek seviye olduğu zamanın (t1)

toplam periyoda (T) oranına çalışma oranı (Duty Cycle) denir. Şu şekilde gösterilir.

t1

R2

=

...................................................................................(21-11)

t1 + t 2 R1 + R 2

Şekil 21-5, 555 tek-kararlı multivibratörü tetikleme girişi için darbe üretecini gösterir.

DC =

S1 butonu, R3, R4 ve C3 elemanları kullanılarak, el yordamıyla bir tek giriş darbesi

sağlamak için bir tek-darbe üreteci oluşturulmuştur. S butonu açık devre iken tetikleme

terminalinin yüksek seviyede kalmasını garanti altına almak için VCC ile pin 2 arasına

R4 pull-up direnci yerleştirilir. S1 butonu kapalı devre yapıldığında, C3 kapasitörü

hızla deşarj olur ve pin2’de bir negatif darbe oluşur.

Şekil 21-5 Tetikleme darbesi üreteci

Deney Devresinin Açıklaması

Şekil 21-6 bu deneyde kullanılan devreyi gösterir. U2, NE555, bir zamanlama anahtarı

için bir tek-kararlı multivibratör olarak bağlanmıştır. Tetikleme girişine uygulanacak

tetikleme darbesi, CMOS Schmitt Evirici CD4093 ve S1 butonu ile üretilir.

Güç uygulanınca, C1 yüksek seviyeye şarj olur. U1 çıkışı (pin 4) kararlı bir yüksek

seviyedir, dolayısıyla U2’yi tetiklemek için değildir. U2 çıkışı düşük seviyede kalır,

böylece LED’ler sönük kalır.

S1’e basılınca, C1 hızla düşük seviyeye deşarj olur ve U1 çıkışı düşük seviyeye geçer.

U1 çıkışındaki seviye değişiklikleri tek-kararlı multivibratörü tetikler. U2 çıkışı yüksek

seviyeye geçerek Q1’i iletime sürer yada SCR’yi ON duruma geçirir. C3 kapasitörü R3

ve VR1 üzerinden VCC’ye şarj olur. Kapasitör gerilimi 2/3VCC’ye ulaşınca, U2 çıkışı

düşük seviyeye geçer, ve dolayısıyla Q1 ve SCR kesime giderler.

21-7

Şekil 21-6 Deney Devresi

Denklem (21-3) kullanılarak, U2 çıkışının yüksek seviyede kaldığı sure

T = 1.1 x (R3 + VR1) x C3 olarak hesaplanır. Bu denkleme göre, VR1 yada

kapasitörler (C3, C4 yada C5) değiştirilerek bu süre kolayca kontrol edilebilir.

U2 çıkışı, Q1 transistörünü yada SCR’yi kontrol etmek için kullanılabilir. Q1

kullanılırsa, bir yüksek seviye durumu Q1’i iletime geçirecektir ve LED’ler yanacaktır.

SCR kullanılırsa, U2 çıkışının yüksek seviye olması SCR’yi tetikleyecek, SCR de

röleyi enerjilendirecektir, böylece LED’ler yanacaktır. Eğer Q2 çıkışı düşük seviye

olursa, dalgalı dc kaynağın her yarım dalgasının sonunda SCR kesime gider.

KULLANILACAK ELEMANLAR

KL-51001 Güç Kaynağı Ünitesi

KL53010 Modülü

Multimetre

DENEYİN YAPILIŞI

1. KL-51001 güç kaynağı ünitesinin 12VDC ve 12VAC çıkışlarını KL-53010

modülüne bağlayın. Güç kaynağını açın.

2. Multimetreyi kullanarak, U1 çıkışındaki (pin 4) gerilimi ölçün ve kaydedin.

VO=_______________V. S1 butonuna basılı tutun, çıkış gerilimi ____________V.

S1 anahtarını bırakın, çıkış gerilimi _______________V.

21-8

3. VR1’i saat yönünün tersi yönde sonuna kadar çevirin. Bağlantı fişlerini 1, 4, 6, ve 7

numaralara takın. LED’in durumunu gözlemleyin ve kaydedin. ________________

Zamanlayıcı süresini hesaplayın.

T1 = (100K x 0.1µF) x 1.1 = _________________saniye.

4. S1’e bir kere basıp bırakın. LED’in yanık olduğu süreyi ölçün ve kaydedin.

T1 = _______________saniye.

Hesapladığınız T1 değer ile ölçtüğünüz T1 değeri uyuşuyor mu?

______________________________________________________________

5. VR1’i saat yönünde sonuna kadar çevirin. Zamanlayıcı süresini hesaplayın.

T2 = 1.1 x (100K + 1M) x 0.1µF = ______________________________saniye.

6. 4. adımı tekrarlayın. T2 ____________________ saniye.

Ölçülen T2 değeri ile hesaplanan T2 değeri uyuşuyor mu?

______________________________________________________________

7. Bağlantı fişini 4 numaradan çıkarın ve 3 numaraya takın. VR1’i saat yönünün tersi

yönde sonuna kadar çevirin. Zamanlayıcı süresini hesaplayın.

T1 = 1.1 x (100K x 10µF) = _____________________saniye.

8. 4. adımı tekrarlayın. T1_____________________saniye.

Ölçülen T1 değeri ile hesaplanan T1 değeri uyuşuyor mu?

______________________________________________________________

9. VR1’i saat yönünde sonuna kadar çevirin. Zamanlayıcı süresini hesaplayın.

T2 = 1.1 x (100K x 1M) x 10µF = _____________________saniye.

10. 4. adımı tekrarlayın. T2 ____________________ saniye.

Ölçülen T2 değeri ile hesaplanan T2 değeri uyuşuyor mu?

______________________________________________________________

11. Bağlantı fişini 3 numaradan çıkarın ve 2 numaraya takın. VR1’i saat yönünün tersi

yönde sonuna kadar çevirin. Zamanlayıcı süresini hesaplayın.

T1 = 1.1 x (100K x 22µF) = _____________________saniye.

12. 4. adımı tekrarlayın. T1_____________________saniye.

Ölçülen T1 değeri ile hesaplanan T1 değeri uyuşuyor mu?

______________________________________________________________

13. VR1’i saat yönünde sonuna kadar çevirin. Zamanlayıcı süresini hesaplayın.

T2 = 1.1 x (100K x 1M) x 22µF = _____________________saniye.

21-9

14. 4. adımı tekrarlayın. T2 ____________________ saniye.

Ölçülen T2 değeri ile hesaplanan T2 değeri uyuşuyor mu?

______________________________________________________________

15. Bağlantı fişlerini 1, 3, 5 , ve 8 numaralara takın.

16. VR1’i saat yönünün tersi yönde sonuna kadar çevirin S1’e bir kere basıp bırakın.

LED yanıyor mu? _________________________________________________

Röle çalıştı mı? ___________________________________________________

17. Zaman dolunca, LED sönüyor mu neden?

______________________________________________________________

______________________________________________________________

SONUÇ

Bu deneyde, VR1 yada kapasitörler değiştirilerek istenen zaman aralığının elde

edilebileceğini öğrendik.

(1) T1 = 1.1 x R3 x C5 = 0.011 saniye.

T2 = 1.1 x (R3 + VR1) x C5 = 0.121 saniye.

(2) T1 = 1.1 x R3 x C4 = 1.1 saniye.

T2 = 1.1 x (R3 + VR1) x C4 = 12.1 saniye.

(3) T1 = 1.1 x R3 x C3 = 2.42 saniye.

T2 = 1.1 x (R3 + VR1) x C3 = 26.62 saniye.

UJT, PUT, ve SCS gibi birçok yarıiletken eleman, zamanlayıcı anahtar olarak

kullanılabilir, ancak IC 555 zamanlayıcısı daha uygun ve düşük maliyetlidir.

21-10