Bölüm 7

Bu ve bundan sonraki bölümde, makine komutlarını işleten ve diğer birimlerin faaliyetlerini

düzenleyen işlem birimi üzerine yoğunlaşacağız. Bu birim genellikle Komut Seti Mimarisi

(Instruction Set Architecture - ISA) ya da kısaca işlemci olarak adlandırılır. Dahili yapısını ve

bir programın komutlarını alıp getirme (fecthing), çözme (decoding) ve işletme (execution)

görevlerini nasıl yerine getirdiğini inceleyeceğiz. İşlem birimi merkezi işlem birimi olarak da

bilinir. Buradaki “merkezi” terimini kullanmak günümüzde pek uygun değildir, çünkü

modern bilgisayar sistemleri çok sayıda işlem birimine sahiptir.

İşlemcilerin organizasyonu, yıllar içinde teknolojide yaşanan gelişmeler ve diğer

taraftan performansa olan ihtiyaç sayesinde oldukça gelişti. Yüksek performanslı işlemcilerin

geliştirilmesindeki yaygın bir stratejiye göre çeşitli fonksiyonları yerine getiren birimler

mümkün olduğunca paralel bir şekilde çalışmalıdır. Yüksek performanslı işlemciler ardışık

(pipelined) bir organizasyona sahiptir. Bir komutun işletilmesine önceki komutun işletilmesi

bitmeden önce başlanır. Süper skalar işletim adı verilen bir başka yaklaşıma göre, aynı anda

çok sayıda komut getirilip işletilir. Bu bölümde tüm işlemcilerde yaygın olan temel fikirler

üzerinde yoğunlaşacağız.

Tipik bir hesaplama

görevi (computing task), bir programı oluşturan makine

komutları dizisi tarafından belitilmiş olan adımlardan oluşur. Bir komut, bir dizi temel

işletimin (operation) gerçekleştirilmesiyle işletilir. Bu işletimler ve nasıl kontrol edildikleri bu

bölümün temel konusudur.

7.1 Bazı Temel Konseptler

Bir program işletmek için, işlemci birim zamanda bir komut getirir ve belirtilen işlemi

uygular. Komutlar, bir dallanma veya bir atlama komutuna rastlayana kadar ardışık hafıza

alanlarından getirilir. İşlemci , program sayacını (Program Counter - PC) kullanarak,

getirilecek bir sonraki komutu içeren hafıza alanının adresini saklar. Bir komutu getirdikten

sonra, PC’nin içeriği dizideki bir sonraki komutu gösterecek şekilde güncellenir. Bir dallanma

komutu PC’ye farklı bir değer yükleyebilir.

İşlemcideki bir başka anahtar yazmaç ise komut yazmacıdır (Instruction Register - IR).

Her bir komutun 4 bayttan meydana geldiğini ve tek hafıza wordünde depolandığını

varsayalım. Bir komutu işletebilmek için, işlemci aşağıdaki adımları uygulamalıdır:

1. PC tarafından gösterilen hafıza alanının içeriğini getir. Bu alanın içeriği işletilecek bir

komut olarak yorumlanır. Bu nedenle bu içerik IR’ye yüklenir. Bu durum sembolik

olarak aşağıdaki gibi ifade edilebilir:

IR ← [[PC]]

2. Hafızanın bayt adreslenebilir olduğunu varsayarak, PC’nin içeriğini 4 arttır. Yani:

PC ← [PC] + 4

3. IR’deki komut tarafından belirtilen faaliyetleri yerine getir.

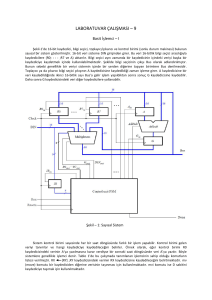

Şekil 7.1 İşlemci içindeki tek yollu veriyolu organizasyonu

Bir komutun bir wordden fazla yer kaplaması durumunda 1. ve 2. adımlar tüm komutun

getirilebilmesi için gerektiği kadar tekrarlanmalıdır. Bu iki adım genellikle getirme evresi

(fetch phase), 3. adım ise işletme evresi (execution phase) olarak adlandırılır. Bu işletimleri

detaylı inceleyebilmek için işlemcinin dahili organizasyonunu incelememiz gerekir. Bir

işlemcinin temel yapı taşları Şekil 1.2’de gösterilmektedir. Bunlar organize edilebilir ve çeşitli

yollarla birbirine bağlanabilir haldedir. Çok basit bir organizasyonla başlayacağız. Bu

bölümün ilerleyen kısımlarında ve Bölüm 8’de yüksek performans sağlayan karmaşık yapıları

göreceğiz. Şekil 7.1’deki organizasyonda aritmetik ve mantık birimi ALU ve tüm yazmaçlar

tek ortak veriyoluyla birbirine bağlanmış halde görülüyor. Bu veriyolu işlemcinin içindedir ve

işlemci, hafıza ve G/Ç aygıtlarını birbirine bağlayan harici veriyolu ile karıştırılmamalıdır.

Şekil 7.1’de görüldüğü gibi, harici hafıza veriyolunun veri ve adres çizgileri, sırasıyla

hafıza veri yazmacı (memory data register - MDR) ve hafıza adresi yazmacıyla (memory

adress register - MAR) dahili işlemci veriyoluna bağlanıyor. MDR yazmacı iki girişe ve iki

çıkışa sahiptir. Veri MDR’a hafıza veriyolundan veya dahiliişlemci veriyolundan yüklenebilir.

MDR’da depolanan veri her iki veriyolu üzerinde de yer alabilir. MAR’ın girişi dahili

veriyoluna, çıkışı da harici veriyoluna bağlıdır. Hafıza veriyolunun kontrol çizgileri komut

şifre çözücüsüne ve kontrol mantık bloğuna bağlıdır. Bu birimin görevi, işlemci içindeki tüm

birimlerin faaliyetini kontrol eden sinyalleri dağıtmak ve hafıza veriyoluyla iletişim

sağlamaktır. R0’dan R(n-1)’e kadar olan işlemci yazmaçlarının sayısı ve kullanım şekli

işlemciden işlemciye değişir. Yazmaçlar programcılar tarafından genel amaçlı kullanım için

oluşturulabilir. Bazıları dizin yazmaçları ya da yığın yazmaçları gibi özel amaçlı yazmaçlar

olabilir. Şekil 7.1’deki üç yazmaç Y, Z ve TEMP’den daha önce bahsedilmemişti. Bu

yazmaçlar programcıya saydamdır, yani programcının bu yazmaçlarla uğraşmasına gerek

yoktur, çünkü bunlar herhangi bir komut tarafından referans gösterilemezler. Bazı komutların

işletimi esnasında geçici depolama için işlemci tarafından kullanılırlar. Bu yazmaçlar, bir

komutun bir başka komutun kullanımı için oluşturduğu veriyi depolamak için hiçbir zaman

kullanılmaz.

Çoklayıcı MUX, ALU’nun A girişi olmak için Y yazmacının çıkışını ya da 4 sabit

değerini seçer. 4 sabiti PC’nin içeriğini arttırmak amacıyla kullanılır. MUX kontrol

girişindeki Select iki değer alabilir: 4 sabitini seçebilmek için Select4 veya Y yazmacını

seçebilmek için SelectY.

Bir komut işletimi ilerlerken, veri bir yazmaçtan diğerine aktarılır, genellikle de bazı

aritmetik ve mantık işlemlerini yapabilmek için ALU üzerinden geçer. Komut şifre çözücü

(instruction decoder) ve kontrol mantık birimi (control logic unit), IR yazmacında bulunan

komut tarafından belirtilen görevleri yapmakla yükümlüdür. Şifre çözücü, yazmaçları seçmek

için gerekli kontrol sinyallerini üretir ve verinin aktarımını yönlendirir. Yazmaçlar, ALU ve

bunları birbirine bağlayan veriyolu datapath – veriyolu olarak adlandırılır.

Şekil 7.2 Şekil 7.1’deki yazmaçlar için giriş ve çıkış kapıları

Bazı olağanüstü durumlarda, bir komut aşağıdaki işlemleri belirli bir düzende 1 ya da

daha fazla sayıda uygulamalıdır:

•

Bir işlemci yazmacından diğerine ya da ALU’ya 1 word boyutunda veri aktar.

•

Bir aritmetik veya bir mantık işlemi uygula ve sonucu işlemci yazmacında depola.

•

Verilen bir hafıza alanının içeriğini getir ve işlemci yazmacına yükle.

•

Bir işlemci yazmacındaki 1 word boyutunda veriyi verilen bir hafıza alanında depola.

Şimdi ise Şekil 7.1’deki basit işlemci modelini kullanarak bu işlemlerin her birinin nasıl

uygulandığını inceleyeceğiz.

7.1.1 Yazmaç Aktarımı

Komut işletimi, verinin bir yazmaçtan diğerine aktarıldığı durumlarda bir dizi adımdan oluşur.

Her yazmaç için, yazmacın içeriğini veriyoluna yerleştirmek veya veriyolundaki veriyi

yazmaca yüklemek için iki kontrol sinyali kullanılır. Bu durum Şekil 7.2’de sembolik olarak

gösterilmiştir. Ri yazmacının giriş ve çıkışları Riin ve Riout sinyallerinin kontrol ettiği

anahtarlarla veriyoluna bağlıdır. Riin 1’e eşitlendiğinde, veriyolundaki veri Ri’ye yüklenir.

Benzer bir şekilde, Riout 1’e eşitlendiğinde Ri yazmacının içeriği veriyoluna yerleştirilir. Riout

0’a eşit olduğunda, veriyolu diğer yazmaçlardan veri aktarmak için kullanılır.

R1 yazmacının içeriğini R4 yazmacına aktarmak istediğimizi varsayalım. Bunu

gerçekleştirmek için aşağıdaki işlemleri yapmalıyız:

• R1out 1’e eşitlenerek R1 yazmacının çıkışı aktif hale getirilir. Böylece R1’in içeriği

işlemci veriyoluna yerleştirilir.

• R4in 1’e eşitlenerek R4 yazmacının girişi aktif hale getirilir. Böylece veri veriolundan

R4’e taşınır.

İşlemci içindeki tüm işlemler ve veri aktarımı işlemci saati (processor clock) tarafından

belirlenen zaman dilimlerinde gerçekleştirilir. Belirli bir aktarımı yöneten kontrol sinyalleri

saat çevriminin (clock cycle) başında öne sürülür. Örneğimizde R1out ve R4in 1’e eşitleniyor.

Yazmaçlar kenar-tetikli (edge-triggered) flip-floplardan meydana gelir. Bundan dolayı, saatin

bir sonraki etkin kenarında, R4’ü oluşturan flip-floplar girişlerinde bulunan veriyi yüklerler.

Ancak çalışan farklı planların da olması mümkündür. Örneğin, veri aktarımı saatin yükselen

ve alçalan kenarlarını kullanabilir. Eğer kenar-tetikli flip-floplar kullanılmazsa, iki veya daha

çok saat sinyali düzgün veri aktarımını garanti etmelidir. Buna çok fazlı saatle denetim

(multiphase clocking) denir.

Örnek olarak Şekil 7.3’de Ri yazmacının bir biti için uygulama gösterilmektedir. İki girişli

bir çoklayıcı (multiplexer) kenar-tetikli flip-flopun girişine uygulanan veriyi seçmek için

kullanılır. Riin kontrol girişi 1’e eşitlendiğinde, çoklayıcı veriyolundaki veriyi seçer. Bu veri

saatin yükselen kenarındaki flip-flopa yüklenir. Riin 0’a eşitlendiğinde, çoklayıcı o an flipflopta depolanan değeri karşılık verir.

Flip-flopun Q çıkışı üç durumlu bir geçitle veriyoluna bağlıdır. Riout 0’a eşit olduğunda

geçidin çıkışı yüksek empedanslı (elektrik olarak bağlı olmayan) bir durumdadır. Bu da bir

anahtarın açık devre (open-circuit) durumuna karşılık gelir.

Şekil 7.3 Tek yazmaç biti için giriş ve çıkış kapıları

Şekil 7.4 MDR yazmacı için bağlantı ve kontrol sinyalleri

Şekil 7.5 Hafıza Read komutu için zaman değerleri